Time Constrained Test Scheduling

On this page, we first give the problem formulation. Next we introduce fault coverage and system test quality STQ and finally the algorithms used in the experiments will be presented.

Problem Formulation

In our work, the problem is to:

- For a given TAM width Wtam with a constraint on the maximum number of TAM's to use k, we want to find the number of TAM's and their widths;

- For each core i select the number of test vectors stvi

- Assign the selected test vectors for each core i to the designed TAM's.

This needs to be done in such a way that the test application time for the system meets the time constraint Tmax given by the memory depth in the ATE (automatic test equipment) and the test quality in the system is maximized.

Fault Coverage

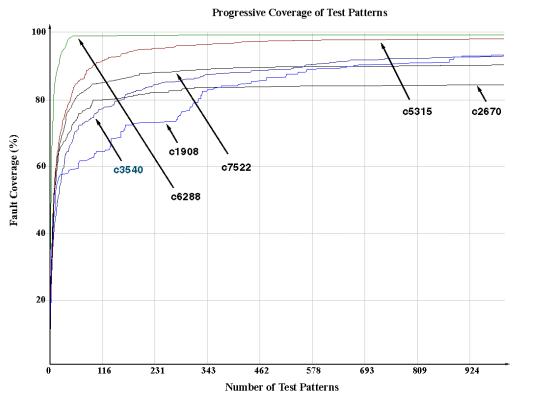

By fault coverage, we mean how many percent of the possible faults that are checked by applying a set of test vectors. Initially, when no test vectors are applied, no faults are detected. As the test stimuli is applied the covered faults in the design, the fault coverage, increases. Figure 1 shows the fault coverage for a set of ISCAS benchmarks.

Figure 1 Fault coverage versus the number of applied test vectors

By examining Figure 1, the following observation can be made: the curves have exponential behaviour, see Figure 2.

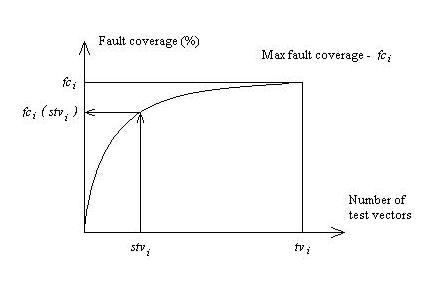

Figure 2 Fault coverage versus the number of test vectors

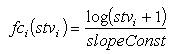

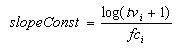

We therefore assume that the fault coverage after applying stvi test vectors for core i can be estimated to:

where slopeConst is given as follows:

where fci is the maximal fault coverage achieved when all tvi vectors are applied and the +1 is used to adjust the curve so it passes the origin.

System Test Quality

In order to meet the time constraint, the number of test vectors need to be reduced. This reduction have to be done in such a way that the quality of the test is maximized. To find the schedule with the highest probability to find a defect in the system, we need to introduce a way to meassure the test quality.

We assume that the the quality of a set of test vectors can be determined by:

- fault coverage fci

- defect probability dpi

- number of selected test vectors stvi

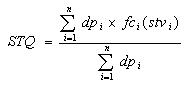

We introduce the system test quality STQ:

Time Constraint Test Scheduling without Test Vector Selection

In this section, we describe a time constrained sequential test scheduling algorithm based on test ordering, where the time constraint is caused by the limited memory in the ATE. In this approach, we assume a TAM architecture where all cores are assigned to the entire TAM. During testing, the cores are multiplexed such that the all cores are tested in a sequence.

In this approach, we first order the cores by using one of the three sorting techniques listed below.

Sorting when not considering defect probability and fault coverage. In this technique, the cores are sorted in ascending order according to defect probability.

Sorting when considering defect probability but not fault coverage. In this technique, the cores are sorted in descending order according to defect probability.

Sorting when considering defect probability together with fault coverage. In this technique, we make use of the STQ equation in order to find a value of the test quality for each core. The cores are then sorted in descending order according to test quality per clock cycle.

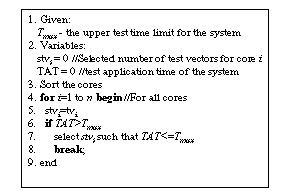

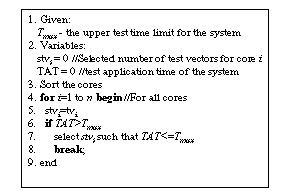

After the ordering, we run all available tests at as many cores as possible until we reach the time limit. When a core finally exceeds the limit when we run all available tests, we schedule as many tests as possible without exceeding the maximum test time. The algorithm for our test scheduling technique is described in Figure 3.

Figure 3 Sequential test scheduling without test vector selection

The benefit with this approach is that it is simple, but if a very short test time is available only a small part of the cores in the system is tested which will result in a large decrease of test quality.

Time Constraint Test Scheduling and Test Vector Selection

In this section we describe a time-constrained test vector selection and test scheduling technique.

We are assuming a TAM architecture where the TAM wires are grouped into several TAMs [13] and the cores connected to the same TAM are tested sequentially.

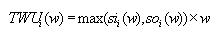

For a given value of the maximum number of TAMs k, our algorithm finds the number of TAMs, the TAM widths, the assignment of the cores and the assignment of the test vectors that maximizes test quality STQ. Given a set of TAM's, we need to find the TAM width to assign a core i to minimize the waste of the TAM width. For each core i, we therefore introduce TWUi (TAM width utilization) for a given TAM width w:

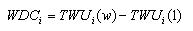

If the TAM width is equal to 1, the wrapper scan-in chain and the wrapper scan-out chain are perfectly balanced. In order to measure the cost of the wrapper design, we measure how much this design differ from the balanced case. To decide how balanced a wrapper design is at acertain TAM width w, we therefore introduce the wrapper design cost WDC:

In our approach, we assume that each core i is assigned to the TAM with a width w that will give the least contribution to WDC. During test scheduling, we are always doing the assignment of test vectors to the core that will increase the STQ per clock cycle at most. If this assignment is impossible due to exceeding of the total available test time at one of the TAMs, we consider the scheduling to be finished for this TAM and continue to select the best option that do not exceed the time limit for the remaining TAMs. We continue like this until test scheduling is finished for all TAMs. Since we want to find the solution with best value of STQ, we run the algorithm described above for every possible set of TAM widths. The algorithm for our test scheduling technique is outlined in Figure 4.

Figure 4 Test scheduling and test vector selection algorithm.

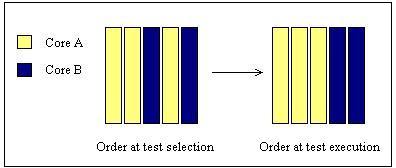

It is important to realize that there is a difference between the order the test vectors are selected and in the actual execution order. Our algorithm may select and assign the test vectors in one order, but when it comes to execution all selected vectors for each core are always executed in a sequence. In Figure 5, we illustrate the difference between selection order and execution order by considering test vectors from two different cores.

Figure 5 Test selection order versus test execution order