# Outline

Control unit

LiU

- Input/Output Devices and System Buses

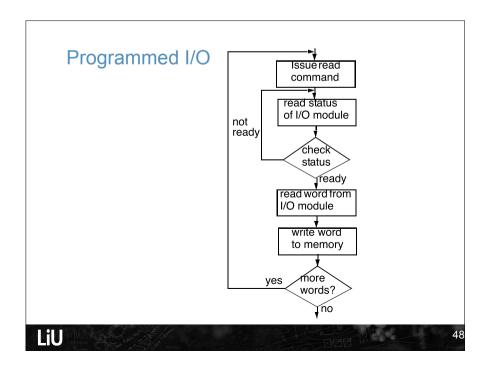

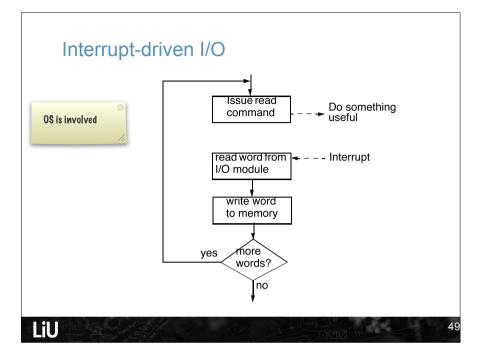

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

103 pe 201 her 103 her 2

RISC and CISC

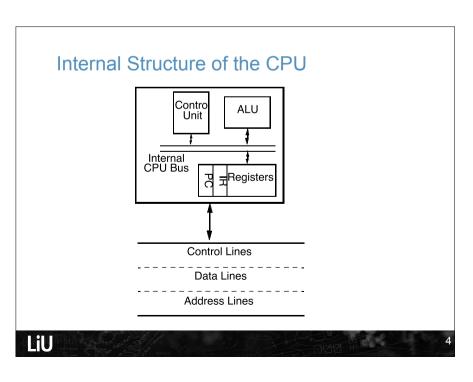

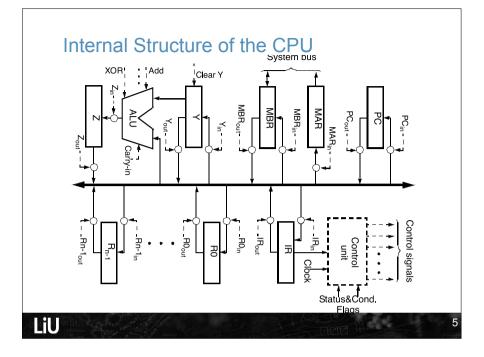

#### Internal Structure of the CPU

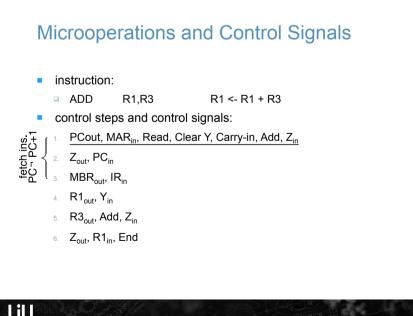

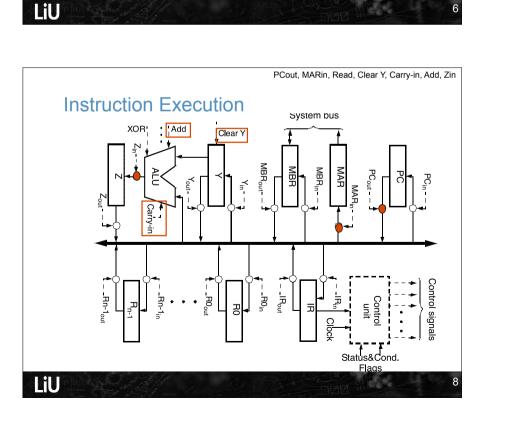

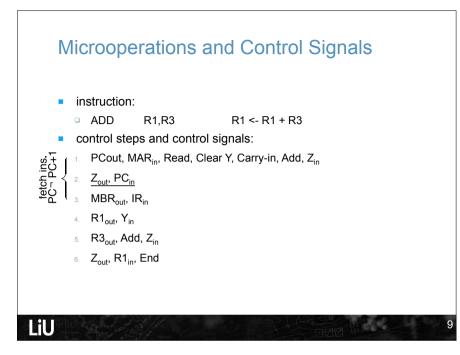

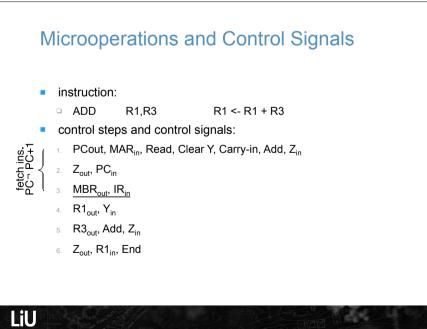

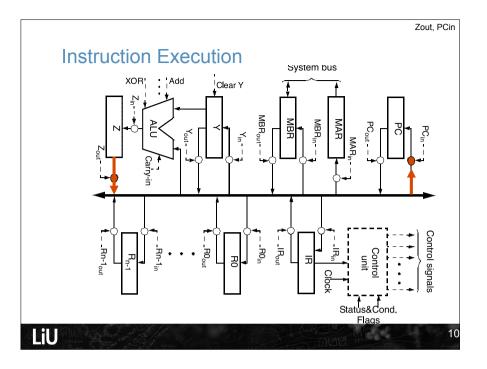

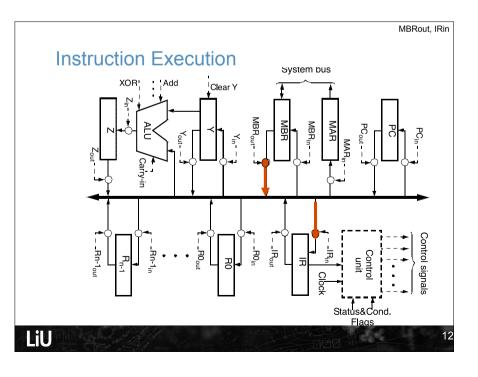

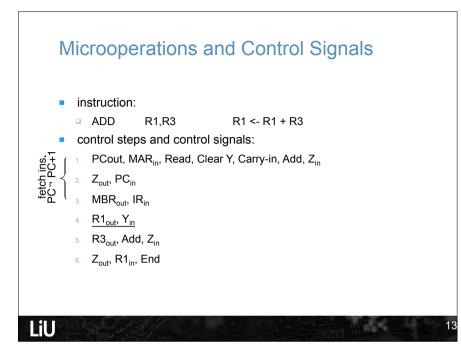

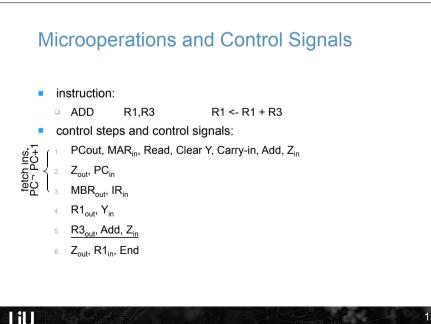

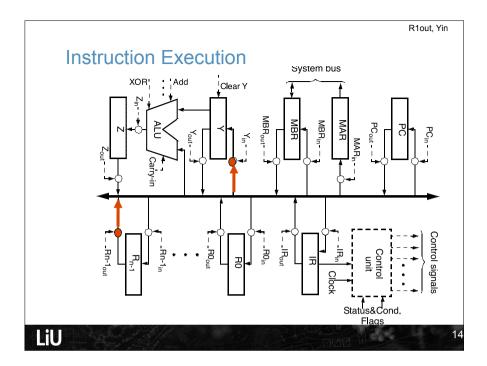

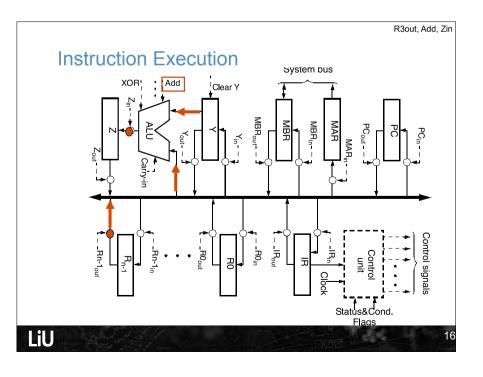

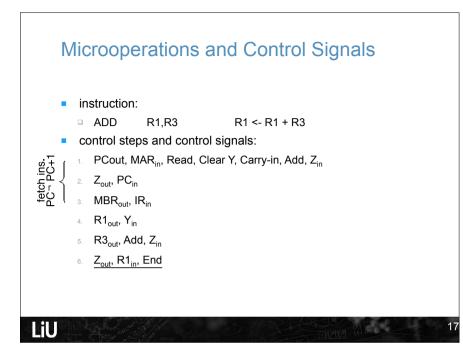

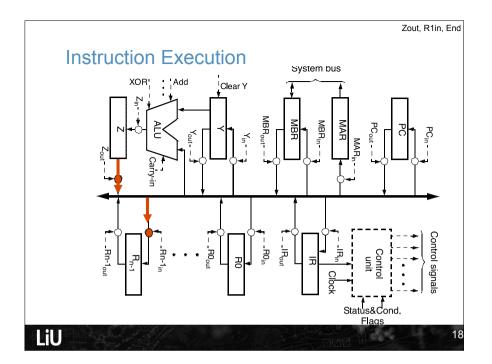

- The CPU executes an instruction as a sequence of control steps. In each control step one or several microoperations are executed.

- Execution of a microoperation, one or several control signals have to be issued:

- a) signals for transferring content of register R0 to R1: R0out, R1in

- b) signals for adding content of Y to that of R0 (result in Z): R0out, Add, Zin

- c) signals for reading a memory location; address in R3: . R3out, MARin, Read

- One clock pulse triggers the activities corresponding to one control step -> for each clock pulse the control unit generates the control signals corresponding to the microoperations to be executed in the respective control step.

100

#### RISC and CISC

# Summary

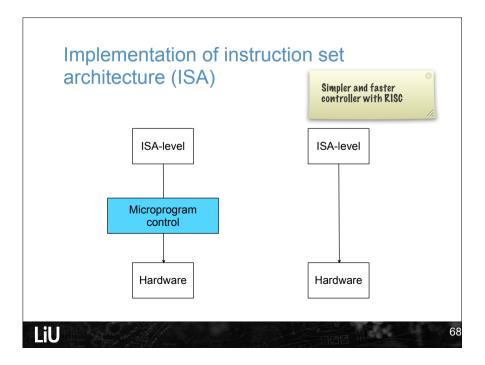

- The control unit coordinates the CPU by issuing in each clock cycle the appropriate control signals.

- Control signals activates the microoperations

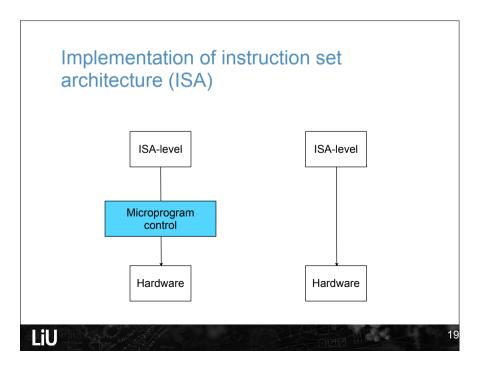

- Control units can be hardwired or microprogrammed.

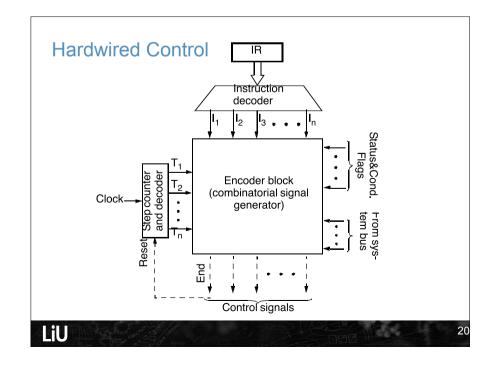

- A hardwired control unit is a combinatorial circuit

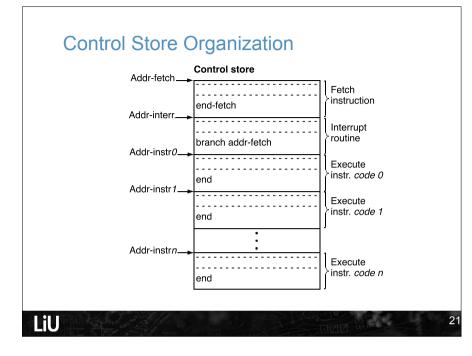

- A microprogrammed control unit is implemented like another CPU inside the CPU.

22

- Hardwired controllers are faster than microprogrammed.

- Microprogrammed controllers can implement advanced instructions

# System Buses

- A bus 50-100 separate lines/wires

- Classified into three functional groups:

- Data lines: moving data between system components.

- Address lines: are used to designate the source or destination of data.

- Control lines: are used to control bus access, synchronize operations, and to propagate commands throughout the system.

28

- In order to avoid large buses -> multiplexed bus.

- Multiplexed bus:

- Advantage: Bus width can be reduced

- Disadvantage: The system becomes slower

#### **Bus Arbitration**

- Devices connected to a bus can be of two kinds:

- Master: is active and can initiate a bus transfer.

- Slave: is passive and waits for requests.

- Some devices can act both as master and as slave, depending on the circumstances:

- CPU is typically a master.

- A coprocessor, however, can initiate a transfer of a parameter from the CPU -> CPU acts like a slave.

- An I/O device usually acts like a slave in interaction with the CPU.

- Several devices can perform direct access to the memory, in which case they access the bus like a master.

100

The memory acts only like a slave.

#### LiU

#### Bus Timing

- Timing refers to the way in which events are coordinated on the bus:

- Synchronous timing: the occurrence of events on the bus is determined by a clock.

- Asynchronous timing: the occurrence of one event on a bus follows and depends on the occurrence of a previous event.

- Examples:

- PCI and ISA buses use synchronous timing.

- SCSI buses use asynchronous timing.

### **Bus Arbitration**

- Since only one unit at a time can transmit over the bus, arbitration is needed.

- Arbitration mechanisms:

- Centralized arbitration: there is a single device, the bus arbiter, that determines who goes next.

- Decentralized (distributed) arbitration: no arbiter is needed.

- Examples:

LiU

- PCI and ISA buses use a centralized arbitration scheme.

- SCSI buses use a decentralized scheme.

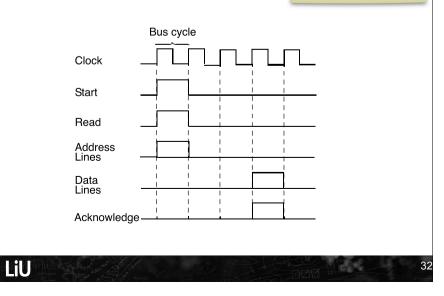

# Synchronous Timing

Adopt to slowest device Easy to design

# Synchronous Timing

- The bus includes a clock line: all devices on the bus can read the clock line.

- All events on the bus start at the beginning of a clock cycle.

- A bus sequence for a synchronous memory read.

- The CPU (master) issues a start signal to mark the presence of address and control information on the bus: the read signal is issued on the respective control line, and the memory address is placed on the address lines.

- After a delay of two bus cycles, the memory (slave) places the data on the data lines and issues an acknowledge signal on the respective control line.

100

Adopt to slowest device. Easy to design

# LiU

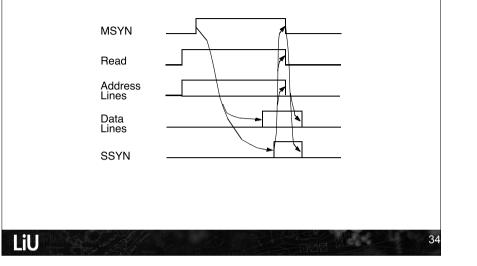

#### Asynchronous Timing There is no clock line on the bus. . Each event is caused by a prior event, not by the clock pulse. The master will wait exactly as much as is needed for the slave to finish. If a master has to wait long for a certain slow slave, this does not influence how much it will have to wait for. A bus sequence for an asynchronous memory read. 1. CPU (master) asserted the address lines and issue read signal 2 wait until lines are stable and then issue MSYN signal (Master SYNchronization). 3. memory (slave) sees the MSYN, performs the work and asserts the SSYN (Slave SYNchronization) signal. 4 When the master has noticed the SSYN, it knows that data is on the lines and latches LiU

# Asynchronous Timing

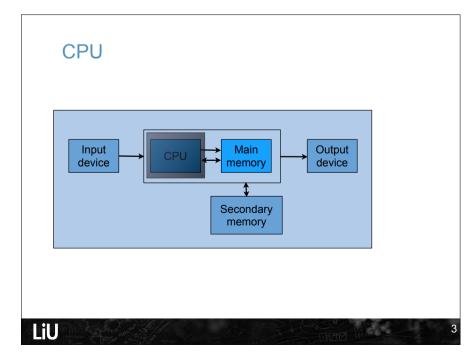

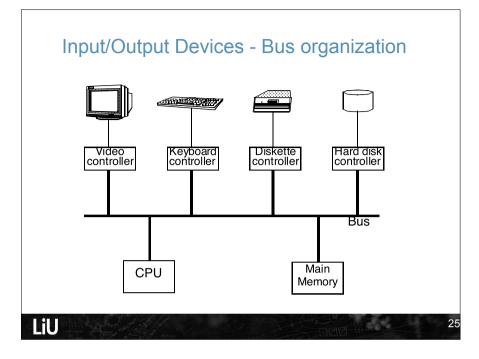

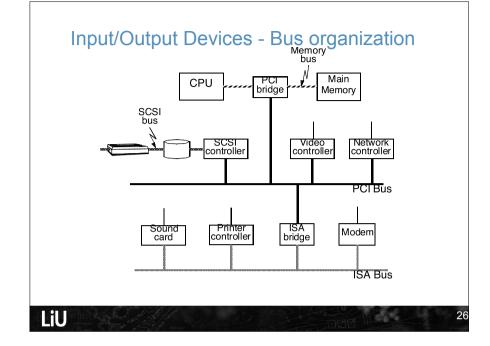

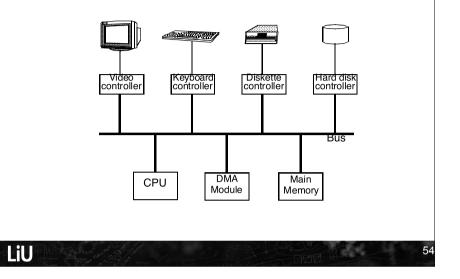

#### Input/Output Devices - Bus organization

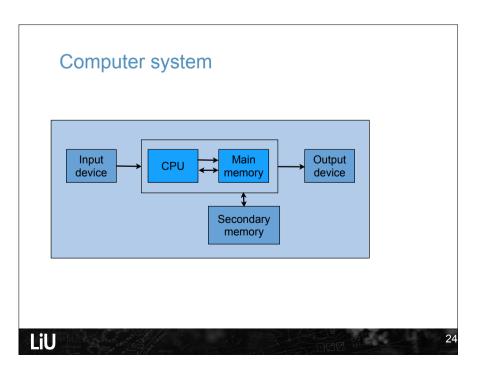

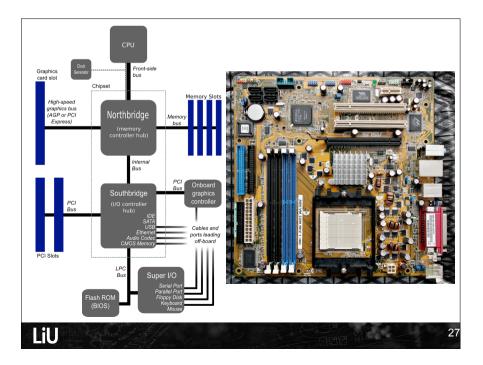

- CPU and memory connected by local bus

- Industry Standard Architecture (ISA) bus

- Peripheral Component Interconnect (PCI) bus

- Peripheral Component Interconnect Express (PCI Express)

- Accelerated Graphics Port (AGP) н.

- Small Computer System Interface (SCSI) bus

- Universal Serial Bus (USB)

- IEEE 1394 (Firewire (Apple), i.LINK (Sony) och DV (Panasonic))

- Thunderbolt

# Input/Output Devices - Bus organization

- A bus is a common electrical pathway between multiple devices. In addition to such "system buses", there are buses also inside the CPU (internal buses).

- System buses differ in the number and organization of lines, arbitration, timing, and specific bus operations.

- Different buses are connected through adequate bridges (bridges also perform buffering of information);

- Advantages of architectures with multiple buses:

- avoids bus conflicts;

- insulates CPU-to-memory traffic from I/O traffic;

- allows the system to support a variety of I/O devices tailored for different bus standards.

- In order to connect a device to a bus, the device controller must fit to the respective bus features.

# Input/Output Devices - Bus organization

- Bus conflict -> bus arbiter decides on access.

- I/O devices are given preference over the CPU; usually devices cannot be stopped -> forcing them to wait would result in loss data.

- When no I/O is in progress, the CPU has all bus cycles for itself to reference memory.

- When some I/O device is also running and requests the bus, it gets it -> cycle stealing slows down the computer.

# LiU

#### Outline

LiU

- Control unit

- Input/Output Devices and System Buses

- Bus organization

- Arbitration, timing

- CPU interface

- I/O interface

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

- RISC and CISC

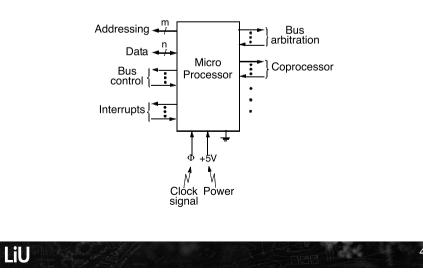

# External Interface of the CPU Chip

# External Interface of the CPU Chip

- The CPU pins can be divided into: address pins, data pins, and control pins.

- address pins: the address is output to the system bus on these pins, for read/write operations. With m address pins, 2<sup>m</sup> locations can be addresses.

- data pins: data bits are output/received to/from the system bus on these pins.

- with n data pins an n-bit word can be read written in a single operation.

- control pins:

LiU

- bus control: the CPU uses these pins to control the rest of the system and tell it what it wants to do; control signals are propagated over the system bus.

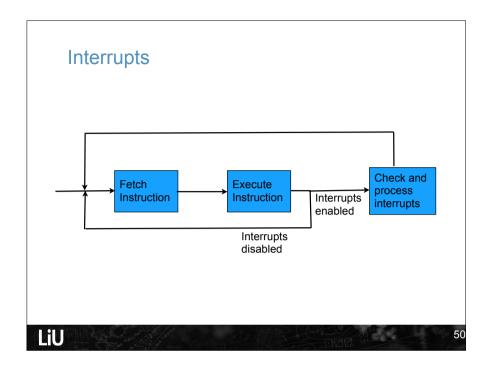

- interrupt pins: on these pins the CPU gets signals from I/O modules; they usually indicate that an I/O operation has been completed;

- bus arbitration: are needed to regulate traffic on the system bus, to prevent devices from trying to use it at the same time;

- coprocessor: facilitate communication with coprocessors, such as floating point chips, graphic chips, etc.

lee' ?

### Outline

- Control unit н.

- Input/Output Devices and System Buses

- Bus organization

- Arbitration, timing

- CPU interface

- I/O interface

- access, I/O processing

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

- RISC and CISC

LiU

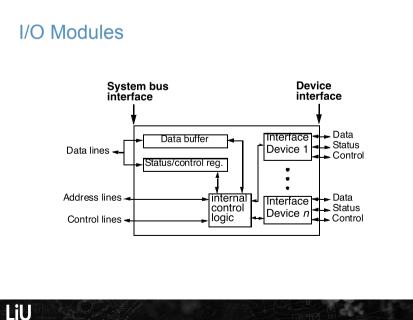

### I/O Modules

- An I/O module has an interface to the device and to the system bus

- Major functions of an I/O module:

- control and timing of the operations;

- bus communication:

- device communication;

- data buffering;

- error detection.

- A possible sequence data transfer between a device and the CPU:

- CPU interrogates the status of I/O module (device).

- I/O module returns device status.

- If the device is OK and ready, the CPU requests the transfer of data by means of a command to the I/O module.

- The I/O module issues commands to the device and obtains data.

#### Summary

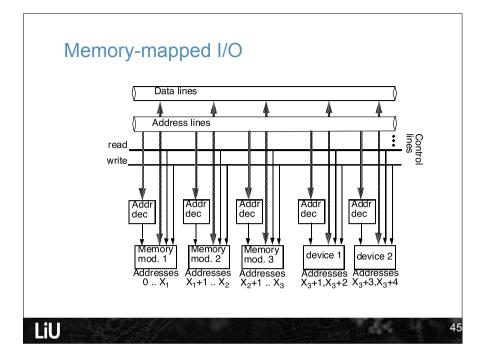

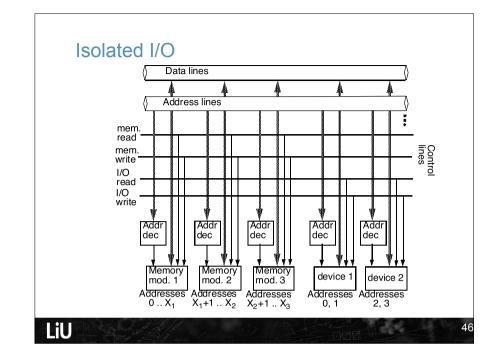

- CPU, memory and I/O devices are connected by system buses.

- The CPU chip is connected through <u>address</u>, <u>data</u>, and <u>control</u> pins.

- A bus consists of <u>data</u>, <u>address</u>, and <u>control</u> lines

- Bus arbitration can be <u>centralized</u> or <u>decentralized</u>.

- Bus coordination can be synchronous or asynchronous.

- I/O modules interface an I/O device to the system bus.

- I/O device can be <u>memory-mapped</u> or <u>isolated I/O</u>.

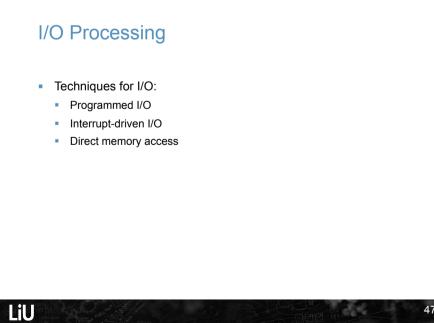

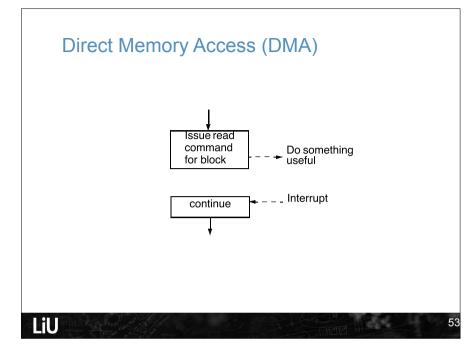

- Techniques for I/O: programmed I/O, interrupt-driven I/O, and direct memory access.

act

# Direct Memory Access (DMA)

# Outline

- Control unit

- Input/Output Devices and System Buses

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

- RISC and CISC

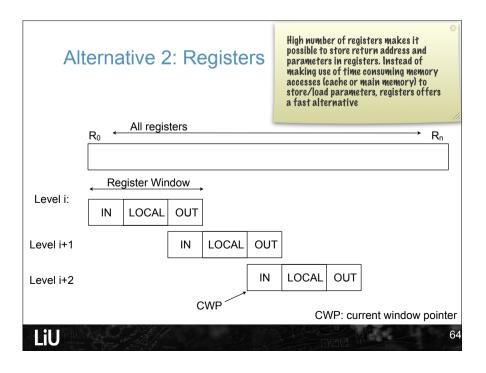

- The problem and motivation

- Register file

- Instruction set

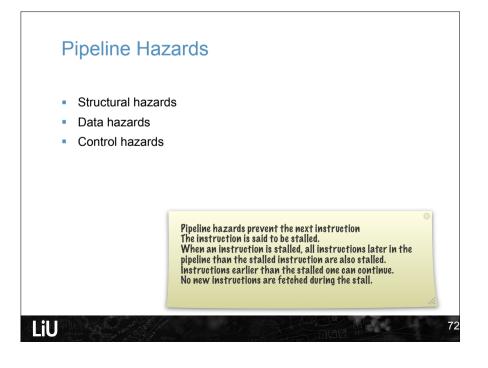

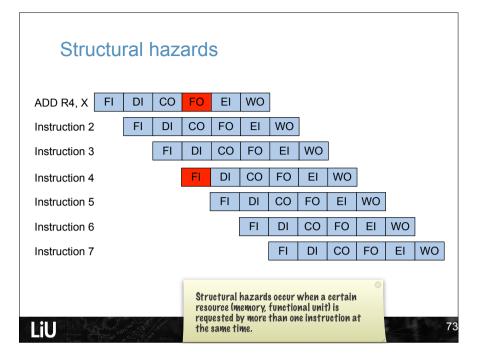

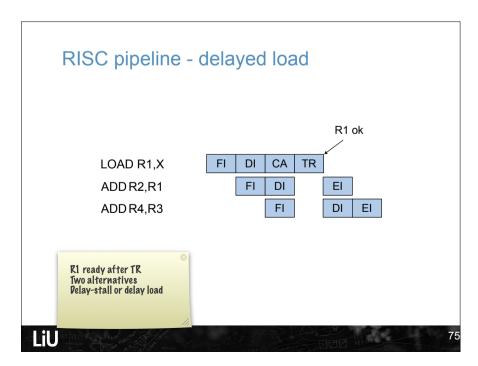

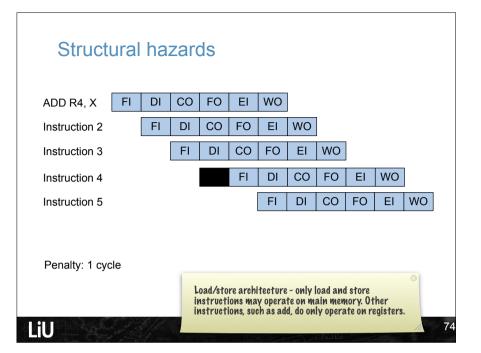

- Pipeline

| The so | Motiva                  |        | the   | or each typ<br>amount of<br>structions. |       | For each type, this is<br>the amount of memory<br>references. |      |  |

|--------|-------------------------|--------|-------|-----------------------------------------|-------|---------------------------------------------------------------|------|--|

|        | is this amo<br>ructions |        | rence | Mach<br>instru<br>weig                  | ction | Merr<br>refer<br>weig                                         | ence |  |

|        |                         | Pascal | С     | Pascal                                  | С     | Pascal                                                        | С    |  |

|        | Assign                  | 45%    | 38%   | 13%                                     | 13%   | 14%                                                           | 15%  |  |

|        | Loop                    | 5%     | 3%    | 42%                                     | 32%   | 33%                                                           | 26%  |  |

|        | Call                    | 15%    | 12%   | 31%                                     | 33%   | 44%                                                           | 45%  |  |

|        | lf                      | 29%    | 43%   | 11%                                     | 21%   | 7%                                                            | 13%  |  |

|        | Other                   | 6%     | 1%    | 3%                                      | 1%    | 2%                                                            | 1%   |  |

- Conclusions:

- There are many assign constructions (X=5, Y=X+Z, ...) in a HLL, but each such instruction results in few machine instructions, often with few memory references.

- On the other hand, there are only few subroutine/procedure/etc (call/return) but each such translates into a high number of machine instructions, with many memory references.

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item>

### Conclusions

- Common with simple (ALU and move) instructions

- Common with simple addressing modes

- Large frequency of operand accesses; on average each instruction references 1.9 operands

- Most of the referenced operands are scalars (so they can be stored in a register) and are local variables or parameters

- Optimizing the procedure CALL/RETURN mechanism promises large benefits in speed

#### Outline

- Control unit

- Input/Output Devices and System Buses

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

61

- RISC and CISC

- The problem and motivation

- Register file

- Instruction set

- Pipeline

LiU

| Alternative 1: Stacl                                                                                                                                                                                           | k                                          |                                                       |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|--|

| instruction 1<br>call proc A<br>instruction 3<br>instruction 4<br>instruction 12<br>instruction 13<br>call proc A<br>call proc A<br>instruction 11<br>instruction 12<br>instruction 13<br>call proc A<br>T1 T3 | PUSH(Item 1)<br>POP<br>PUSH(Item 2)<br>POP | T0     2       T1     1       T2     6       T3     1 |  |  |  |  |  |  |  |

| <ul> <li>PUSH/POP: accesses the memory where the stack is</li> </ul>                                                                                                                                           |                                            |                                                       |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                |                                            |                                                       |  |  |  |  |  |  |  |

| LiU                                                                                                                                                                                                            | Non Contract of Contract                   | 63<br>12012 H                                         |  |  |  |  |  |  |  |

# Program execution analysis

- Procedure Calls

- Even if only 15% of the HLL instructions are CALL or RETURN, they are executed most of the time, because of their complexity.

- A CALL or RETURN is compiled into a relatively long sequence of machine instructions with a lot of memory references.

- Some statistics concerning procedure calls:

- Only 1.25% of called procedures have more than six parameters.

- Only 6.7% of called procedures have more than six local variables.

ee.

Chains of nested procedure calls are usually short and only very seldom longer than 6.

# Liu

# <section-header><list-item><list-item><list-item><list-item>

# Outline

- Control unit

- Input/Output Devices and System Buses

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

- RISC and CISC

- The problem and motivation

- Register file

- Instruction set

- Pipeline

# Outline

- Control unit

- Input/Output Devices and System Buses

- Programmed I/O, Interrupt-driven I/O, and Direct Memory Access

LEI Loci

69

- RISC and CISC

- The problem and motivation

- Register file

- Instruction set

- Pipeline

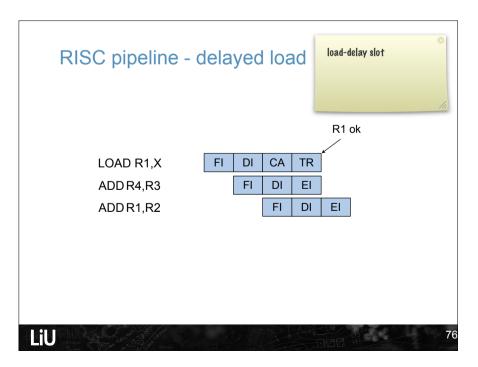

| Pipe | liniı                                    | ng        |          |    |          |       |    | DI<br>C<br>F(<br>EI | l: Dec<br>O: Cal<br>D: Fet<br>: Exec | ode In<br>Iculate<br>ch Op<br>cute In | euction<br>structi<br>opera<br>erand<br>struction | on<br>and<br>on |

|------|------------------------------------------|-----------|----------|----|----------|-------|----|---------------------|--------------------------------------|---------------------------------------|---------------------------------------------------|-----------------|

|      | FI                                       | DI        | CO       | FO | EI       | WO    |    | vv                  | 0. 11                                |                                       |                                                   |                 |

|      |                                          | FI        | DI       | CO | FO       | EI    | WO | ]                   |                                      |                                       |                                                   |                 |

|      |                                          |           | FI       | DI | CO       | FO    | EI | WO                  |                                      |                                       |                                                   |                 |

|      |                                          |           |          | FI | DI       | CO    | FO | EI                  | WO                                   | ]                                     |                                                   |                 |

|      |                                          |           |          | [  | FI       | DI    | CO | FO                  | EI                                   | WO                                    | ]                                                 |                 |

|      |                                          |           |          |    |          | FI    | DI | CO                  | FO                                   | EI                                    | WO                                                |                 |

|      |                                          |           |          |    |          |       | FI | DI                  | CO                                   | FO                                    | EI                                                | WO              |

|      | <br>•                                    |           |          |    | 2        | 2*T   |    |                     |                                      |                                       |                                                   |                 |

| LiU  | C. C | et / 15/2 | terman . |    | a Availe | HEMIN |    |                     | 8/10<br>10 - H                       |                                       |                                                   | 71              |

# CISC

- A large number of instructions

- <u>Complex</u> instructions and data types

- <u>Many and complex</u> addressing modes.

- · High-level instructions map direct to instructions

- Microprogramming to implement instructions

- Memory bottleneck is a major problem:

- complex addressing modes and multiple memory

- accesses per instruction.

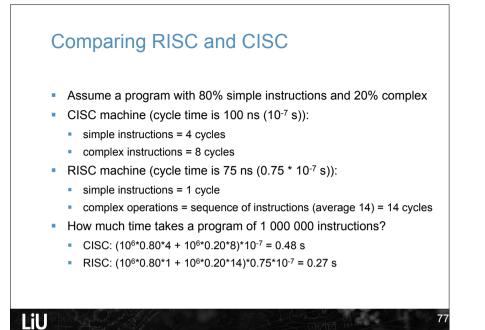

# Comparing RISC and CISC

LiU

- Complex operations take more time on the RISC, but their number is small;

- because of its simplicity, the RISC works at a smaller cycle time; with the CISC, simple instructions are slowed down because of the increased data path length and the increased control complexity.

# CISC

#### CISC

#### Advantages:

- Easier to map high-level instruction to machine instruction

- Smaller programs; less memory

- Fewer instructions, lead to smaller execution time.

- Disadvantages

- A large instruction set is difficult to decode and execute

- Instructions may not match all high-level language exactly,

Les beet

Complex design tasks.

#### CISC - Intel 486

- 32-bit processor

- Registers

- 8 general

- 6 address

- 2 status/control

- 1 instruction pointer (program counter)

- On-chip floating point unit

- Micro-programmed control

- Instruction set:

- 253 instructions

- Instruction size: 1-12 bytes

- Addressing modes: 11

# **CISC** processors

- VAX 11/780

- Nr. of instructions: 303

- Instruction size: 2 57 bytes

- Instruction format: not fixed

- Addressing modes: 22

- Number of general purpose registers: 16

- Pentium

- Nr. of instructions: 235

- Instruction size: 1 11 bytes

- Instruction format: not fixed

- Addressing modes: 11

- Number of general purpose registers: 8

LiU

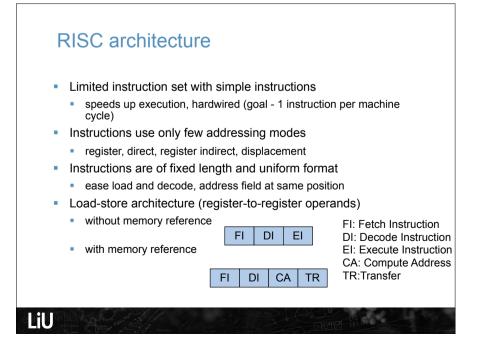

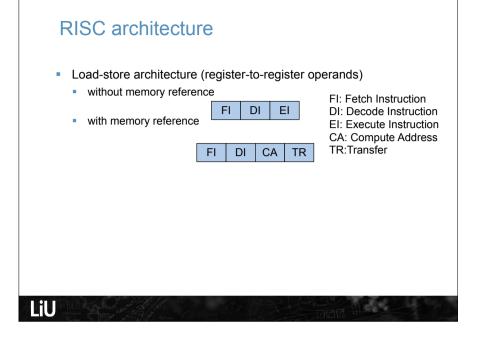

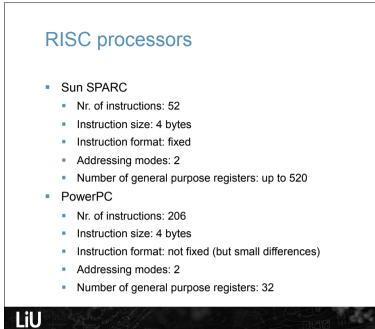

### RISC

- <u>Limited</u> instruction set

- <u>Simple</u> instructions and data types.

- Few and simple addressing modes

- Instructions are of <u>fixed length</u>

- Load-and-store architecture

- <u>Hardwired</u> controller to implement instructions

82

ee /

Load/store reduces pipeline penalties

CC.

LiU

LiU

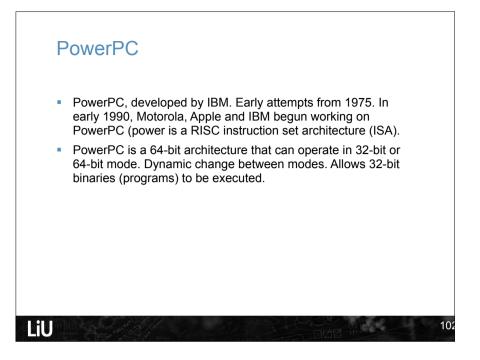

#### **RISC** Architectures

- MIPS

- SPARC

- PowerPC

- ARM

### Summary

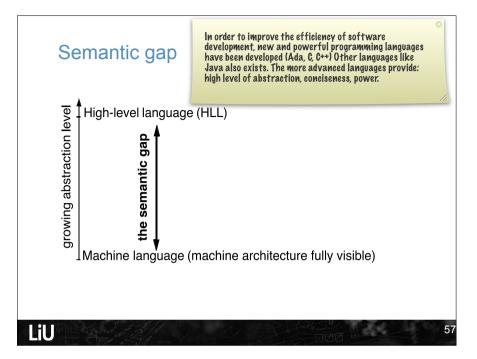

- Both RISCs and CISCs try to cover the semantic gap

- CISC approach: implements more and more complex instructions

- RISC approach: try to simplify the instruction set

- Main features of RISC architectures are:

- reduced number of simple instructions,

- few addressing modes,

- load-store architecture,

- instructions are of fixed length and format,

- a large number of registers is available.

- One main concerns for RISC maximize the efficiency of pipelining.

- Present architectures often include both RISC and CISC features.

86

de /

#### MIPS

LiU

- MIPS(Microprocessor without Interlocked Pipeline Stages)

- MIPS32, 32-bits, MIPS64, 64-bits

- 32 general purpose registers (R0=0, R31=link register), Program counter, 2 register for multiplication/division

- Load/store architecture

- Fixed-length instruction format (32 bits)

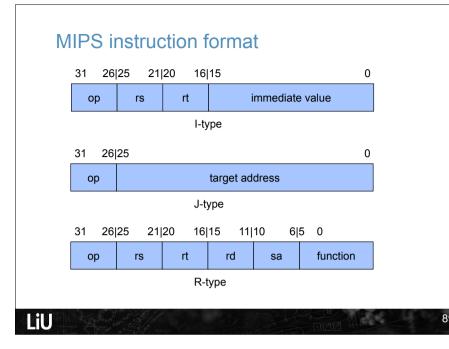

- Immediate (I-type): load and store instructions. The immediate value is 16 bits.

- Jump (J-type): 26-bit target address is combined with higher-order bits of PC to get absolute address

- Register (R-type): Arithmetic and logical instructions use the format as well as instructions where the target address is specified indirectly via a register.

LiU

#### SPARC

- Scalable Processor ARCitecture (SPARC) developed by SUN and is based on RISC II from University of California, Berkely.

- Open architecture (license). Different companies makes the processor.

- 64-bit since 1993.

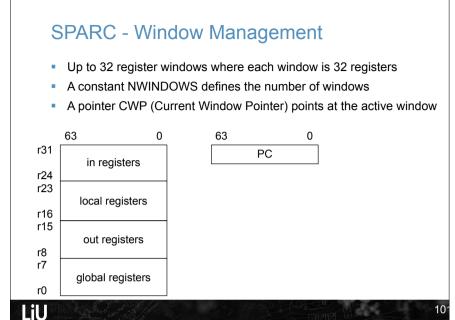

- A user's program sees 32 general purpose registers of 64-bits. r31-r24 are in-registers, r23-r16 are local registers, r15-r8 out registers and r7-r0 are global registers

- 2 addressing modes

- Register Indirect with Immediate -> address=content of Rx + constant (Rx can be any register and constant is 13-bit displacement)

- Register Indirect with Index -> address=content of Rx + content of Ry (Rx and Ry can be any register)

ac.

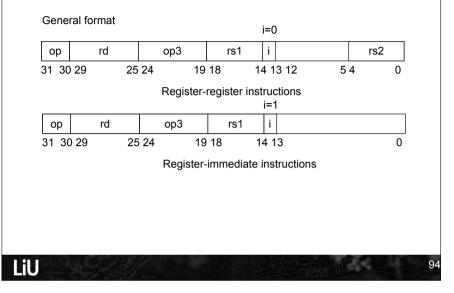

#### SPARC - instruction set

- Instruction length: 32 bits

- Only load and store access memory

- Opcode (2-bits) more bits to detail specific opcode

- Arithmetic instructions:

- Add add rs1, rs2, rd rd<-rs1+rs2

- Mul mul rs1, rs2, rd rd<-rs1\*rs2 (64 bits times 64 times -> 128 bits)

# SPARC - procedure calls

LiU

| Caller | Callee | Usage           |

|--------|--------|-----------------|

| %00    | %i0    | First argument  |

| %01    | %i1    | Second argument |

| %o2    | %i2    | Third argument  |

| %o3    | %i3    | Fourth argument |

| %04    | %i4    | Fifth argument  |

| %05    | %i5    | Sixth argument  |

| %06    | %i6    | Stack pointer   |

| %07    | %i7    | Return adress   |

93

# SPARC - instruction set

#### PowerPC - register set

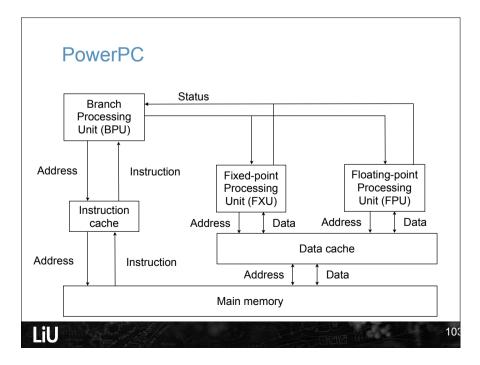

- 32 general purpose registers for integer data

- 32 general purpose registers for floating point data

- 1 condition register keeps conditions from FXU and FPU

- 1 link register keeps the return address of procedure calls

#### LiU

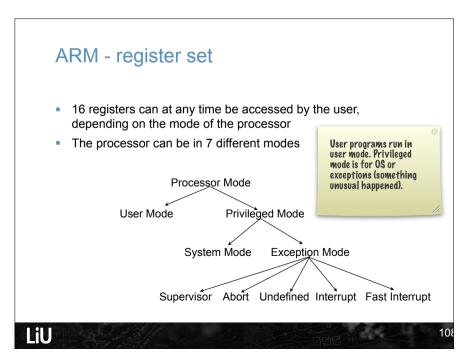

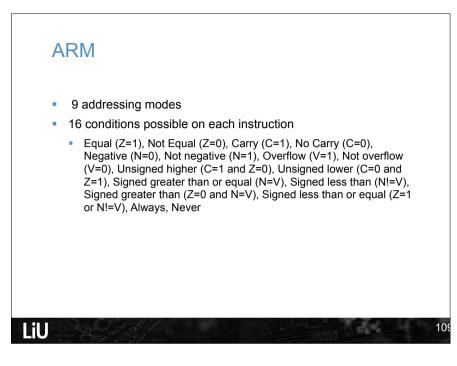

# ARM

- Acorn RISC Machine (ARM), later Advanced RISC Machine

- Embedded systems such as mobile phones

- First versions had 26-bit address space

- DSP-instructions, Single-Instruction Multiple Data (SIMD) instructions

- 37 registers; 31 general purpose + 6 program status

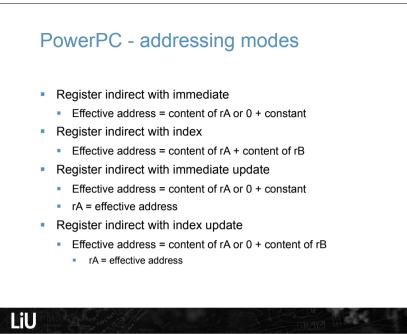

#### PowerPC - instruction set

| _      |         |      | 1                               |                    |          | 1             |       |  |  |

|--------|---------|------|---------------------------------|--------------------|----------|---------------|-------|--|--|

|        | ор      | rd   | ra                              | rb                 | OE       |               | rc    |  |  |

| 0      | 5       | 6 10 |                                 | 16<br>er format    | 20 21    | 22            | 30 31 |  |  |

|        | ор      | rd   | ra                              | 1                  | 6-bit im | mediate value |       |  |  |

| 0      | 5       | 6 10 | 10 11 15 16<br>Immediate format |                    |          |               |       |  |  |

|        | ор      |      | 24                              | 4-bit immed        | iate val | ue            |       |  |  |

| 0      | 5       | 6    | 3 Unconditional branch format   |                    |          |               |       |  |  |

|        | ор      | rd   | ra                              |                    | 16-bit c | lisplacement  |       |  |  |

| 0      | 5       | 6 10 | ) 11 15<br>Register inc         | 16<br>direct forma | ıt       |               | 31    |  |  |

|        | ор      | rd   | ra                              | rb                 | c        | ptions        |       |  |  |

| 0      | 5       | 6 10 | ) 11 15<br>Load/store           | 16 20<br>format    | 21       |               | 31    |  |  |

| AL SOL | 8158379 |      | THERE ACCOUNTS                  | MEMIN<br>Net Ward  | and the  |               |       |  |  |

### Questions

- What does the control unit do?

- How can you implement the control unit?

- If execution of an instruction consists of fetch and execute, detail what the control unit should do during fetch.

- What is RISC? CISC? Which to pick?

- What is typical for a CISC (RISC)?

- Name a few RISC processors (and a few CISC processors)

- What is the RISC philosophy to minimize "FO hazards"?

- What type of hazard is a "FO" hazard?

- How can I/O be handled?

- What is interrupt? How does it work?

- What is programmed I/O? Name disadvantages.

- Detail an instruction you would not see in a RISC machine

- Which alternative exists to handle subroutine and procedure calls (which is best from performance (speed) point of view)

- Is fix-length instructions good or bad?

# Summary

- Instruction size: 4 bytes (MIPS, SPARC, PowerPC)

- Instruction sets for PowerPC and ARM are fairly advanced

- ARM has quite many addressing modes

# LiU