## STATE MACHINES

Q

Q

LECTURE VI TDDI11 Embedded Software

DEPT. COMPUTER AND INFORMATION SCIENCE (IDA) LINKÖPINGS UNIVERSITET

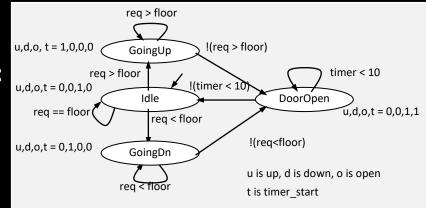

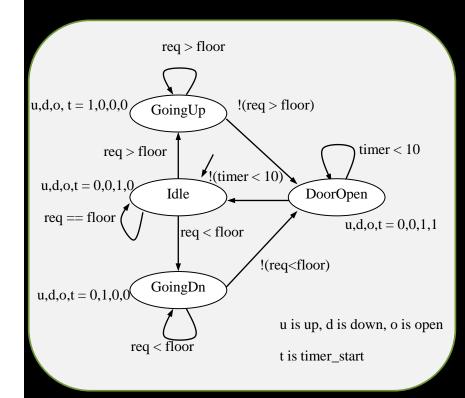

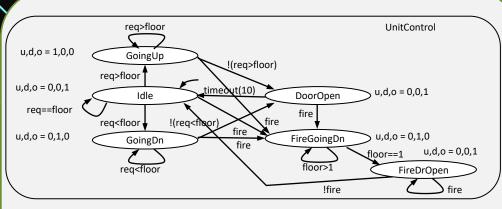

### INTRODUCTORY EXAMPLE: AN ELEVATOR CONTROLLER

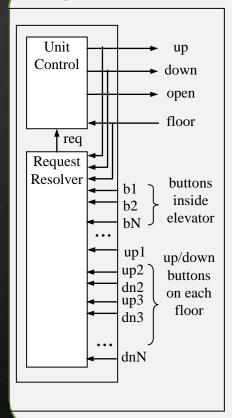

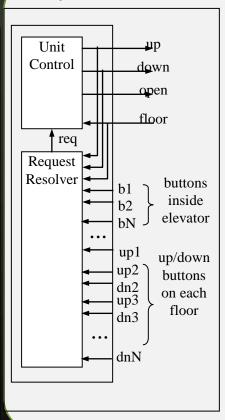

### Simple elevator controller

- Request Resolver resolves various floor requests into single requested floor

- Unit Control moves elevator to this requested floor

"Move the elevator either up or down to reach the requested floor. Once at the requested floor, open the door for at least 10 seconds, and keep it open until the requested floor changes. Ensure the door is never open while moving. Don't change directions unless there are no higher requests when moving up or no lower requests when moving

down..."

Partial English description

#### **System interface**

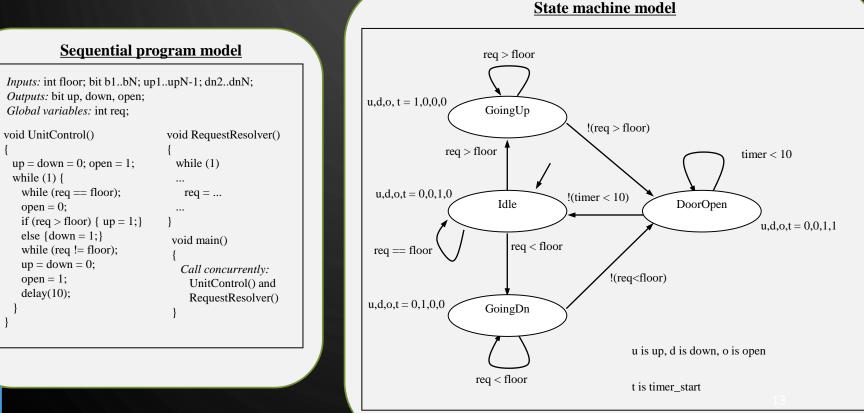

### ELEVATOR CONTROLLER: A SEQUENTIAL PROGRAM MODEL

#### Sequential program model

*Inputs:* int floor; bit b1..bN; up1..upN-1;dn2..dnN; *Outputs:* bit up, down, open; *Global variables:* int req;

|                                                                                        | void                                                                                          |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| void UnitControl()                                                                     | RequestResolver()                                                                             |

| {<br>up = down = 0; open = 1;<br>while (1) {<br>while (req == floor);<br>open = 0;     | {<br>while (1)<br><br>req =                                                                   |

| if (req > floor) { up = 1;}<br>else {down = 1;}                                        | }                                                                                             |

| <pre>while (req != floor);<br/>up = down = 0;<br/>open = 1;<br/>delay(10);<br/>}</pre> | <pre>void main() {     Call concurrently:     UnitControl() and     RequestResolver() }</pre> |

#### **Partial English description**

"Move the elevator either up or down to reach the requested floor. Once at the requested floor, open the door for at least 10 seconds, and keep it open until the requested floor changes. Ensure the door is never open while moving. Don't change directions unless there are no higher requests when moving up or no lower requests when moving down..."

#### **System interface**

$\mathbf{O}$

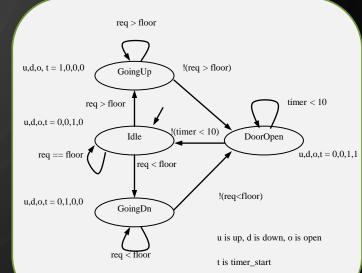

### FINITE-STATE MACHINE (FSM) MODEL

- Trying to capture this behavior as sequential program is a bit awkward

- Instead, we might consider an FSM model, describing the system as:

- Possible states

- E.g., Idle, GoingUp, GoingDn, DoorOpen

- Possible transitions from one state to another based on input

- E.g., req > floor

- Actions that occur in each state

- E.g., In the GoingUp state, u,d,o,t = 1,0,0,0 (up = 1, down, open, and timer\_start = 0)

# STATE MACHINE

Ò

- The system is described as a set of states

- Each state is a representation of what the system looks like now and how it got there

- Each state reacts in a specific way to *every possible* input event, leading to a new state via a transition

# MEALY AND MOORE

### • There are two kinds of state machines

Mealy and Moore

Ò

$\bullet$

- Both are finite state machines

- Both can capture regular expressions

- Note: Finite state machines and finite automata are used interchangeably

## » MOORE MACHINES

A Moore machine is a tuple  $(Q, \Sigma, \Gamma, \Delta, H, q_0)$  consisting in:

- 1. a finite set Q of states where  $q_0$  is the start state

- 2. an alphabet  $\Sigma$  of input letters

- 3. an alphabet  $\Gamma$  of output characters

- 4. a mapping  $\Delta$  associating a state in Q to each pair in ( $Q \times \Sigma$ )

- 5. a mapping *H* associating an output in  $\Gamma$  to each state in *Q*

$(q, \sigma) \xrightarrow{\Delta: \text{ transition}} q' \text{ where } q, q' \in Q \text{ and } \sigma \in \Sigma$  $q \xrightarrow{H: \text{ output}} o \text{ where } q \in Q \text{ and } o \in \Gamma$

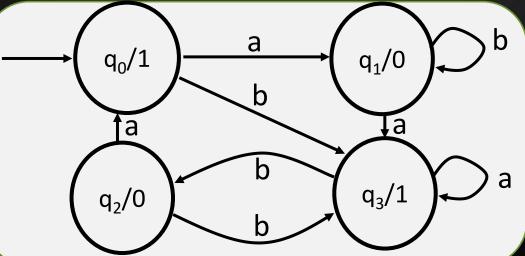

# EXAMPLE OF A MOORE MACHINE

Example: states =  $\{q_0, q_1, q_2, q_3\}$

Q

$\Sigma$ ={a,b}

$\Gamma = \{0, 1\}$

a b a b

1

$\left( \right)$

$\left(\right)$

1

0

Old state Output by the New state old state After input a After input b 1  $\rightarrow q_0$  $q_1$  $q_3$ 0  $\mathbf{q}_3$  $q_1$  $q_1$  $\mathbf{q}_2$ 0  $\mathbf{q}_0$  $q_3$ 1  $\mathbf{q}_3$  $\mathbf{q}_3$  $\mathbf{q}_2$

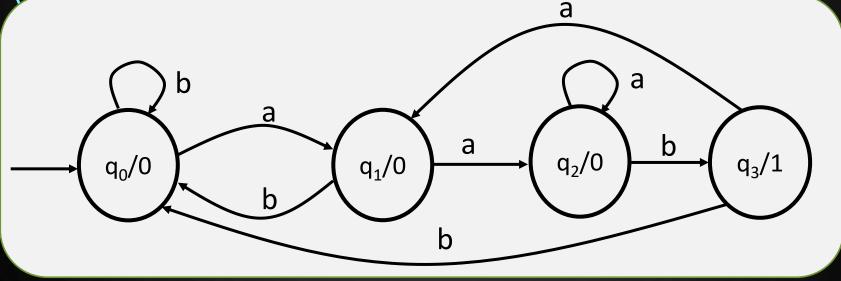

# ANOTHER MOORE MACHINE

0

| Input  |                | а                     | а                     | а                     | b                     | а                     | b                     | b                     | а                     | а                     | b                     | b                     |

|--------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| State  | q <sub>0</sub> | <b>q</b> <sub>1</sub> | <b>q</b> <sub>2</sub> | <b>q</b> <sub>2</sub> | <b>q</b> <sub>3</sub> | <b>q</b> <sub>1</sub> | <b>q</b> <sub>0</sub> | <b>q</b> <sub>0</sub> | <b>q</b> <sub>1</sub> | <b>q</b> <sub>2</sub> | <b>q</b> <sub>3</sub> | <b>q</b> <sub>0</sub> |

| Output | 0              | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     | 0                     |

When does the machine output 1?

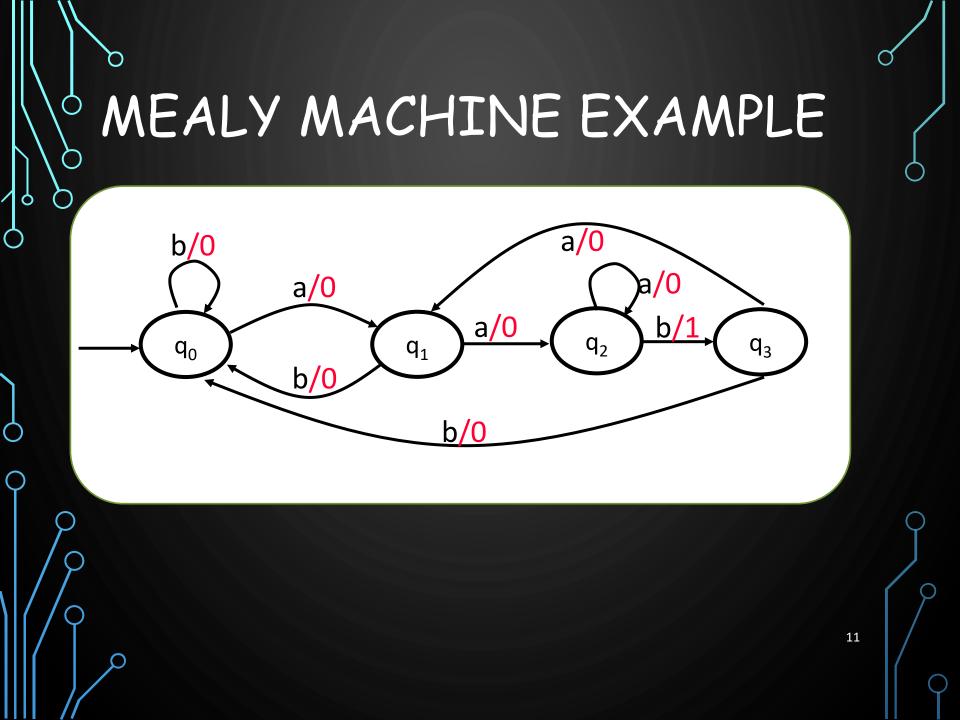

# MEALY MACHINE

A Mealy machine is a tuple  $(Q, \Sigma, \Gamma, \Delta, q_0)$  consisting in:

- a finite set of Q of states where  $q_0$  is the start state

- an alphabet  $\Sigma$  of input letters

$\sigma/o$

$(q,\sigma)$

q

- an alphabet  $\Gamma$  of output characters

- a finite set of transitions Δ that indicate, for each state and letter of the input alphabet, the state to go to next and the associated output.

$\rightarrow (q', o)$  where  $q, q' \in Q, \sigma \in \Sigma$  and  $o \in \Gamma$

## AN EXTENDED FINITE STATE MACHINE

FSMD extends FSM with Data: complex data types and variables for storing data

An FSMD is a tuple  $(Q, \Sigma, \Gamma, V, \Delta, H, q_0)$ :

- 1. *Q* is a finite set of states

- 2.  $\Sigma$  *is the set of possible* inputs

- 3.  $\Gamma$  is the set of possible outputs

- 4. V is a set of variables

- 5.  $\Delta$  associates a state to any triple in  $S \times \Sigma \times V$

- 6. H represents actions: it associates an output and values to V for each state

System state completely described by the current state and values of all variables

# DESCRIBING A SYSTEM AS A STATE MACHINE

## DESCRIBING A SYSTEM AS A STATE MACHINE

#### 1. List all possible states

- 2. Declare all variables

- 3. For each state, list possible transitions, with conditions, to other states

- 4. For each state and/or transition, list associated actions

- 5. For each state, ensure exclusive and complete exiting transition conditions

- No two exiting conditions can be true at same time. Otherwise, nondeterministic state machine

- One condition must be true at any given time

### STATE MACHINE VS. SEQUENTIAL PROGRAM MODEL

- Different thought process used with each model

- State machine:

- Encourages designer to think of all possible states and transitions among states based on all possible input conditions

- Sequential program model:

- Designed to transform data through series of instructions that may be iterated and conditionally executed

### CAPTURING STATE MACHINES IN SEQUENTIAL PROGRAMMING LANGUAGE

- Despite benefits of state machine model, most popular development tools use sequential programming language

- C, C++, Java, Ada, VHDL, Verilog, etc.

- Development tools are complex and expensive, therefore not easy to adapt or replace

- Two approaches to capturing state machine model with sequential programming language

- Front-end tool approach

- Language subset approach

### LANGUAGE SUBSET APPROACH

```

#define IDLE 0

#define GOINGUP 1

#define GOINGDN 2

#define DOOROPEN 3

void UnitControl() {

int state = IDLE:

while (1) {

switch (state) {

IDLE: up=0; down=0; open=1; timer start=0;

if (req==floor) {state = IDLE;}

if (reg > floor) {state = GOINGUP;}

if (reg < floor) {state = GOINGDN;}</pre>

break;

GOINGUP: up=1; down=0; open=0; timer start=0;

if (reg > floor) {state = GOINGUP;}

if (!(reg>floor)) {state = DOOROPEN;}

break;

GOINGDN: up=1; down=0; open=0; timer start=0;

if (req < floor) {state = GOINGDN;}</pre>

if (!(reg<floor)) {state = DOOROPEN;}</pre>

break;

DOOROPEN: up=0; down=0; open=1; timer start=1;

if (timer < 10) {state = DOOROPEN;}</pre>

if (!(timer<10)){state = IDLE;}</pre>

break;

```

<u>UnitControl state machine in</u> sequential programming language

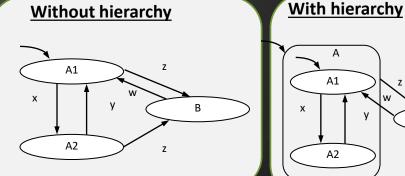

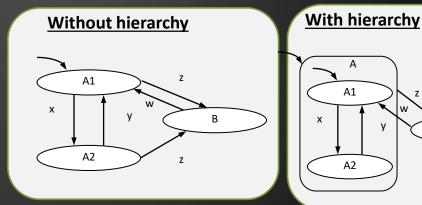

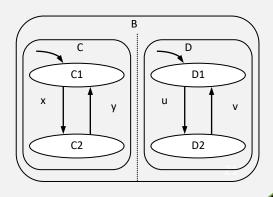

### HIERARCHICAL/CONCURRENT STATE MACHINE MODEL

#### Another Model for state-based specification

$\mathbf{O}$

Uses Hierarchies and Concurrency to eliminate clutter and clarify the structure

А A1 В

A2

Allows states to be grouped together

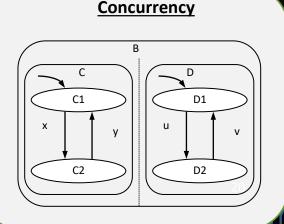

# GROUPS IN STATECHART

Statecharts define a ightarrowlanguage for HCFSMs

Two groups are

OR

Q

AND lacksquare

Concurrency

w

В

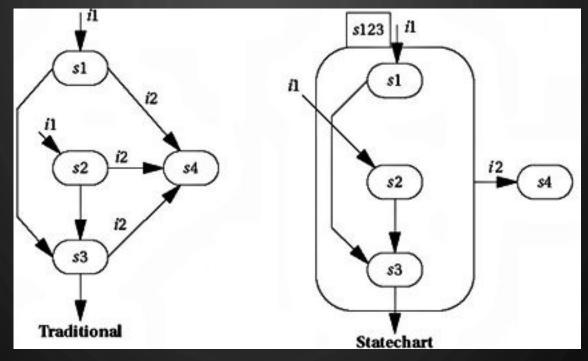

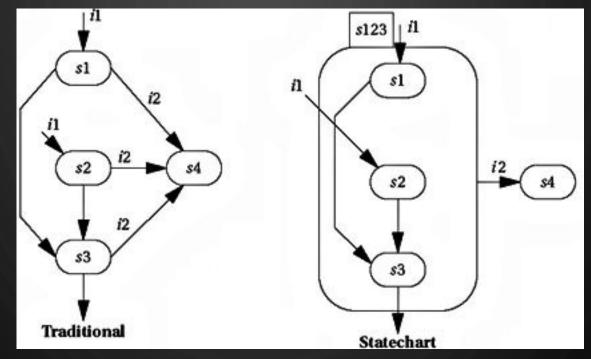

# EXAMPLE OF OR

Q

- The machine goes to s4 from s1, s2, s3

- Statechart captures this by having one state around s1, s2, and s3

# EXAMPLE OF OR

$\cap$

Q

- A single transition out of s123 means that on event i2, all states go to s4.

- The OR state allows transitions between its own internal states

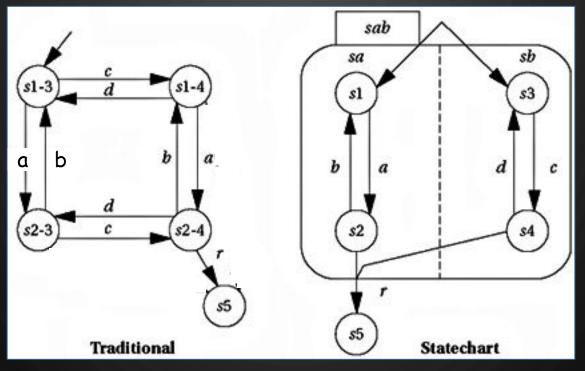

# EXAMPLE OF AND GROUP

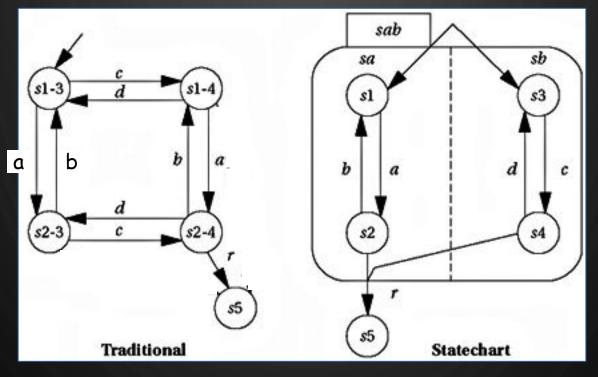

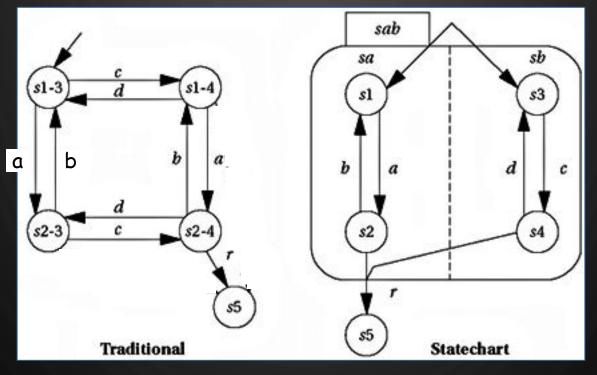

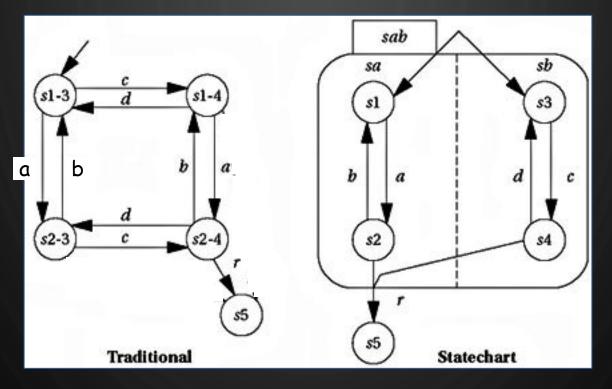

The traditional model has many transitions

• Between states

Ó

- Going out of all states

- One initial transition

# EXAMPLE OF AND

Ó

- The statechart has an AND state called sab

- sab has two components sa and sb

- When the machine enters the state sab, it is simultaneously in both sa and sb

- We must know both sa and sb to know sab

# EXAMPLE OF AND

- The name of states reveal their relations

- s1-3 corresponds to sab in s1 and in s3

- When the machine enters the state sab, it is simultaneously in both sa and sb

Ó

Both models describe the same behavior but the statechart is much simpler, cleaner and easier to understand

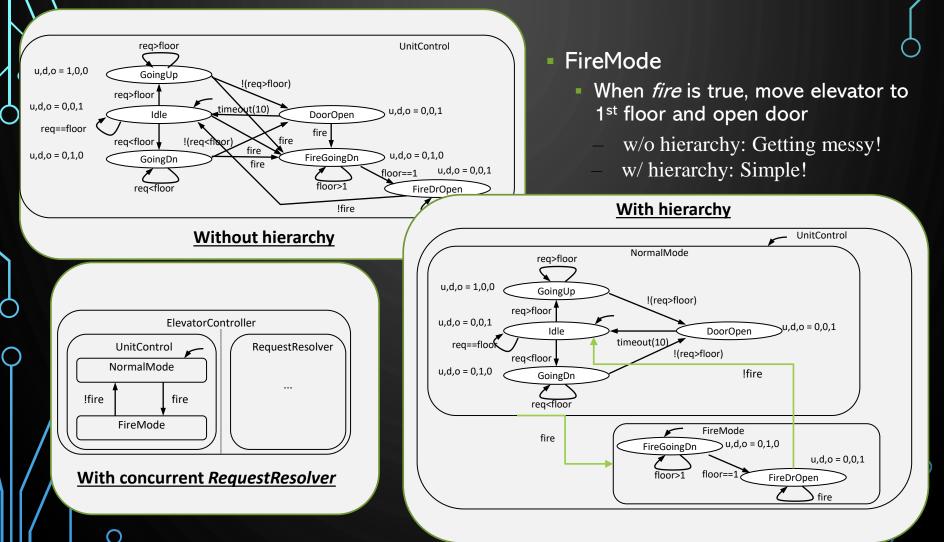

# EXAMPLE OF HCFSM MODELING

**Without hierarchy**

FireMode

- When *fire* is true, move elevator to 1<sup>st</sup> floor and open door

- w/o hierarchy: Getting messy!

- w/ hierarchy: Simple!

# EXAMPLE OF HCFSM MODELING

## FSM LAB ON STM32L562

Q

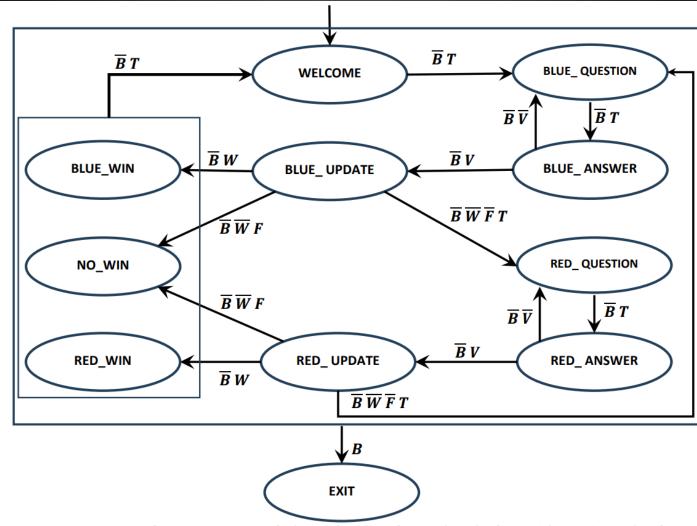

### STATE MACHINE FOR THE GAME

$\bigcirc$

$\bigcirc$

Q

Figure 2 State Machine for TicTacToe. B stands for (pressed) Button, V for Valid (move), T for Touch (screen detected), W for Win, F for Full. Overlines correspond to negations.

### STATE MACHINE FOR THE GAME

```

. . .

//Update State on entry

if(State != PreviousState){

switch(State){

case WELCOME:

Initialize Board(BoardState);

. . .

break;

case BLUE QUESTION:

Touch = 0;

. . .

break;

case BLUE ANSWER:

Valid = Check Move Validity(...);

break;

. . .

} //update state

}//on entry

```

while (1){

```

// transitions

switch(State){

case WELCOME:

PreviousState = WELCOME;

if(Button){

State = EXIT;

}else if(Touch){

State = BLUE QUESTION;

break;

case BLUE QUESTION:

PreviousState = BLUE QUESTION;

if(Button){

State = EXIT;

}else if(Touch){

State = BLUE ANSWER;

break;

}// transitions

```

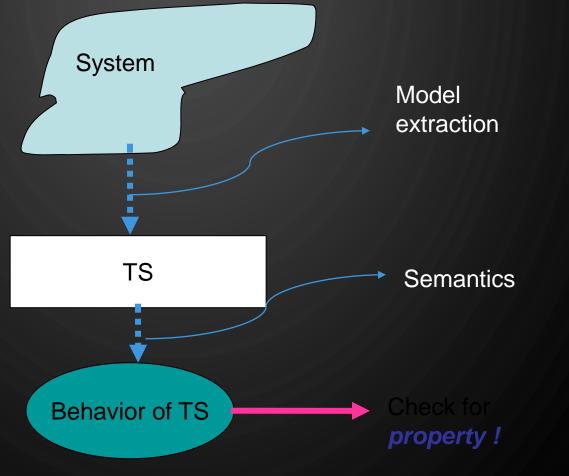

# VERIFICATION

### THE VERIFICATION SETTING

$\bigcirc$

Q

# TRAIN GATE EXAMPLE

- On the model checker UPPAAL

- You can download it from <u>http://uppaal.org/</u>

- Several demos of timed systems, the train gate controller is one of them

45

You can do simulation and verification