TDDD55 Compilers and Interpreters (opt.)

TDDB44 Compiler Construction

### Code Generation for RISC and Instruction-Level Parallel Processors

RISC/ILP Processor Architecture Issues

Instruction Scheduling

Register Allocation

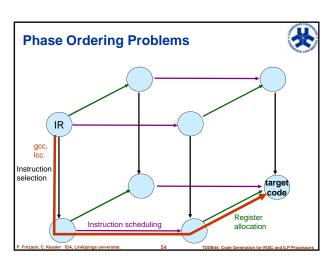

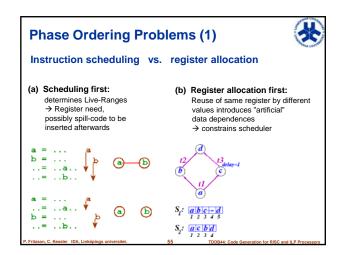

Phase Ordering Problems

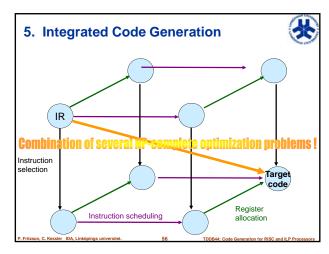

Integrated Code Generation

Peter Fritzson, Christ

Peter Fritzson, Christoph Kessler IDA, Linköpings universitet, 2011. TDDD55 Compilers and Interpreters (opt.)

TDDB44 Compiler Construction

# 1. RISC and Instruction-Level Parallel Target Architectures

Peter Fritzson, Christoph Kessler IDA, Linköpings universitet, 2011.

#### CISC vs. RISC

#### CISC

- Complex Instruction Set Computer

- Memory operands for arithmetic and logical operations possible

- $M(r1+r2) \leftarrow M(r1+r2) * M(r3+disp)$

- Many instructions

- Complex instructions

- Few registers, not symmetric

- Variable instruction size

- Instruction decoding (often done in microcode) takes much silicon overhead

- Example: 80x86, 680x0

#### ■ RISC

- Reduced Instruction Set Computer

- Arithmetic/logical operations only on registers

- add r1, r2, r1 load (r1), r4 load r3+disp, r5 mul r4, r5 store r5, (r1)

- Few, simple instructions

- Many registers, all general-purpose typically 32 ... 256 registers

- Fixed instruction size and format

- Instruction decoding hardwired

- Example: POWER, HP-PA RISC, MIPS, ARM, SPARC

P. Fritzson, C. Kessler IDA, Linköpings universitet

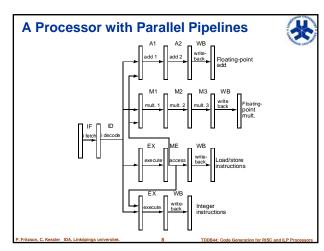

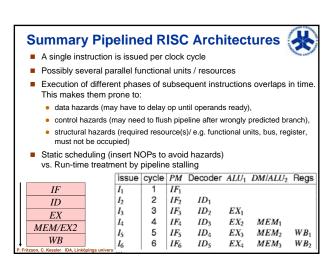

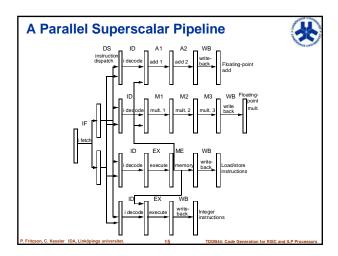

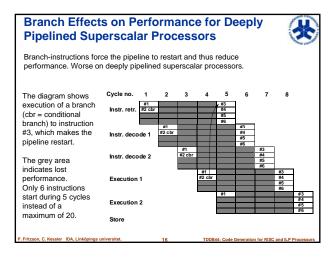

## Instruction-Level Parallel (ILP) architectures

Single-Issue: (can start at most one instruction per clock cycle)

- Simple, pipelined RISC processors with one or multiple functional units

- e.g. ARM9E, DLX

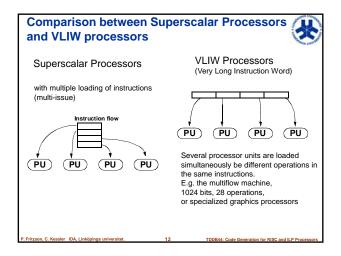

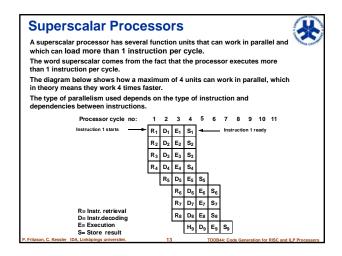

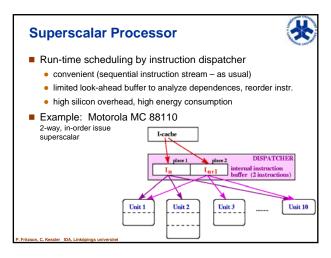

Multiple-Issue: (can start several instructions per clock cycle)

- Superscalar processors

- e.g. Sun SPARC, MIPS R10K, Alpha 21264, IBM Power2, Pentium

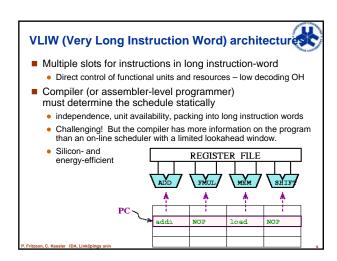

- VLIW processors (Very Long Instruction Word)

- e.g. Multiflow Trace, Cydrome Cydra-5, Intel i860, HP Lx, Transmeta Crusoe; most DSPs, e.g. Philips Trimedia TM32, TI 'C6x

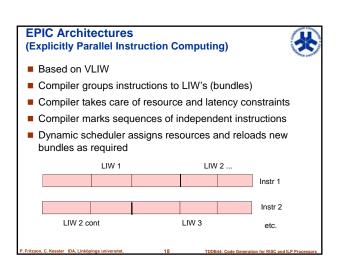

- EPIC processors (Explicitly Parallel Instruction Computing)

- e.g. Intel Itanium family (IA-64)

tzson, C. Kessler IDA, Linköpings universitet. 4

TDDB44: Code Generation for RISC and ILP Processor

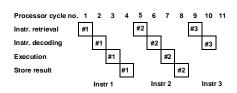

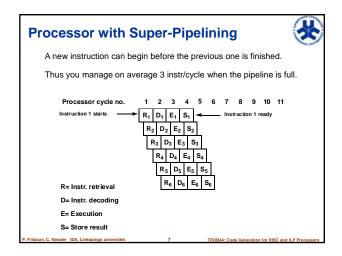

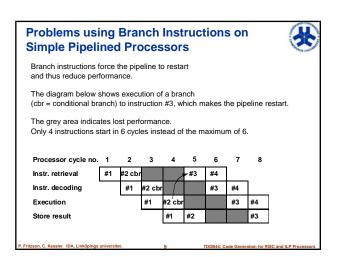

#### **Processors with/without Pipelining**

Traditional processor without pipelining

One instruction takes 4 processor cycles, i.e. 0.25 instructions/cycle

P. Fritzson, C. Kessler IDA, Linköpings universitet. 5 TDDB44: Code Generation for RISC and ILP Processor.

#### **Processor with Simple Pipelining**

An instruction takes 1 cycle on average with pipeline i.e. 1 instruction/cycle

This pipeline achieves 4-way parallelism

Erikson C Veccler IDA Liskining unburgitet

#### **Global Register Allocation**

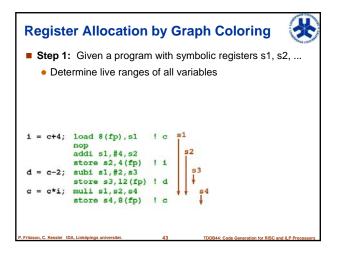

- Register Allocation: Determines values (variables, temporaries, constants) to be kept when in registers

- Register Assignment: Determine in which physical register such a value should reside.

- Essential for Load-Store Architectures

- Reduce memory traffic (→ memory / cache latency, energy)

- Limited resource

- Values that are alive simultaneously cannot be kept in the same register

- Strong interdependence with instruction scheduling

- scheduling determines live ranges

- spill code needs to be scheduled

- **Local register allocation** (for a single basic block) can be done in linear time (see previous lecture)

- Global register allocation on whole procedure body (with minimal spill code) is NP-complete. Can be modeled as a graph coloring problem [Ershov'62] [Cocke'71].

### When do Register Allocation

- Register allocation is normally performed at the end of global optimization, when the final structure of the code and all potential use of registers is known.

- It is performed on abstract machine code where you have access to an unlimited number of registers or some other intermediary form of program.

- The code is divided into sequential blocks (basic blocks) with accompanying control flow graph.

### **Live Range**

(Here, variable = program variable or temporary)

- A variable is being defined at a program point if it is written (given a value) there.

- A variable is used at a program point if it is read (referenced in an expression) there.

- A variable is live at a point if it is referenced there or at some following point that has not (may not have) been preceded by any definition.

- A variable is reaching a point if an (arbitrary) definition of it, or usage (because a variable can be used before it is defined) reaches the point.

- A variable's **live range** is the area of code (set of instructions) where the variable is both alive and reaching.

- does not need to be consecutive in program text.

## Live Range Example x is defined x := 5+u: Use of x Live range for x Last use of x v := 35 + x + z:

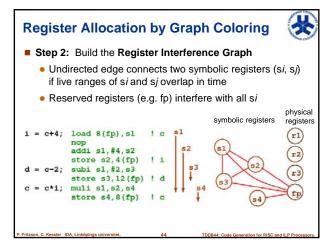

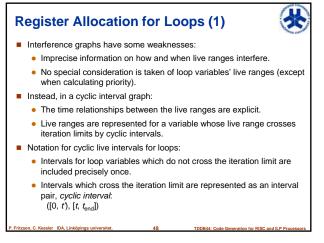

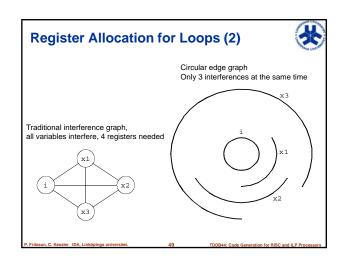

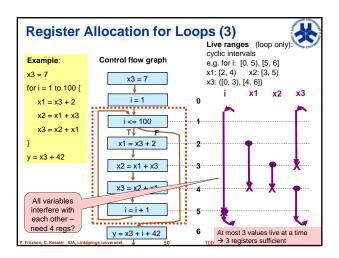

#### **Interference Graphs**

- The live ranges of two variables interfere if their intersection is not empty.

- Each live range builds a node in the interference graph (or conflict graph)

- If two live ranges interfere, an edge is drawn between the nodes.

- Two adjacent nodes in the graph can not be assigned the same reaister.

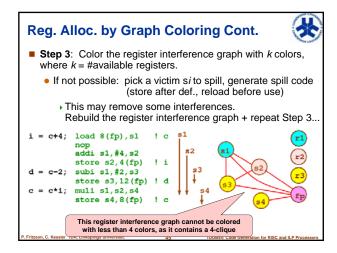

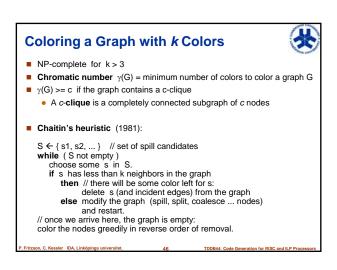

#### Register Allocation vs Graph Coloring

- Register allocation can be compared with the classic coloring problem.

- That is, to find a way of coloring with a maximum of *k* colors - the interference graph which does not assign the same color to two adjacent nodes.

- k = the number of registers.

- On a RISC-machine there are, for example, 16 or 32 general registers. Certain methods use some registers for other tasks. e.g., for spill code.

- Determining whether a graph is colorable using *k* colors is NP-complete for k>3

- In other words, it is unmanageable always to find an optimal solution.