Linköping Studies in Science and Technology

Dissertation No. 1089

## Analysis and Optimisation of Distributed Embedded Systems with Heterogeneous Scheduling Policies

by

**Traian Pop**

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

Linköping 2007

# Analysis and Optimisation of Distributed Embedded Systems with Heterogeneous Scheduling Policies

© 2007 Traian Pop

ISBN 978-91-85715-27-5 ISSN 0345-7524 PRINTED IN LINKÖPING, SWEDEN BY LIU-TRYCK COPYRIGHT © 2007 TRAIAN POP

# To Ruxandra

## Abstract

The growing amount and diversity of functions to be implemented by the current and future embedded applications (like, for example, in automotive electronics) have shown that, in many cases, time-triggered and event-triggered functions have to coexist on the computing nodes and to interact over the communication infrastructure. When time-triggered and event-triggered activities have to share the same processing node, a natural way for the execution support can be provided through a hierarchical scheduler. Similarly, when such heterogeneous applications are mapped over a distributed architecture, the communication infrastructure should allow for message exchange in both time-triggered and event-triggered manner in order to ensure a straightforward interconnection of heterogeneous components.

This thesis studies aspects related to the analysis and design optimisation for safety-critical hard real-time applications running on hierarchically scheduled distributed embedded systems. It first provides the basis for the timing analysis of the activities in such a system, by carefully taking into consideration all the interferences that appear at run-time between the processes executed according to different scheduling policies. Moreover, due to the distributed nature of the architecture, message delays are also taken into consideration during the timing analysis. Once the schedulability analysis has been provided, the entire system can be optimised by adjusting its configuration parameters. In our work, the entire optimisation process is directed by the results from the timing analysis, with the goal that in the end the timing constraints of the application are satisfied.

The analysis and design methodology proposed in the first part of the thesis is applied next on the particular category of distributed systems that use FlexRay as a communication protocol. We start by providing a schedulability analysis for messages transmitted over a FlexRay bus, and then by proposing a bus access optimisation algorithm that aims at improving the timing properties of the entire system.

For all the problems that we investigated, we have carried out extensive experiments in order to measure the efficiency of the proposed solutions. The results have confirmed both the importance of the addressed aspects during system-level design, and the applicability of our techniques for analysing and optimising the studied systems.

## Acknowledgements

THE PUBLICATION OF THIS THESIS would have not been possible without the generous support and patient guidance of my advisors: Prof. Petru Eles and Prof. Zebo Peng. I am convinced that nobody else except for them would have done a better job in supervising my PhD studies. After all these years, I am still amazed by Petru's energy and dedication for his work, and I constantly admire his thoroughness when approaching a problem. Also, I have always appreciated Zebo's managing skills, by fully enjoying the freedom he has often allowed us in our work.

The working environment here at IDA<sup>1</sup> is probably one of the best I'll ever experience in my life. To every staff member who contributed in one way or another to the smooth publication process of this thesis, a sincere "thank you".

My ESLAB colleagues, past and present, deserve a special mention for being some of my closest friends during the last years. I would have never enjoyed my PhD studies so much if it weren't for them.

I would also like to thank the members of the IDA<sup>2</sup> group in Braunschweig, Germany, for their hospitality during my visit to their laboratory in November 2004. The close contact with their work has given me a better understanding for some of the topics presented in this thesis.

Naturally, a big influence on the person that I am today is coming from my parents and my sister. I hope that my current achievements will lighten their lives and bring them the feelings of satisfaction that they truly deserve.

In the end, I would like to dedicate this thesis to my wife, Ruxandra, as a small token of appreciation for her patience and for the joy she brings into my life.

Thank you all, Traian Pop

<sup>1.</sup> Institutionen för Datavetenskap

<sup>2.</sup> Institut für Datantechnik und Kommunicationsnetze

# Contents

| 1.  | Introduction                                     | 1  |

|-----|--------------------------------------------------|----|

|     | 1.1. Design Flow of Distributed Embedded Systems | 2  |

|     | 1.2. Heterogeneous ET/TT Systems                 | 5  |

|     | 1.2.1. Event/Time-Triggered Task Execution       | 5  |

|     | 1.2.1.1.Event-Triggered Tasks                    | 5  |

|     | 1.2.1.2.Time-Triggered Tasks                     | 7  |

|     | 1.2.1.3.Task Execution for Heterogeneous         |    |

| Tir | ne/Event-Triggered Systems                       | 8  |

|     | 1.2.2. Static/Dynamic Communication              | 9  |

|     | 1.2.2.1.Dynamic (DYN) Communication              | 10 |

|     | 1.2.2.2.Static (ST) Communication                | 11 |

|     | 1.2.2.3.Heterogeneous ST/DYN Protocols           | 14 |

|     | 1.2.3. Distributed Embedded Systems with         |    |

| He  | terogeneous Scheduling Policies                  | 15 |

|     | 1.3. Related Work                                | 17 |

|     | 1.3.1. System Level Design                       | 17 |

|     | 1.3.2. Scheduling and Schedulability Analysis of |    |

| Re  | al-Time Systems                                  | 18 |

|     | 1.3.3. Communication in Real-Time Systems        | 21 |

|     | 1.4. Thesis Contributions                        | 24 |

|     | 1.5. Thesis Overview                             | 25 |

| 2.  | System Model                                     | 27 |

|     | 2.1. Hardware Architecture                       | 27 |

|     | 2.2.Bus Access                                           | 28 |

|-----|----------------------------------------------------------|----|

|     | 2.3. Software Architecture                               | 29 |

|     | 2.4. Application Model                                   | 31 |

| 3.  | Scheduling and Schedulability Analysis                   | 35 |

|     | 3.1. Problem Formulation                                 | 35 |

|     | 3.2. Holistic Scheduling                                 | 37 |

|     | 3.3.Schedulability Analysis of Event-Triggered Task      |    |

| Set | ts                                                       | 38 |

|     | 3.4. Schedulability Analysis of Event-Triggered          |    |

| Act | tivities under the Influence of a Static Cyclic Schedule | 43 |

|     | 3.5. Static Cyclic Scheduling of Time-Triggered          |    |

| Act | tivities in a Heterogeneous TT/ET Environment            | 47 |

|     | 3.6. Experimental Results                                | 57 |

| 4.  | Design Optimisation                                      | 61 |

|     | 4.1. Specific Design Optimisation Problems               | 62 |

|     | 4.1.1. Scheduling Policy Assignment                      | 62 |

|     | 4.1.2. Mapping                                           | 64 |

|     | 4.1.3. Bus Access Optimisation                           | 66 |

|     | 4.2. Exact Problem Formulation                           | 67 |

|     | 4.3. Design Optimisation Strategy                        | 68 |

|     | 4.3.1. Building An Initial Configuration                 | 69 |

|     | 4.3.2. Mapping and Scheduling Policy Assignment          |    |

| He  | uristic                                                  | 70 |

|     | 4.3.3. Bus Access Optimisation                           | 73 |

|     | 4.4. Experimental Results                                | 74 |

| 5.  | The FlexRay Communication Protocol                       | 79 |

|     | 5.1. The Media Access Control for FlexRay                | 80 |

| 6.  | Timing Analysis of FlexRay Messages                      | 85 |

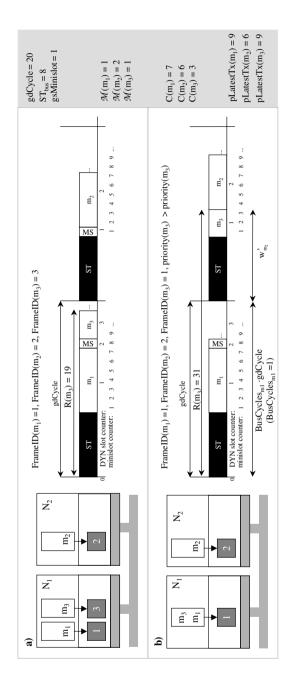

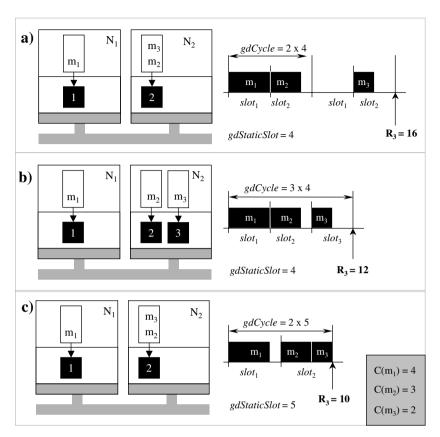

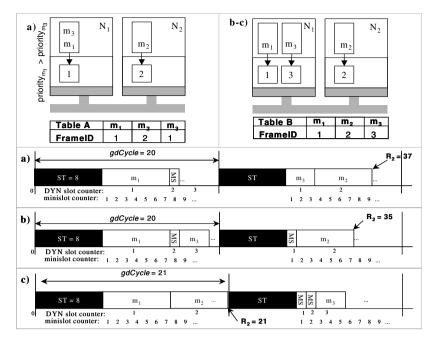

|     | 6.1. Schedulability Analysis of DYN Messages             | 86 |

|     | 6.1.1. Optimal Solution for $BusCycles_m$                | 91 |

|     | 6.1.2. Optimal Solution for $w_m$                        | 95 |

|     |                                                          |    |

| 6.1.3. Heuristic Solution for $BusCycles_m$            | 95  |

|--------------------------------------------------------|-----|

| 6.1.4. Heuristic Solution for $w_m$ '                  | 97  |

| 6.2. Holistic Schedulability Analysis of FPS Tasks and |     |

| DYN Messages                                           | 97  |

| 6.3. Analysis for Dual-channel FlexRay Bus             | 99  |

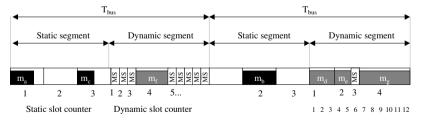

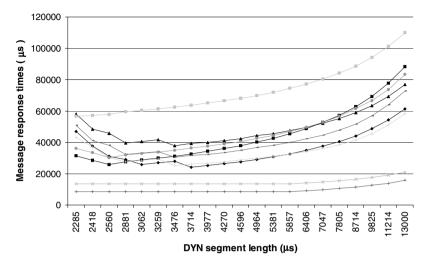

| 6.4. Evaluation of Analysis Algorithms                 | 100 |

| 6.5. Conclusions                                       | 104 |

| 7.                                      | <b>Optimisation of the FlexRay Bus Access</b>        |              |  |  |  |  |  |  |  |

|-----------------------------------------|------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| Sc                                      | heme                                                 | 105          |  |  |  |  |  |  |  |

|                                         | 7.1. Introduction                                    | 105          |  |  |  |  |  |  |  |

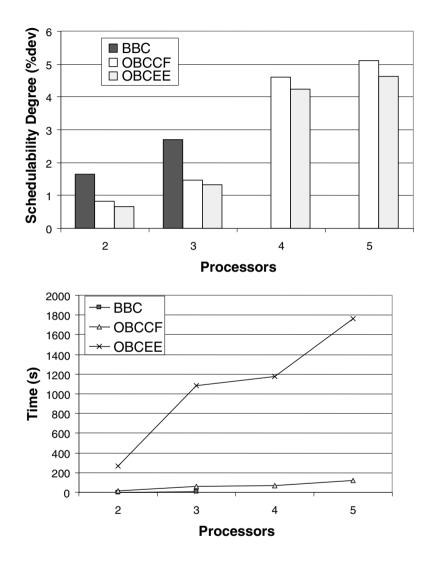

| 7.2. The Basic Bus Configuration (BBC)  |                                                      |              |  |  |  |  |  |  |  |

|                                         | 7.3. Heuristic for Optimised Bus Configuration (OBC) | 111          |  |  |  |  |  |  |  |

|                                         | 7.3.1. Curve-fitting Based Heuristic for DYN         |              |  |  |  |  |  |  |  |

| Segment Length                          |                                                      |              |  |  |  |  |  |  |  |

| 7.4. Simulated Annealing Based Approach |                                                      |              |  |  |  |  |  |  |  |

|                                         | 7.5. Evaluation of FlexRay Bus Optimisation          |              |  |  |  |  |  |  |  |

| Heuristics                              |                                                      |              |  |  |  |  |  |  |  |

|                                         | 7.6. Conclusions                                     | 121          |  |  |  |  |  |  |  |

| 8.                                      | <b>Conclusions and Future Work</b>                   |              |  |  |  |  |  |  |  |

|                                         | 8.1. Conclusions                                     |              |  |  |  |  |  |  |  |

|                                         | 8.2. Future Work                                     | 124          |  |  |  |  |  |  |  |

|                                         | Appendix A: List of Notations                        |              |  |  |  |  |  |  |  |

|                                         | Appendix B: Bin-Covering Heuristics                  |              |  |  |  |  |  |  |  |

|                                         | Appendix C: Real Life Example                        |              |  |  |  |  |  |  |  |

|                                         | Appendix D: List of Figures                          | $135 \\ 139$ |  |  |  |  |  |  |  |

|                                         | References                                           | 143          |  |  |  |  |  |  |  |

## Chapter 1 Introduction

THIS THESIS DEALS with specific issues related to the system-level design of distributed real-time embedded systems implemented with mixed, event-triggered (ET) and time-triggered (TT) task sets that communicate over bus protocols consisting of both static (ST) and dynamic (DYN) phases. We have focused on the scheduling of heterogeneous TT/ET systems and we have studied the factors which influence the efficiency of the scheduling process. We have also identified several optimisation problems specific for this type of heterogeneous systems, and we have approached these problems in the context of design optimisation heuristics.

This chapter starts by presenting the framework of our thesis, namely the area of distributed embedded real-time systems. We make a short introduction to event-triggered and time-triggered execution of tasks, as well as a brief description of static and dynamic transmission of messages. We introduce both homogeneous and heterogeneous TT/ET distributed embedded systems and we focus on the later ones, as they constitute the motivation behind this work.

Analysis and design of distributed embedded systems has been and will be a prolific area of research, considerably boosted by the variety of communication protocols which are involved. This thesis is not the first and

definitely not the last contribution in this area. In Section 1.3, the reader is acquainted with other work related to the one presented in our thesis, while in Section 1.4 we outline our contributions to the field of analysis and design of embedded real-time systems.

Finally, Section 1.5 is a feed forward to the following chapters.

## 1.1 Design Flow of Distributed Embedded Systems

Today, *embedded systems* find their place in more and more applications around us, starting with consumer electronics and appliances and ending with safety critical systems in applications such as aerospace/avionics, railway, automotive industry, medical equipment, etc. Quite often, such systems are also *real-time systems*, as they are constrained to perform certain tasks in a limited amount of time; failure to comply with the timing requirements leads to consequences whose gravity can vary from almost imperceptible loss of quality in an MPEG decoder, up to catastrophic events, like fatal car crashes when braking and air-bag systems fail to react in time. Depending on the nature of the timing constraints, real-time systems can be classified into *soft* real-time systems, in which deadlines can be occasionally missed without the system reaching an intolerable state, and *hard* real-time systems, in which missing a deadline is intolerable because of its possible consequences [Kop97]. This thesis focuses on hard real-time systems.

Designing a hard real-time embedded system requires procedures for guaranteeing that all deadlines will be met. If such guarantees cannot be provided, then the system is considered *unschedulable* and most likely, its implementation will not meet the requirements in terms of timeliness.

The continuous increase in range and number of applications entailing the use of embedded systems [Tur99] is closely followed by an increase in complexity of the applications themselves. Complex environments need more and more complex control embedded systems. The growing complexity of real-time embedded systems is also considerably increased by their heterogeneous nature, which goes along several dimensions, like:

- applications can be data or control intensive;

- the system functionality implies both hard and soft timing requirements;

- the controlled environment can generate discrete or continuous stimuli;

- components inside an embedded computer system can interact among themselves using different synchronisation mechanisms;

- hardware implementations are based on heterogeneous architectures in which one can find application-specific instruction processors (ASIPs), digital signal processors (DSPs), general purpose processors, protocol processors, application-specific integrated circuits (ASICs), field-programmable gate arrays (FPGAs), etc., all organised in various topologies and interconnected by diverse shared buses, point-to-point links or networks;

- the system includes both analog and digital components.

In this thesis, we have studied another dimension of heterogeneity, resulted from the two different approaches to the design of real-time embedded systems:

- the *time-triggered* approach, in which the processing and communication activities are initiated at predetermined points in time;

- the *event-triggered* approach, in which activities happen when a significant change of state in the system occurs.

As we will see in Chapter 2, the systems which we consider support both time-triggered and event-triggered processing and communication activities.

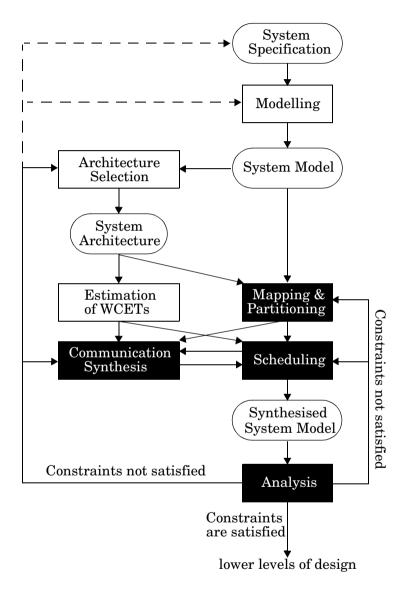

In Figure 1.1 we present a system-level design flow (adapted from [Ele02]) that starts from a high-level system specification, which may be expressed in several languages, including natural language. The system specification is later refined into an abstract formal model (which can be captured in one or several modelling languages). Starting from the system model, the methodology follows a design exploration stage in which various system architectures are selected, different ways to map the functionality on the available resources are evaluated, and several alternatives for scheduling and synthesis of the communication parameters are examined,

Figure 1.1: System Level Design Flow

so that in the end, the resulted model of the system will meet the requirements imposed for the current design.

In Figure 1.1 we marked with dark rectangles the phases in the design process which are covered in this thesis. First, we developed a method for scheduling and schedulability analysis of the activities in a heterogeneous TT/ET embedded system. This analysis method is then used for guiding the design process, and in particular we concentrated on the problems of *mapping* of functionality, *communication synthesis* and the specific aspect of *partitioning* the functionality into TT and ET activities.

## 1.2 Heterogeneous ET/TT Systems

In this thesis, we consider heterogeneous embedded systems in the sense that they consist of both time-triggered (TT) and event-triggered (ET) activities. In this section, we present the characteristics of such activities, the typical mechanisms used for implementation and the advantages and disadvantages inherent to each approach.

## 1.2.1 EVENT/TIME-TRIGGERED TASK EXECUTION

We start by describing first the execution mechanism of tasks in an ET and then in a TT system. In this thesis we consider that the functionality of the system is decomposed into a set of interacting tasks (2.4). A *task* is defined as "a computation that is executed by the CPU in a sequential fashion" [But97].

## 1.2.1.1 EVENT-TRIGGERED TASKS

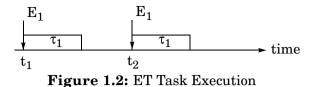

In the event-triggered approach, the execution of a task is initiated by the occurrence of a certain event which is related to a change in the system state. For example, in Figure 1.2, task  $\tau_1$  is initiated by event  $E_1$  which appears at times  $t_1$  and  $t_2$ . If the resources needed by task  $\tau_1$  are available at moment  $t_1$  (for example, the CPU is idle), then task  $\tau_1$  starts its execution. The mechanism behaves similarly at moment  $t_2$ .

Usually, the system functionality is composed of several tasks and their execution might lead to resource conflicts, like in the case when two tasks are simultaneously ready for execution and only one of them can make use of the processing capabilities of the system. Typically, such conflicts are solved by assigning priorities to tasks and executing the task with the highest priority. We present below one of the simplest and most common approaches, the fixed priority approach, in which the priorities are statically assigned off-line to tasks and do not change at run time.

In order to implement a fixed priority policy for task execution, a realtime kernel has a component called *scheduler* which has two main responsibilities:

- to maintain/update the prioritised queue of ready tasks;

- to select from the queue and execute the ready task with the highest priority.

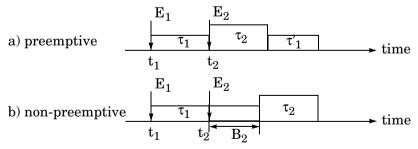

The timeline in Figure 1.3 presents how two conflicting ET tasks are executed by such a real-time kernel. In the first case, the kernel implements a preemptive policy for task execution. When task  $\tau_2$  is initiated by the occurrence of event  $E_2$ , task  $\tau_1$  will be interrupted because it has a lower priority than the priority of task  $\tau_2$ . Task  $\tau_1$  is placed in the ready queue and it will resume its execution only after task  $\tau_2$  finishes. In the

Figure 1.3: Concurrent ET Execution of Tasks

second case, the execution is non-preemptive and task  $\tau_2$  has to wait until task  $\tau_1$  finishes execution. In this case, even if task  $\tau_2$  has a higher priority than task  $\tau_1$ , it will be blocked for an amount of time  $B_2$  and it will have to stay in the ready queue until a subsequent activation of the scheduler will find the processor available.

The advantages of the event-triggered approach are its flexibility and an efficient usage of the available resources. However, taking into consideration the overheads related to task switching, scheduler activation, etc. considerably increases the difficulty of the schedulability analysis for such types of systems.

## 1.2.1.2 TIME-TRIGGERED TASKS

In a time-triggered system, the execution of tasks is initiated at pre-determined moments in time. The main component of the real-time kernel is the time interrupt routine and the main control signal is the clock of the system. The information needed for task execution is stored in a data structure called *schedule table*, where each task has a pre-assigned start time. The schedule table is obtained through a static scheduling algorithm, which is executed off-line and which eliminates the possible conflicts between tasks by imposing appropriate start times.

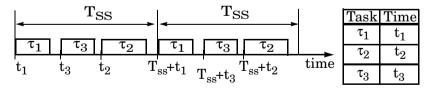

For example, in Figure 1.4, we consider three periodic tasks running on a single processor, each task being executed with period *T*. The schedule table on the right side of the figure shows that the executions of the three tasks  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are started at moments  $t_1$ ,  $t_2$  and  $t_3$ . Each start time in the table is computed off-line in such a way that the execution of a task is finished before the next start time stored in the schedule table. After a certain

Figure 1.4: Time Triggered Execution of Tasks

time  $T_{SS}$ , called the period of the static cyclic schedule, the kernel performs again the same sequence of decisions.

The period  $T_{SS}$  is computed as the least common multiple of the periods of the individual tasks in the system. The case presented above is a very particular one, as all three tasks have the same period *T*, which gives a perfectly harmonised system, and therefore  $T_{SS} = T$ . In the general case, one may notice that the size of the schedule table increases substantially if the task periods are not harmonised.

Also, a time-triggered system based on a static schedule table has a low flexibility and is usually inappropriate for dynamic environments for which it provides an inefficient processor utilisation.

However, the time-triggered approach has several important advantages. Being highly predictable, deterministic, easier to be validated and verified, it is particularly suitable for safety-critical applications [Kop97].

## 1.2.1.3 TASK EXECUTION FOR HETEROGENEOUS TIME/EVENT-TRIGGERED SYSTEMS

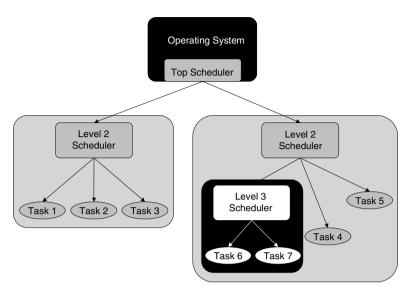

When time-triggered and event-triggered activities have to share the same processing node, the operating system for that node has to support concurrent execution of both categories of tasks. A natural way for such an execution support can be provided through a hierarchical scheduler.

The activities on a processing node that uses a hierarchical scheduler are tasks in one of the following categories:

- schedulers that implement a scheduling policy each;

- application tasks that implement a part of the system functionality.

The execution of each application task is controlled by a scheduler. The execution of each scheduler is controlled by another scheduler, or, in the case of the top scheduler, by the operating system itself. Such an organisation leads to a hierarchy of schedulers, each with their own scheduling pol-

Figure 1.5: Hierarchy of Schedulers

icies and their own set of tasks to control (see Figure 1.5 for an example of such a hierarchy).

## 1.2.2 STATIC/DYNAMIC COMMUNICATION

The previous section presented activation mechanisms of tasks in a realtime system. We continue with a similar discussion but in the context of communication activities in architectures based on broadcast buses.

There are two main features characteristic to broadcast buses:

- all nodes connected to the communication channel (the bus) receive the same messages; and

- only one node can send messages at a time on the bus. This feature enforces the usage of a bus arbitration method.

In the following sub-sections, we discuss two approaches to communication in distributed real-time systems:

- 1. Dynamic communication (DYN), in which the communication activities are triggered dynamically, in response to an event.

- 2. Static communication (ST), in which the communication activities are

triggered at pre-determined moments in time. For such a case, each node in the system knows (from design time) exactly when and which messages are sent on the bus, as well as how long their transmission takes.

## **1.2.2.1 DYNAMIC COMMUNICATION**

In the case of DYN communication, the trigger which initiates the process of sending a message is the generation of the message itself (by the sending task).

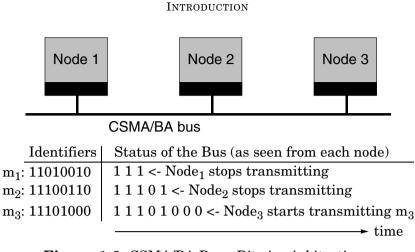

We will give an example of how messages are sent over the CAN bus, which is one of the most used event-triggered communication approaches ([Bos91]). The CAN protocol is based on a CSMA/BA (Carrier Sense Multiple Access with Bitwise Arbitration) arbitration policy, and for this purpose each message in the system has a unique identifier associated to it. Whenever the communication controller in a node receives a message to be sent on the bus, it will have first to wait until the bus is available. When no activity is identified on the bus any more, the message will be sent, preceded by its unique identifier. The identifier of a message acts like a priority, in the sense that if there are several nodes which transmit at the same time on the bus, only the message with the highest priority will go through and the other ones will have to wait the next moment when the bus becomes available. The collisions between messages whose transmission start at the same time are avoided by a non-destructive bitwise arbitration based on the message identifier.

The collision avoidance mechanism implemented with bitwise arbitration is illustrated in Figure 1.6, where three messages  $m_1$ ,  $m_2$  and  $m_3$  are simultaneously generated on three different nodes. All three messages start being transmitted at the same time. Each message is preceded on the bus by the sequence of several bits representing its priority. The bus is usually hardwired in such a way that it will always have the same value in the case a collision appears. This means that if two nodes transmit two different bits simultaneously, then only the *dominant* bit will be sensed on the bus. The example in Figure 1.6 considers the case where the dominant bit is 1, and as a result, after 3 bits have been sent on the bus, the first node

Figure 1.6: CSMA/BA Bus - Bitwise Arbitration

gives up the transmission, as it sensed a higher priority on the bus than the one sent by itself. The second node gives up after transmitting 5 bits. Having the highest value for the identifier, the message transmitted by the third node will go undeterred on the bus, while messages  $m_1$  and  $m_2$  will be resent only after transmission of  $m_3$  will finish (of course, the bus access mechanism will decide again which of the remaining messages goes first).

## 1.2.2.2 STATIC COMMUNICATION

In Section 1.2.1.2 we presented the time-triggered execution of tasks. Similarly, static (ST) communication activities are initiated at predetermined moments of time. A consistent behaviour of such a distributed multiprocessor time-triggered system requires that the clocks in all the nodes in the system are synchronised to provide a global notion of time [Kop97]. Such a synchronisation can be efficiently achieved through the communication protocol.

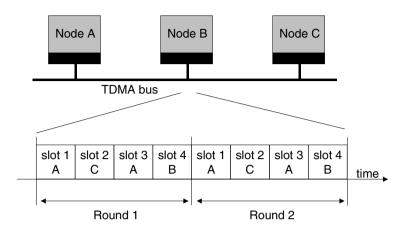

In this section, we detail the time-triggered communication mechanism as it appears in the case of a TDMA bus. As we already mentioned, in the case of a TDMA bus the bandwidth is divided into timeslots and each such slot is assigned off-line to a node in the system. During its timeslot, a node has the exclusive right to send messages on the bus. At run-time, if a node

Figure 1.7: TDMA Bus

has a message to send, it will have to wait until the system time has advanced to the start of its pre-assigned slot. The periodic sequence in which the timeslots are ordered represents a TDMA round.

For example, in Figure 1.7, one can see a distributed system with three nodes connected to a TDMA bus. The bus cycle is composed of four time slots, each slot being associated to a node.  $Node_A$ , for example, can send messages only during  $slot_1$  and  $slot_3$  of each TDMA round,  $Node_B$  can send only during  $slot_4$ , while  $Node_C$  can send only during the second slot of each round. In this way it is guaranteed that only one node transmits on the bus at a time. The TDMA round in the example consists of the sequence of slots 1, 2, 3 and 4.

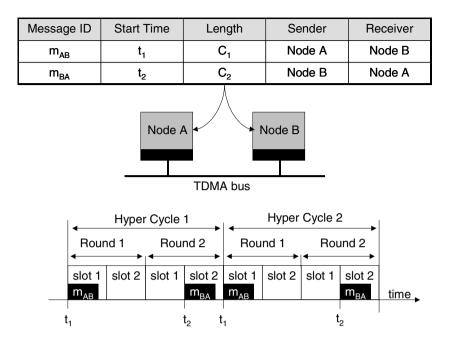

A typical TDMA based communication protocol is the Time-Triggered Protocol (TTP) [TTP01C]. In the case of TTP, every node stores locally the information related to each of the messages in the system: sender/ receiver, starting time of transmission, message length, etc. A node will send a message on the bus whenever the global current time reaches one of the start time values which are stored locally. For example, in Figure 1.8,  $Node_A$  starts sending a message  $m_{AB}$  at time  $t_1$  relative to the start of each bus round, during its pre-assigned slot in the first round of the schedule, according to the information stored locally. At the same time, the commu-

Figure 1.8: Statically Scheduled TT Communication

nication controller in  $Node_B$  will know from its own local table that at time  $t_1$  it will have to start reading message  $m_{AB}$ . At time  $t_2$ , another message is scheduled to be transmitted on the bus from  $Node_B$  towards  $Node_A$ . The static schedule illustrated in Figure 1.8 expands along two bus cycles, called *rounds*, and the sequence of such two consecutive rounds forms a *hyper cycle*. The static schedule stored locally in each node is repeated periodically with a period equal to the length of such a hyper cycle.

It is largely accepted that the static properties inherent to the TDMA communication considerably diminish the flexibility of the system. Unless bandwidth is reserved from the design time, adding another sending node in the system requires a reconfiguration of the bus round, which usually triggers many other updates and validations of the system design.

However, the determinism associated with the TDMA communication has several major advantages: timing properties of the system are easily

| •            |         |         |               |         |         |              |         |         |         |               |  |         |         |         |

|--------------|---------|---------|---------------|---------|---------|--------------|---------|---------|---------|---------------|--|---------|---------|---------|

| Static phase |         |         | Dynamic phase |         |         | Static phase |         |         |         | Dynamic phase |  |         |         |         |

|              |         |         |               |         |         |              |         |         |         |               |  |         |         |         |

| ST slot      | ST slot | ST slot | ,             | DYN msg | DYN msg |              | ST slot | ST slot | ST slot | ST slot       |  | DYN msg | DYN msg | DYN msg |

Communication Cycle

Figure 1.9: Heterogeneous ST/DYN Communication Cycle

guaranteed, system composability is straightforward when extensions are planned, etc.[Kop97].

## **1.2.2.3 HETEROGENEOUS STATIC/DYNAMIC PROTOCOLS**

Nowadays, protocols which support both static and dynamic communication are being developed and placed on the market. Examples in this sense are Flexray [Fuh00], WorldFIP [Wor03] and FTT-CAN [Ple92]. The main motivation behind their appearance was to provide a bus support which combines the advantages of both ST and DYN approaches into powerful and versatile protocols.

In order to avoid the interferences between ST and DYN communication, interference that may have a negative impact on the properties of the ST messages, such a mixed protocol has to enforce a temporal isolation between the two types of traffic. The most common solution is based on the so called *communication cycle* that is split into ST and DYN phases that repeat periodically: TT messages are sent during a ST phase, while ET messages are sent during a DYN phase ([Raj93], [Ple92]).

In Figure 1.9, we present a generalised model of such a protocol, called Universal Communication Model (UCM [Dem01]), in which the communication cycle contains several *static* (ST) and *dynamic* (DYN) phases. A system based on such a protocol will send the ST messages during ST slots according to a pre-defined TDMA scheme and to an associated static schedule, while the DYN messages are packed on-line into frames and sent during the DYN phases according to an arbitration mechanism (like CSMA/BA [Bos91] or mini-slotting [ARI629]).

The Universal Communication Model allows for the modelling and exploration of a large range of mixed ST/DYN communication protocols for bus based systems. This is why in the first part of this thesis, we model the communication on the bus using UCM (Section 2.2).

## 1.2.3 DISTRIBUTED EMBEDDED SYSTEMS WITH HETEROGENEOUS SCHEDULING POLICIES

There has been a lot of debate in the literature on the suitability of the event-triggered paradigm as opposed to the time-triggered one, for implementation of real-time systems [Aud93], [Kop97], [Xu93]. Several arguments have been brought concerning composability, flexibility, fault tolerance, jitter control or efficiency in processor utilisation. The same discussion has also been extended to the communication infrastructure, which can also be implemented according to the time-triggered or event-triggered paradigm.

An interesting comparison of the TT and ET approaches, from a more industrial, in particular automotive, perspective, can be found in [Loc92]. Their conclusion is that one has to choose the right approach depending on the particularities of the scheduled tasks. This means not only that there is no single "best" approach to be used, but also that, inside a certain application the two approaches can be used together, some tasks being timetriggered and others event-triggered.

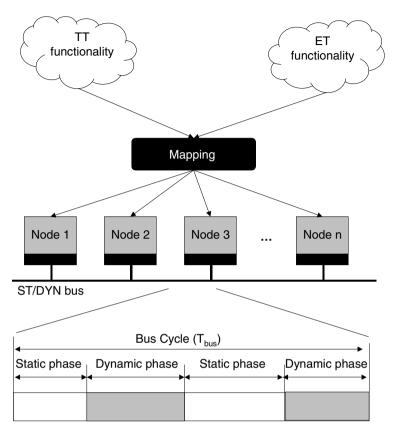

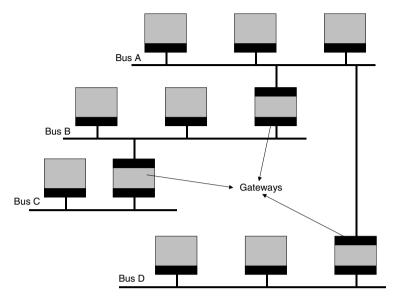

The growing amount and diversity of functions to be implemented by the current and future embedded applications (like for example, in automotive electronics [Koo02]) has shown that, in many cases, time-triggered and event-triggered functions have to coexist on the computing nodes and to interact over the communication infrastructure (see for example in Figure 1.10 the illustration of such a heterogeneous functionality mapped over a distributed architecture). When time-triggered and event-triggered activities have to share the same processing node, a natural way for the execution support can be provided through a hierarchical scheduler. Similarly, when such heterogeneous applications are mapped over a multiprocessor architecture, the communication infrastructure should allow for both

Figure 1.10: Heterogeneous TT/ET Distributed System

static and dynamic message exchange in order to ensure a straightforward interconnection of heterogeneous functional components.

Safety-critical hard real-time distributed applications running on such hierarchically scheduled multiprocessor architectures are difficult to analyse. Due to the hierarchical nature of the schedulers, various execution interferences have to be carefully accounted for during the timing analysis that determines the worst-case response times of the system activities. Moreover, due to the distributed nature of the architecture, message delays have to be taken into consideration during the analysis. Such an analysis is

further complicated by the particular characteristics of the communication protocol that mixes both static and dynamic transmission of messages.

In order to cope with the complexity of designing such heterogeneous embedded systems, only an adequate design environment can effectively support decisions leading in an acceptable time to cost-efficient, reliable and high performance solutions. Developing flexible and powerful tools for the design and analysis of such kind of heterogeneous systems represents the motivation behind the work presented in this thesis.

## 1.3 Related Work

This section presents an overview of the previous research in the area of analysis and system level design for distributed embedded systems. We concentrate in particular on scheduling and communication synthesis, with focus on the time-triggered and event-triggered aspects.

## 1.3.1 System level design

System level design methodology is continuously evolving [Mar00], from ad-hoc approaches based on human designer's experience, to hardware/ software codesign, and currently to platform-based design [Keu00] and function-architecture codesign [Bal97], [Dav99], [Lav99], [Tab00].

The design flow presented in Figure 1.1 illustrates only some of the main problems that appear during the system level phases of design. For a deeper insight into system level design aspects with focus on hardware/ software trade-offs, the reader is referred to the surveys in [Wol94], [Mic97], [Ern98], [San03], [Wol03], [Mar03] and [Wol06].

System modelling has received a lot of attention, as powerful computational models and expressive specification languages are needed in order to capture heterogeneous system requirements and properties at different levels of abstraction [Edw97], [Edw00], [Lav99], [Mul04]. Typical hardware architectures for embedded systems have evolved from simple ones (involving only one processor and one ASIC), to distributed and heterogeneous ones (involving multiprocessor architectures distributed over a large area or integrated on a single chip [Ben02]). Such an evolution has

directly increased the complexity of the problems related to architecture selection, mapping, partitioning and scheduling of functionality and has led to the apparition of new approaches like those proposed in [Bec98], [Bli98], [Dav99], [Lee99], [Wol97], [Yen97], [Hu03], [Jer04], [Nur04], [Thi04] and [Ben05].

## 1.3.2 Scheduling and schedulability analysis of Real-Time systems

Task scheduling and schedulability analysis have been intensively studied for the past decades. The complexity of the scheduling problems have been analysed in [Ull75], [Sta94]. The reader is referred to [Aud95], [Bal98] and [But05] for surveys on this topic.

A comparison of the two main approaches for scheduling hard real-time systems (i.e., *static cyclic scheduling* and *fixed priority scheduling*) can be found in [Loc92] and [Lön99].

The *static cyclic (non-preemptive) scheduling* approach has been long considered as the only way to solve a certain class of problems [Xu93]. This was one of the main reasons why it received considerable attention. Solutions for generating static schedules are often based on *list scheduling* in which the order of selection for tasks plays the most important role [Cof72], [Jor97] (see also 3.5). However, list scheduling is not the only alternative, and branch-and-bound algorithms [Jon97], [Abd99], mixed integer linear programming [Pra92], constraint logic programming [Kuc97], [Eke00], or evolutionary [Sch94] approaches have also been proposed.

For event-triggered tasks, in this thesis we are interested both in static and dynamic priority based scheduling policies. In our work we will focus our attention on *fixed priority scheduling* (FPS) and *earliest-deadline-first scheduling* (EDF). For both policies, determining whether a set of tasks is schedulable involves two aspects:

- 1. *The assignment of priorities* to system activities, i.e. what priority should be associated with each task and message in the system so that the task set is schedulable.

- 2. The schedulability test, which determines whether all activities in the

system will meet their deadlines under the current policy.

In the case of EDF scheduling, the priorities are assigned dynamically, at run-time, according to the criticality of each ready task, i.e. tasks that are closer to their deadline will receive higher priorities.

In the case of *fixed priority scheduling*, the priorities are associated to tasks off-line, before the system is deployed. In order to solve the problem of assigning priorities to system activities so that the system is schedulable, two main policies have been developed; they both work under restricted assumptions, i.e. the task set to be scheduled is composed of periodic and independent tasks mapped on a single processor:

- **a.** rate-monotonic (RM) [Liu73] which assigns higher priorities to tasks with shorter periods; it works under the constraint that task deadlines are identical with task periods.

- **b.** deadline-monotonic (DM) [Leu82] which assigns higher priorities to tasks with shorter relative deadlines; this policy assumes that task deadlines are shorter than task periods.

Under a particular set of restrictions regarding the system specification, such policies are optimal. However, if, for example, tasks are not independent, then the optimality does not hold any more for RM and DM policies. Therefore, in [Aud93], the authors proposed a priority assignment in the case of tasks with arbitrary release times. Their algorithm is of polynomial complexity in the number of tasks. However, for the case of multiprocessor/distributed hard real-time systems, obtaining an optimal solution for priority assignment is often infeasible, due to complexity reasons. A solution based on simulated annealing has been proposed in [Tin92], where the authors present an algorithm that simultaneously maps the tasks on processors and assigns priorities to system activities so that the resulted system is schedulable. In order to avoid the large amount of computation time required by such a general-purpose approach, an optimised priority assignment heuristic called HOPA has been suggested in [Gut95], where the authors iteratively compute deadlines for individual tasks and messages in the system, while relying on the DM policy to assign priorities to the tasks. Their algorithm has shown a better efficiency than the one proposed in [Tin92], both in quality and especially in speed, making it appropriate for being used inside a design optimisation loop that

requires many iterations. As an example, HOPA has been adapted for the design optimisation of multi-cluster distributed embedded systems [PopP03b].

As mentioned above, another main issue in the context of fixed priority scheduling is that of the schedulability tests. In this regard, there are two main approaches used:

- **a.** *utilisation based tests*, in which the schedulability criterion is represented by inequations involving processor utilisation and utilisation bounds. However, such approaches are valid only under restricted assumptions [Liu73], [Bin01], [Leu82], [And01].

- **b.** response time analysis, in which determining whether the system is schedulable or not requires first the computation of the worst-case response time of the tasks and/or messages. The worst case response time of an activity is represented by the longest possible time interval between the instant when that activity is initiated in the system and the moment when the same activity is finished. If the worst case response time resulted for each task/message is lower or equal than the associated deadline for that activity, then the system is schedulable.

Response time analysis is usually more complex but also more powerful than the utilisation based tests. The main reason for this is because response time analysis can take into consideration more factors that influence the timing properties of tasks and messages in a system.

The response time analysis in [Leh89] offers a necessary and sufficient condition for scheduling tasks running on a mono-processor system, under fixed priority scheduling and restricted assumptions (independent periodic tasks with deadlines equal with periods). In order to increase the range of target applications, relaxing such restrictive assumptions is necessary. Moreover, considering the effects of more and more factors that influence the timing properties of the tasks decreases the pessimism of the analysis by determining tighter worst case response times and leading to a smaller number of false negatives (which can appear when a system that is practically schedulable cannot be proven so by the analysis). Over the time, extensions have been offered to response time analysis for fixed priority scheduling by taking into account task synchronisation [Sha90], arbitrary deadlines [Leh90], precedence constraints between tasks [Pal99] and tasks

with varying execution priorities [Gon91], arbitrary release times [Aud93], [Tin94c], tasks which suspend themselves [Pal98], tasks modelling code with conditional branches [Bar98], tasks running on multiprocessor systems [Tin94a], [Pal98], etc. The fixed priority analysis has been also adapted for the situation when tasks are running under the EDF scheduling policy [Pal03].

In spite of the fact that the duality between different implementations of scheduling algorithms has been suggested in [Dob01a] and [Dob01b], where fixed priority scheduling has been adapted in such a way that it emulates static cyclic schedules which are generated off-line, the growing amount and diversity of functionality that has to be implemented on current embedded systems has led to the necessity for concurrently using several scheduling policies in the implementation of the application running on a given system. In [Gon03], the authors present the schedulability analysis for a hierarchical scheduling policy called EDF-within-fixed-priorities, that combines fixed priority and EDF scheduling. The assignment of server parameters for a two-level hierarchical scheduler based on a resource reservation approach has been studied in [Lip04]. In [Ric02] and [Ric03], the authors model the multiprocessor heterogeneous systems as components that communicate through event streams and propose a technique for integrating different local scheduling policies based on such event-model interfaces. Another compositional approach is presented in [Wan05], where the authors propose real-time interfaces and a component model that support incremental design of real-time systems.

### **1.3.3** Communication in Real-Time systems

Many safety-critical applications, following physical, modularity or safety constraints, are implemented using distributed architectures composed of several different types of hardware units (called nodes), interconnected in a network. For such systems, the communication between functions implemented on different nodes has an important impact on the overall system properties, such as performance, cost and maintainability.

There are several communication protocols for real-time networks. Among the protocols that have been proposed for in-vehicle communica-

tion, the Controller Area Network (CAN) [Bos91], the Local Interconnection Network (LIN) [LIN07], and SAE's J1850 [SAE94] are currently in use on a large scale [Nav05]. Moreover, only a few of the proposed protocols are suitable for safety-critical applications where predictability is mandatory [Rus01].

Communication activities can be triggered either dynamically, in response to an event (event-driven), or statically, at predetermined moments in time (time-driven). Therefore, on one hand, there are protocols that schedule the messages statically based on the progression of time, such as the SAFEbus [Hoy92], SPIDER [Min00], TTCAN [ISO02], and Time-Triggered Protocol (TTP) [Kop03]. The main drawback of such protocols is their lack of flexibility. On the other hand, there are communication protocols where message scheduling is performed dynamically, such as Byteflight [Ber03] introduced by BMW for automotive applications, CAN [Bos91], LonWorks [Eche07] and Profibus [Pro01].

A lot of work has been concentrated on coping with some of the disadvantages of the ST/DYN approaches and on trying to combine their advantages. For example, in [PopP01a], [PopP01b] and [PopP04b], the authors present a method for dealing with flexibility in TTP based systems by considering consecutive design stages in a so called *incremental design flow*. Similarly, a large number of schemes have been targeted at improving the real-time properties of communication protocols that may be cathegorised as extremely dynamic, like is the case of Ethernet [Fan05].

The aspects related to communication in real-time systems are receiving a continuously increasing attention in the literature. Building safety critical real-time systems requires consideration for all the factors that influence the timing properties of a system. For the case of distributed systems, in order to guarantee the timing requirements of the activities in the system, one has to also consider the effects of communication aspects like the communication protocol, bus arbitration, clock synchronisation, packaging of messages, characteristics of the physical layer, etc. Due to the variety of communication protocols, scheduling and schedulability analysis involving particular communication protocols has become a prolific area of research. Following the similar model as the one developed for determining task response times under rate monotonic analysis, message

#### INTRODUCTION

transmission times have been analysed for protocols like TTP bus [Kop92], Token Ring [Ple92], [Tab00], FDDI [Agr94], Profibus [Tov99], ATM [Erm97], [Han97] and CAN bus [Tin94b], [Dav07].

In the case of bus-based distributed embedded systems, one of the main directions of evolution for communication protocols is towards mixed protocols, which support both ST and DYN traffic. The proponents of the Time-Triggered Architecture showed that TTP can be enhanced in order to transmit event-triggered messages, while still maintaining time composability and determinism of the system, properties which are normally lost in event-triggered systems [Kop92]. A modified version of CAN, called Flexible Time-Triggered CAN [Alm99], [Alm02], and a similar extension for Ethernet called FTT-Ethernet [Ped05] have been provided under the Flexible Time-Triggered paradigm [Ped03], in which the communication cycles are divided into asynchronous and synchronous windows. Several other mixed communication protocols can be found in [Fuh00], [Wor03].

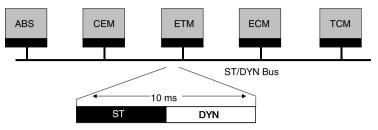

Following this trend, a large consortium of automotive manufacturers and suppliers has recently proposed such a hybrid type of protocol, namely the FlexRay communication protocol [Fle07]. FlexRay allows the sharing of the bus among static and dynamic messages, thus offering the advantages of both worlds. Due to its flexible properties and growing support from its target industry, FlexRay will possibly become the de-facto standard for in-vehicle communications. However, before it can be successfully deployed in applications that require predictability, timing analysis techniques are necessary to provide bounds for the message communication times [Nav05].

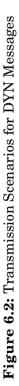

FlexRay is composed of static (ST) and dynamic (DYN) segments, which are arranged to form a bus cycle that is repeated periodically. The ST segment is similar to TTP, and employs a generalized time-division multiple-access (GTDMA) scheme. The DYN segment of the FlexRay protocol is similar to Byteflight and uses a flexible TDMA (FTDMA) bus access scheme.

Although researchers have proposed analysis techniques for dynamic protocols such as CAN [Tin95], TDMA [Tin94a], ATM [Erm97], Token Ring protocol [Str89], FDDI protocol [Agr94] and TTP [PopP00a], none of these analyses is applicable to the DYN segment in FlexRay. In

[Din05], the authors consider the case of a hard real-time application implemented on a FlexRay bus. However, in their discussion they restrict themselves exclusively to the static segment, which means that, in fact, only the classical problem of communication scheduling over a TDMA bus [PopP04a], [Ham05] is considered. The performance analysis of the Byteflight protocol, which is similar to the DYN segment of FlexRay, is discussed in [Cen04]. The authors, however, assume a very restrictive "quasi-TDMA" transmission scheme for time-critical messages, which basically means that the DYN segment would behave as an ST segment (similar to TDMA) in order to guarantee timeliness.

## 1.4 Thesis Contributions

The studies covered in this thesis consider distributed embedded systems implemented with heterogeneous, event-triggered and time-triggered task sets, which communicate over bus protocols consisting of both static and dynamic phases.

We have considered that the time-triggered activities are executed according to a static cyclic schedule, while the event-triggered activities follow a fixed priority scheduling or an EDF scheduling policy, which is preemptive for the execution of tasks and non-preemptive for the transmission of messages. For message exchange over the bus we have considered two heterogeneous communication protocols: UCM in the first part and FlexRay in the second part.

The main contributions of this thesis are threefold. First, we propose a holistic schedulability analysis for heterogeneous TT/ET task sets which communicate through mixed ST/DYN communication protocols [PopT02], [PopT03a]. Such an analysis presents two aspects:

- **a.** It computes the response times of the ET activities while considering the influence of a static schedule;

- b. It builds a static cyclic schedule for the TT activities while trying to

#### INTRODUCTION

minimise the response times of the ET activities.

Second, we show how the scheduling and schedulability analysis can be used inside a design optimisation loop in order to improve the timing properties of the system [PopT03b], [PopT05], [PopT07b].

Third, we apply the analysis and optimisation methodology developed in the first two steps on a particular case of systems that use FlexRay as a communication protocol [PopT06], [PopT07a], [PopT07c].

## 1.5 Thesis Overview

The remaining part of the thesis can be divided into two parts:

The first part (Chapters 2-4) deals with distributed embedded real-time systems that use heterogeneous scheduling policies. Chapter 2 presents the system model we used. In Chapter 3, we present our analysis method for deriving response times for all tasks and messages in such an embedded system. In Chapter 4, we first discuss some optimisation aspects which are particular to the studied systems, and then we define and solve the design optimisation problem that aims at improving the overall system schedulability.

The second part of the thesis (Chapters 5-7) concentrates on the same category of distributed embedded systems, but for the particular case when the communication protocol is FlexRay. First we introduce the specifics of FlexRay in Chapter 5. Then, in Chapter 6 we present the timing analysis that determines the worst-case response times of messages transmitted over a FlexRay bus. Following a similar line of thought like in the first part of the thesis, Chapter 7 aims again at improving the overall timing characteristics of the system by optimising the structure of the bus cycle.

Finally, in Chapter 8 we draw some conclusions and discuss possible research directions for the future.

# Chapter 2 System Model

IN THIS CHAPTER we present the system model that we use during scheduling and design optimisation. First, we briefly describe the hardware architecture and the structure of the bus access cycle. Then, we present our hierarchy of schedulers that implements the software architecture for a system which is able to run both event-triggered and time-triggered activities. The last part of this chapter presents the abstract representation which we use for modelling the applications that are assumed to implement the functionality of the system.

## 2.1 Hardware Architecture

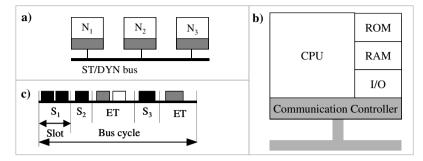

We consider architectures consisting of nodes connected by a unique broadcast communication channel. Each node consists of:

- a *communication controller* which controls the transmission and reception of both ST and DYN messages;

- a *CPU* for running the processes mapped on that particular node;

- *local memories* for storing the code of the kernel (ROM), the code of the processes and the local data (RAM); and

Figure 2.1: System Architecture

• I/O interfaces to sensors and actuators.

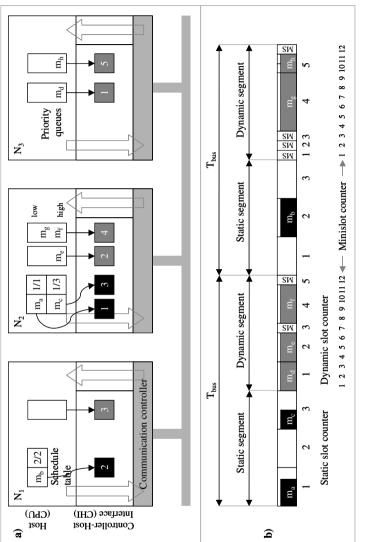

Such hardware architectures are common in applications such as automotive electronics and robotics. In Figure 2.1.a, we illustrate a heterogeneous distributed architecture composed of three nodes interconnected by a bus based infrastructure. The model considered for the processing nodes in the architecture is depicted in Figure 2.1.b.

## 2.2 Bus Access

Every node in the architecture has a communication controller that implements the static and dynamic protocol services. The controller runs independently of the node's CPU. In this first part of the thesis we model the heterogeneous bus access scheme using the Universal Communication Model [Dem01]

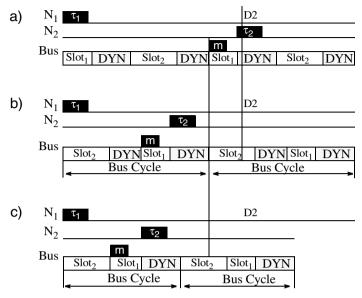

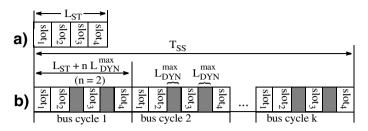

The bus access is organized as consecutive cycles, each with the duration  $T_{bus}$ . We consider that the communication cycle is partitioned into static (ST) and dynamic (DYN) phases (Figure 2.1.b).

- ST phases consist of time slots, and during a slot only the node associated to that particular slot is allowed to transmit ST messages. The transmission times of ST messages are stored in a schedule table.

- During a DYN phase, all nodes are allowed to send messages and the conflicts between nodes trying to send simultaneously are solved by

an arbitration mechanism which allows the transmission of the message with the highest priority. Hence, the DYN messages are organized in a prioritised ready queue.

## 2.3 Software Architecture

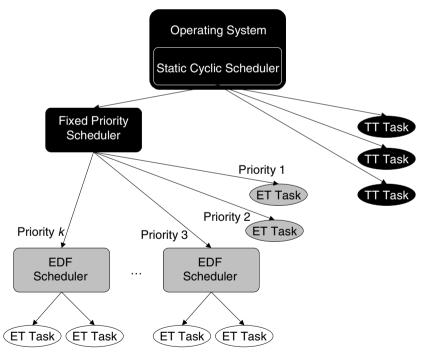

For the systems we are studying, we have designed a software architecture that runs on the CPU of each node. The main component of the software architecture is a real-time kernel. The real-time kernel contains three scheduler types organized *hierarchically* (Figure 2.2):

The top-level scheduler is a static cyclic scheduler (SCS), that is responsible for the activation of TT tasks and transmission of ST messages based on a schedule table, and for the activation of the FPS scheduler. As a consequence, TT tasks and ST messages are activated at predetermined points in time, and their execution/transmission is non-

Figure 2.2: Software Architecture

preemptable.

- 2. The second level in the hierarchy consists of a fixed-priority scheduler (FPS) that activates the execution of ET tasks and transmits DYN messages based on their priorities. It also activates the EDF schedulers that are described below. Tasks and messages scheduled under FPS are initiated whenever a particular event is noted. We consider that the execution of ET tasks under the fixed priority scheduling is preemptable.

- 3. The third level in the hierarchy consists of a set of schedulers that follow the earliest-deadline-first (EDF) scheduling policy. In the case that on a node there are several activities that share the same priority inside the FPS scheduler on the second level, then their execution is controlled by such an EDF scheduler that activates ET tasks and sends DYN messages based on their deadlines. We consider that the execution of ET tasks under the EDF policy is preemptable.

From this point and throughout the rest of the thesis, we will use the terms "SCS tasks", "EDF tasks" or "FP tasks" whenever we want to emphasise the scheduling policy under which certain tasks are executed.

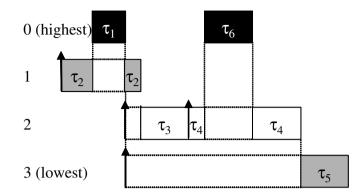

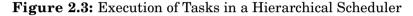

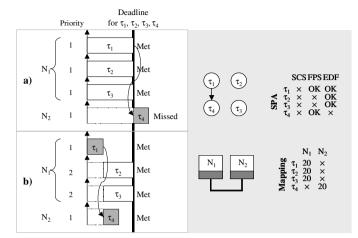

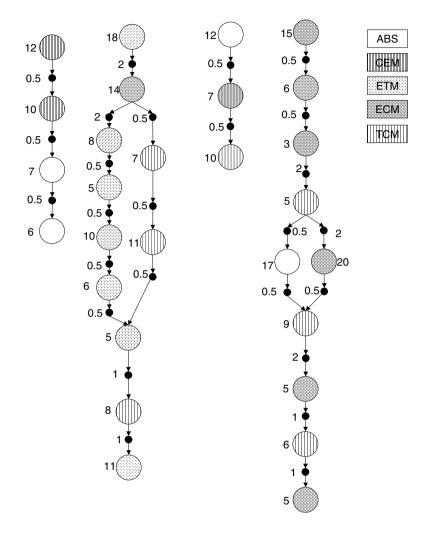

When several tasks are ready on a node, the task with the highest priority is activated, and preempts the other tasks. Let us consider the example in Figure 2.3, where we have six tasks sharing the same node. Tasks  $\tau_1$  and  $\tau_6$  are scheduled using SCS,  $\tau_2$  and  $\tau_5$  are scheduled using FPS, while tasks  $\tau_3$  and  $\tau_4$  are scheduled with EDF. The priorities of the FPS and EDF tasks are indicated in the figure. The arrival time of these tasks is depicted with an upwards pointing arrow. Under these assumptions, Figure 2.3 presents the worst-case response times of each task. The SCS tasks,  $\tau_1$  and  $\tau_6$ , will never compete for a resource because their synchronization is performed based on the schedule table. Moreover, since SCS tasks are non preemptable and their start time is off-line fixed in the schedule table, they also have the highest priority (denoted with priority level "0" in the figure). FPS and EDF tasks can only be executed in the *slack* of the SCS schedule table.

FPS and EDF tasks are scheduled based on their priorities. Thus, a higher priority task such as  $\tau_2$  will interrupt a lower priority task such as  $\tau_3$ . In order to integrate EDF tasks with FPS, we use the approach in [Gon03], by assuming that FPS priorities are not unique, and that a group of tasks having the same FPS priority on a processor are to be scheduled with EDF. Thus, whenever the FPS scheduler notices ready tasks that share the same priority level, it will invoke the EDF scheduler which will schedule those tasks based on their deadlines. Such a situation is present in Figure 2.3 for tasks  $\tau_3$  and  $\tau_4$ . There can be several such EDF priority levels within a task set on a processor. Higher priority EDF tasks can interrupt lower priority FPS tasks (as is the case with  $\tau_3$  and  $\tau_4$  which preempt  $\tau_5$ ) and EDF tasks. Lower priority EDF tasks, and SCS tasks.

TT activities are triggered based on a local clock available in each processing node. The synchronization of local clocks throughout the system is provided by the communication protocol.

## 2.4 Application Model

We model an application as a set of task graphs. Nodes in the graphs represent tasks, and arcs represent communication (and implicitly dependency) between the connected tasks. An edge from a task  $\tau_{ij}$  to  $\tau_{ik}$  indicates that the output of  $\tau_{ij}$  is the input of  $\tau_{ik}$ . The set of all tasks is denoted with  $\mathcal{P}$ . A task becomes ready after all its inputs have arrived and it issues its outputs when it terminates. A message will become ready after its sender task has finished, and becomes available for the receiver task after its transmission has ended.

- A task can belong either to the TT or to the ET domain. We consider that the scheduling policy for each task is known: TT tasks are scheduled using SCS, while ET tasks are scheduled under FPS and EDF.

- Communication between tasks mapped to different nodes is performed by message passing over the bus. Such a message passing is modelled as a communication task inserted on the arc connecting the sender and the receiver tasks. The communication time between tasks mapped on the same node is considered to be part of the task execution time. Thus, such a communication activity is not modelled explicitly. For the rest of the thesis, when referring to messages we consider only the communication activity over the bus.

- A message can belong either to the static (ST) or to the dynamic (DYN) domain. We consider that static messages are those sent during the ST phases of the bus cycle, while dynamic messages are those transmitted during the DYN phases.

- All tasks in a certain task graph belong to the same domain, either ET, or TT, which is called the domain of the task graph. The messages belonging to a certain task graph can belong to any domain (ST or DYN). Thus, in the most general case, tasks belonging to a TT graph, for example, can communicate through both ST and DYN messages. However, in this thesis we restrict our discussion to the situation when TT tasks communicate through ST messages and ET tasks communicate through DYN messages.

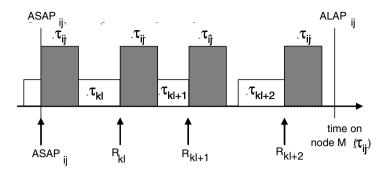

- Each task τ<sub>ij</sub> (belonging to the task graph Γ<sub>i</sub>) has a period T<sub>ij</sub>, and a deadline D<sub>ij</sub> and, when mapped on node Node<sub>k</sub>, it has a worst case execution time C<sub>ij</sub>(Node<sub>k</sub>). The node on which τ<sub>ij</sub> is mapped is denoted as M(τ<sub>ij</sub>). Each ET task also has a given priority Prio<sub>ij</sub>. Individual release times or deadlines of tasks can be modelled by introducing dummy tasks in the task graphs; such dummy tasks have an appropriate execution time and are not mapped on any of the nodes [Ele00a].

- All tasks  $\tau_{ij}$  belonging to a task graph  $\Gamma_i$  have the same period  $T_i$

Figure 2.4: Application Model Example

which is the period of the task graph. The period of a message is identical with that of the sender task. If communicating tasks are of different periods, they are combined into a larger graph capturing all task activations for the hyper-period (LCM of periods).

• We also consider that the size of each message m is given, which can be directly converted into communication time  $C_m$  on the particular bus, knowing the speed of the bus and the size of the frame that stores the message:

$$C_m = Frame\_size(m) / bus\_speed.$$

(2.1)

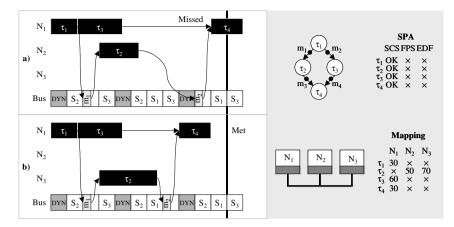

Figure 2.4 shows an application modelled as two task-graphs  $\Gamma_1$  and  $\Gamma_2$  mapped on two nodes, *Node*<sub>1</sub> and *Node*<sub>2</sub>. Task-graph  $\Gamma_1$  is time-triggered and task-graph  $\Gamma_2$  is event-triggered. Data-dependent tasks mapped on different nodes communicate through messages transmitted over the bus, which can be either statically scheduled, like  $m_1$  and  $m_2$ , or dynamic, like the messages  $m_3$  and  $m_4$ .

In order to keep the separation between the TT and ET domains, which are based on fundamentally different triggering policies, communication between tasks in the two domains is not included in the model. Technically, such a communication is implemented by the kernel, based on asyn-

#### Chapter 2

chronous non-blocking send and receive primitives (using proxy tasks if the sender and receiver are on different nodes). Such messages are typically non-critical and are not affected by hard real-time constraints.

# Chapter 3 Scheduling and Schedulability Analysis

In this chapter we present an analytic approach for computing worst-case task response times and worst-case message transmission delays for heterogeneous TT/ET systems.

# 3.1 Problem Formulation

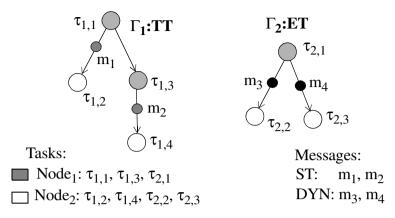

Given an application and a system architecture as presented in Chapter 2, the following problem has to be solved: construct a correct static cyclic schedule for the TT tasks and ST messages (a schedule which meets all time constraints related to these activities), and conduct a schedulability analysis in order to check that all ET tasks and DYN messages meet their deadlines. Two important aspects should be noticed:

- 1. When performing the schedulability analysis for the ET tasks and DYN messages, one has to take into consideration the interference from the statically scheduled TT tasks and ST messages.

- 2. Among the possible correct schedules for TT tasks and ST messages, it is important to construct one which favours, as much as possible, the schedulability of ET tasks and DYN messages.

Figure 3.1: Scheduling and Schedulability Analysis for Mixed TT/ET Distributed Embedded Systems

In the next sections, we will present the schedulability analysis algorithm proposed in [Pal98] for distributed real-time systems and we will show how we extended this analysis in order to consider the interferences induced by an existing static schedule. Section 3.2 presents a general view over our approach for the global scheduling and schedulability analysis of heterogeneous TT/ET distributed embedded systems. Section 3.3 describes the regular schedulability analysis for FPS and EDF tasks sharing the same resources, as developed in [Gon03]. Section 3.4 extends the schedulability analysis so that SCS tasks are taken into consideration when computing the response times of FPS and EDF activities. In Section 3.5 we present our complete scheduling algorithm, which statically schedules the TT activities while trying to minimise the influence of the TT activities onto the ET ones. The performance of our approach is evaluated in Section 3.6, where we present the experimental results. It has to be mentioned that our analysis is restricted, for the moment, to the model in which TT tasks communicate only through ST messages, while communication between ET tasks is performed by DYN messages. However, this is not an inherent limitation of our approach. For example, schedulability analysis of ET tasks communicating through ST messages has been presented in [PopP00b] and [PopP03a].

# 3.2 Holistic Scheduling

Figure 3.1 illustrates our strategy for scheduling and schedulability analysis of heterogeneous TT/ET distributed embedded systems: the activities to be scheduled are the TT and ET task graphs, consisting of TT tasks/ST messages and ET tasks/DYN messages respectively. The TT activities are statically scheduled and, as an output, a static cyclic schedule will be produced. Similarly, the worst case response times of the ET activities are determined using the schedulability analysis that will be described in detail in the following sections. As a result, the system is considered schedulable if the static schedule is valid and if the ET activities are guaranteed to meet their deadlines. For the case of a mixed TT/ET system, building a static cyclic schedule for the TT activities has to take into consideration both the characteristics of the mixed ST/DYN communication protocol and our assumption that execution of TT tasks is non-preemptible, while the execution of an ET task can be interrupted either by a TT task or by another ET task which has a higher priority. This means that the static schedule will have not only to guarantee that TT activities meet their deadlines, but also that the interference introduced from such a schedule will not increase in an unacceptable way the response times of ET activities. In conclusion, an efficient scheduling algorithm requires a close interaction between the static scheduling of TT activities and the schedulability analysis of the ET activities.

# 3.3 Schedulability Analysis of Event-Triggered Task Sets

In order to determine if a hierarchically scheduled system is schedulable, we used as a starting point the schedulability analysis algorithm for EDFwithin-FPS systems, developed in [Gon03]. In this section, we present our extension to this algorithm, which allows us to compute the worst case response times for the FPS and EDF activities when they are interfered by the SCS activities.

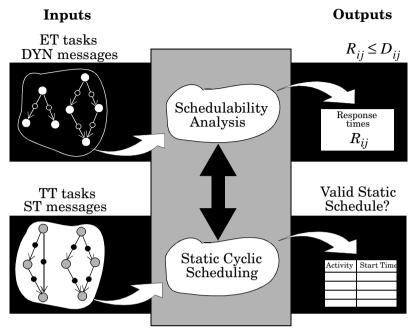

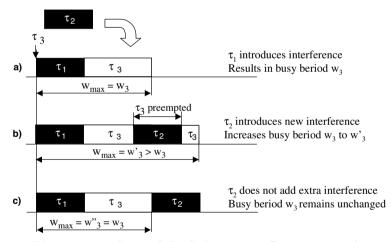

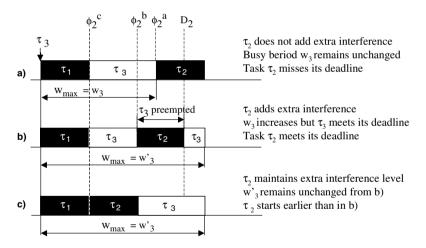

An ET task graph  $\Gamma_i$  is activated by an associated event which occurs with a period  $T_i$ . ET tasks (FPS or EDF) and DYN messages are modelled similarly, by considering the bus as a processing node and accounting for the non-preemptability of the messages during the analysis. Each activity  $\tau_{ij}$  (task or message) in an ET task graph has an offset  $\phi_{ij}$  which specifies the earliest activation time of  $\tau_{ij}$  relative to the occurrence of the triggering event. The delay between the earliest possible activation time of  $\tau_{ij}$  and its actual activation time is modelled as a jitter  $J_{ij}$  (Figure 3.2). The response time  $R^p_{ij}$  of the *p*-th job of a task  $\tau_{ij}$  is the time measured from the occurrence of the associated event until the completion of the *p*-th job of  $\tau_{ij}$ . For example, Figure 3.2 depicts the execution of two jobs for each of the tasks  $\tau_{ij}$  and  $\tau_{ij+1}$ . The worst-case response time  $R_{ij}$  of a task  $\tau_{ij}$  is the longest possible response time for that task, considering all its possible jobs:

$$R_{ii} = max(R^{p}_{ij}), \forall p \tag{3.1}$$

Similarly, each task  $\tau_{ii}$  has a best case response time  $R_{b,ii}$ :

$$R_{b,ij} = min(R^{p}_{ij}), \forall p$$

(3.2)

Offsets are the means by which dependencies among tasks can be modelled for the schedulability analysis. For example, if in Figure 3.2, task  $\tau_{ij+1}$  is data dependant on task  $\tau_{ij}$ , then such a relation can be enforced by associating to  $\tau_{ij+1}$  an offset  $\phi_{ij+1}$  which is equal or greater than the worst

Figure 3.2: Tasks with Offsets

case response time  $R_{ij}$  of its predecessor,  $\tau_{ij}$ . In this way, it is guaranteed that task  $\tau_{ii+1}$  starts only after its predecessor has finished execution.

In [Gon03], the authors have developed a schedulability analysis algorithm for ET tasks running under a hierarchical FPS/EDF scheduling policy. The worst-case response time  $R_{ab}$  of a task  $\tau_{ab}$ , regardless if it is scheduled under FP or EDF, is computed by considering:

- all possible critical instants initiated by the higher priority tasks  $\tau_{ac}$  from  $\Gamma_a$ . A *critical instant* is the moment when task  $\tau_{ab}$  is released. At the same time, higher priority tasks may be released, delaying the execution of task  $\tau_{ab}$ .

- all the jobs p of  $\tau_{ab}$  that appear during an interval of time called a *busy period*. For FPS tasks, the busy period is an interval of time that starts at the critical instant t and ends when all higher priority tasks (released at or after t) and task  $\tau_{ab}$  finish execution. For EDF tasks, the busy period is defined in a similar way, but the release of task  $\tau_{ab}$  may take place at a later instant in the busy period. This is caused by the fact that tasks with shorter deadlines may be released earlier than the critical instant, meaning that for EDF tasks the start of the busy period does not necessarily coincide with the critical instant.

For all considered situations, a response time  $R_{abc}(p)$  is computed, which leads to the value of the worst-case response time  $R_{ab}$  for  $\tau_{ab}$  to be determined as:

$$R_{ab} = \max(\max(R_{abc}(p))), \forall \tau_{ac} \in hp(\tau_{ab}), \forall p$$

(3.3)

Response times for the FPS and EDF tasks respectively are obtained using workload equations. Given a task  $\tau_{ab}$  and an interval of time *t*, a workload equation computes the amount of interference that  $\tau_{ab}$  can suffer during *t* from higher priority tasks and from tasks with earlier deadlines.

For FPS tasks, the worst case response times are influenced only by higher priority tasks, so the completion time of an activation *p* of task  $\tau_{ab}$ , when the critical instant is initiated by a higher priority task  $\tau_{ac}$  is given by:

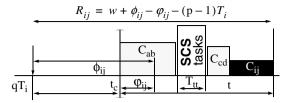

$$R_{abc}(p) = w_{abc}(p) + \phi_{ab} - (p-1) \cdot T_a - \phi_{abc}$$

(3.4)

where  $\phi_{ab}$  is the offset of  $\tau_{ab}$ ,  $T_a$  is the period of task-graph  $\Gamma_a$ ,  $\phi_{abc}$  is the phase between event arrivals and the critical instant, and  $w_{abc}(p)$  is the busy period. The phase  $\phi_{abc}$  is computed as:

$$\varphi_{abc} = T_a - (\phi_{ac} + J_{ac} - \phi_{ab}) mod T_a$$

(3.5)

where  $\phi_{ac}$  and  $J_{ac}$  are the offset and the jitter of the task  $\tau_{ac}$  that initiates the critical instant. The busy period is determined using the following equation:

$$w_{abc}(p) = B_{ab} + (p - p_{0, abc} + 1) \cdot C_{ab} + W_{ac}(\tau_{ab}, w_{abc}(p)) +$$

(3.6)

$$\sum_{\forall i \neq a} W_i'(\tau_{ab}, w_{abc}(p))$$

where  $B_{ab}$  is the blocking time of  $\tau_{ab}$ ; the second term captures the jobs of  $\tau_{ab}$  that appear during the considered time interval;  $W_{ac}$  is the worst case interference produced by higher priority tasks in  $\Gamma_a$  when the critical instant is initiated by  $\tau_{ac}$ :

$$W_{ik}(\tau_{ab}, t) = \sum_{j \in hp_a(\tau_{ab})} \left( \left\lfloor \frac{J_{ij} + \varphi_{ijk}}{T_i} \right\rfloor + \left\lceil \frac{t - \varphi_{ijk}}{T_i} \right\rceil \right) \cdot C_{ij}$$

(3.7)

and  $W'_i$  is the worst-case interference produced by higher priority tasks in a task-graph  $\Gamma_i$  different than  $\Gamma_a$ . This interference is computed using the following equation:

$$W_i'(\tau_{ab}, t) = max(W_{ik}(\tau_{ab}, t)), \forall k \in hp_i(\tau_{ab})$$

(3.8)

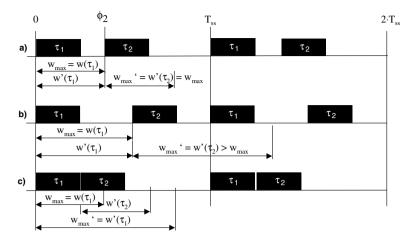

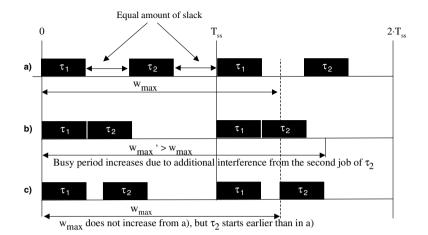

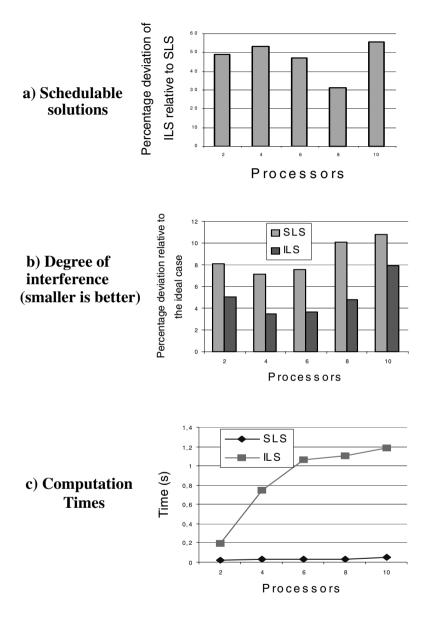

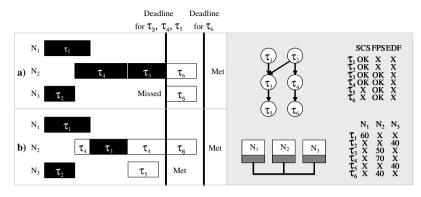

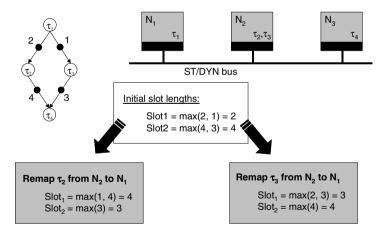

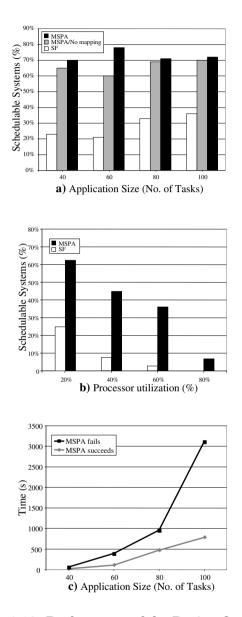

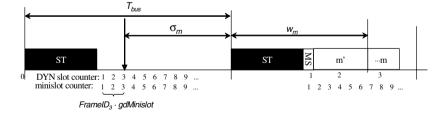

For EDF tasks, the worst-case response times are influenced by higher priority tasks and by EDF tasks running at the same priority level as the task under analysis. Consequently, the worst-case interference produced by a task-graph  $\Gamma_i$  on the execution of the analysed task  $\tau_{ab}$  will contain two parts that are added together: the EDF interference  $W_{ik}^{EDF}$ , and the FPS interference  $W_{ik}^{FP}$ . The worst-case interference  $W_{ik}^{FP}$  of strictly higher priority tasks in a task-graph is computed based on Equation (3.7). For the tasks running at the same priority level, the scheduling policy is EDF, which leads to the following modification of the interference equation: