#### Linköping Studies in Science and Technology Dissertation No. 945

### Hybrid Built-In Self-Test and Test Generation Techniques for Digital Systems

Gert Jervan

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

Linköping 2005

To Liisu

### Abstract

The technological development is enabling the production of increasingly complex electronic systems. All such systems must be verified and tested to guarantee their correct behavior. As the complexity grows, testing has become one of the most significant factors that contribute to the total development cost. In recent years, we have also witnessed the inadequacy of the established testing methods, most of which are based on low-level representations of the hardware circuits. Therefore, more work has to be done at abstraction levels higher than the classical gate and register-transfer levels. At the same time, the automatic test equipment based solutions have failed to deliver the required test quality. As a result, alternative testing methods have been studied, which has led to the development of built-in self-test (BIST) techniques.

In this thesis, we present a novel hybrid BIST technique that addresses several areas where classical BIST methods have shortcomings. The technique makes use of both pseudorandom and deterministic testing methods, and is devised in particular for testing modern systems-on-chip. One of the main contributions of this thesis is a set of optimization methods to reduce the hybrid test cost while not sacrificing test quality. We have devel-

oped several optimization algorithms for different hybrid BIST architectures and design constraints. In addition, we have developed hybrid BIST scheduling methods for an abort-on-first-fail strategy, and proposed a method for energy reduction for hybrid BIST.

Devising an efficient BIST approach requires different design modifications, such as insertion of scan paths as well as test pattern generators and signature analyzers. These modifications require careful testability analysis of the original design. In the latter part of this thesis, we propose a novel hierarchical test generation algorithm that can be used not only for manufacturing tests but also for testability analysis. We have also investigated the possibilities of generating test vectors at the early stages of the design cycle, starting directly from the behavioral description and with limited knowledge about the final implementation.

Experiments, based on benchmark examples and industrial designs, have been carried out to demonstrate the usefulness and efficiency of the proposed methodologies and techniques.

## Acknowledgments

I came to ESLAB in the spring of 1998 to work on my master thesis. I was 100% sure that I would stay for 3 months and I had no plans for longer residence or PhD studies at Linköping. How wrong I was! As you see – it is 2005 and the thesis is in your hands.

The biggest "culprit" is undoubtedly Professor Zebo Peng. He encouraged me to take up the PhD studies at ESLAB and has been a great support since then. Zebo's supervision style is something that I really admire. He has always given me plenty of freedom while making sure that the work progresses towards the right direction. His recommendations and guidance have made me to stand on my own feet and it is hard to underestimate this.

A special thank should go to Professor Petru Eles, who has brought new ideas into my research and has enriched days with interesting remarks, either about research, politics or sports.

Many thanks also to my first scientific supervisor Professor Raimund Ubar from Tallinn University of Technology. We have had very fruitful cooperation in the past and I am very hopeful that the same will continue in the future. This cooperation has produced several excellent results, some of which are presented also in this thesis. The cooperation with Gunnar Carlsson from Ericsson has provided invaluable insight into the industrial practices.

During my years at IDA I have met many wonderful people and I am really grateful for those moments. A special thank to Gunilla for taking care of many practical issues. Not to mention you, ESLAB guys! It has been many wonderful years at Linköping and it would have been much more boring without you.

This work has been supported by the Swedish Foundation for Strategic Research (SSF) under the INTELECT and STRINGENT programs.

Finally, I would like to thank my family. My mother, father and sister have always been the greatest supporters. Encouragement and care from Liisu have been invaluable. Suur aitähh teile: Eeve, Toomas, Getli ja Mai-Liis!

Gert Jervan

Linköping/Tallinn 2005

Gert Jeneau

# **Table of Contents**

| Pa | art I Preliminaries                                  | 1  |

|----|------------------------------------------------------|----|

| 1. | Introduction                                         | 3  |

|    | 1.1. Digital Systems Design and Manufacturing Flow   | 5  |

|    | 1.2. Motivation                                      | 9  |

|    | 1.3. Problem Formulation                             | 10 |

|    | 1.4. Contributions                                   | 11 |

|    | 1.5. Thesis Overview                                 | 13 |

| 2. | Testing and Design for Testability                   | 15 |

|    | 2.1. Introduction to Hardware Testing                | 16 |

|    | 2.2. Failures and Fault Models                       | 18 |

|    | 2.2.1. Stuck-At Fault Model                          | 19 |

|    | 2.2.2. Other Structural Fault Models                 | 21 |

|    | 2.2.3. High-Level Fault Models                       | 21 |

|    | 2.3. Automatic Test Pattern Generation               | 23 |

|    | 2.4. Test Generation at Higher Levels of Abstraction | 26 |

|    | 2.5. Test Application                                | 27 |

|    | 2.5.1. Off-line Test Application                     | 28 |

|    | 2.5.2. Abort-on-First-Fail Testing                   |    |

|    | 2.6. Design for Testability                          | 30 |

|    |                                                      |    |

| 2.6.1. Scan-Path Insertion                             | 31   |

|--------------------------------------------------------|------|

| 2.6.2. Built-In Self-Test                              | 33   |

| 2.7. Emerging Problems in System-on-Chip Testing       | 44   |

| 2.7.1. Core Internal Test Knowledge Transfer           | 48   |

| 2.7.2. Core Test Access Challenges                     |      |

| 2.7.3. Chip-level Test Challenges                      |      |

| 2.7.4. Core Test Architecture                          |      |

| 2.7.5. Power Dissipation                               | 53   |

| 2.8. Conclusions                                       | 55   |

| Part II Hybrid Built-In Self-Test                      | 57   |

| 3. Introduction and Related Work                       | 59   |

| 3.1. Introduction                                      | 60   |

| 3.2. Problems with Classical BIST                      | 61   |

| 3.3. BIST Improvement Techniques                       | 64   |

| 3.3.1. Test Point Insertion                            |      |

| 3.3.2. Weighted Random Testing                         | 66   |

| 3.3.3. Test Pattern Compression                        | 66   |

| 3.3.4. Mixed-Mode Schemes                              | 67   |

| 3.4. Conclusions                                       | 70   |

| 4. Hybrid BIST Concept                                 | 73   |

| 4.1. Introduction                                      | 74   |

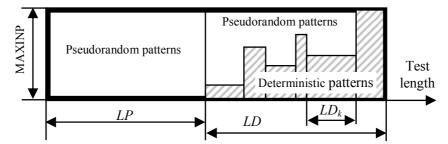

| 4.2. Basic Principle                                   | 75   |

| 4.3. Cost Calculation                                  | 77   |

| 4.4. Architectures                                     | 79   |

| 4.4.1. Core-Level Hybrid BIST Architecture             | 80   |

| 4.4.2. System-Level Hybrid BIST Architectures          | 82   |

| 4.5. Conclusions                                       | 87   |

| 5. Hybrid BIST Cost Minimization for Single Core Desig | ms89 |

| 5.1. Introduction                                      | -    |

| 5.2. Test Cost Minimization Algorithms                 |      |

|                                                        |      |

|    | 5.2.1. ATPG Based Approach                              | 92    |

|----|---------------------------------------------------------|-------|

|    | 5.2.2. Fault Table Based Approach                       | 93    |

|    | 5.2.3. Tabu Search Based Cost Optimization              | 95    |

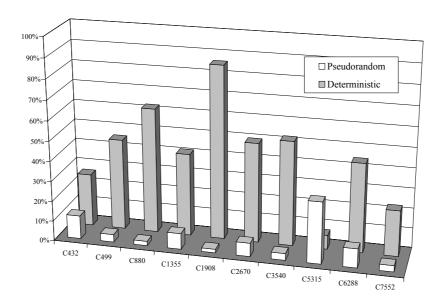

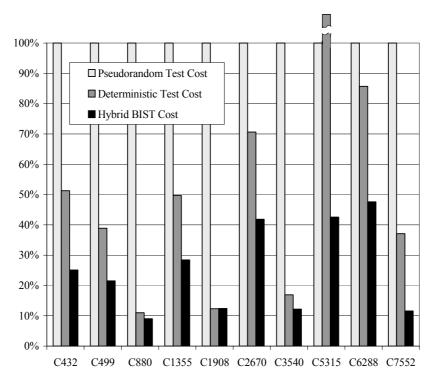

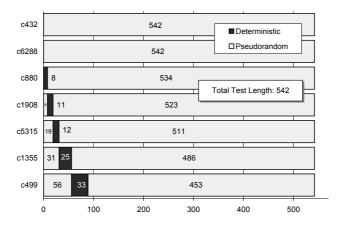

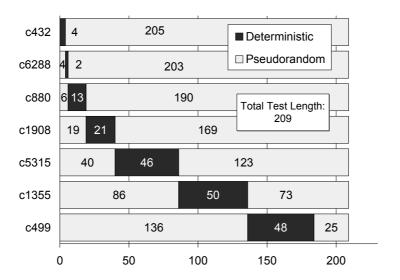

|    | 5.3. Experimental Results                               | 98    |

|    | 5.4. Conclusions                                        | . 106 |

| 6. | Hybrid BIST Time Minimization for Systems-on-Chip       | .109  |

|    | 6.1. Introduction                                       | .109  |

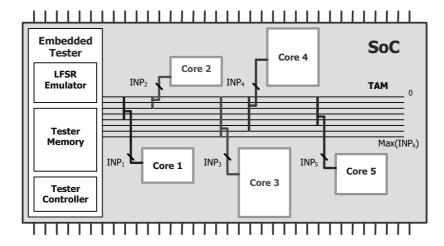

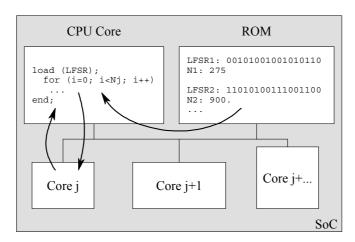

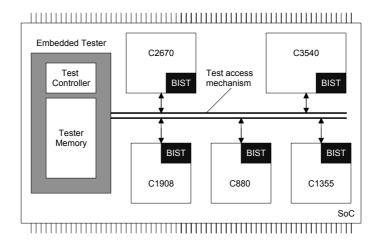

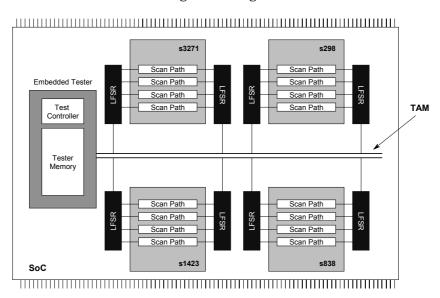

|    | 6.2. Parallel Hybrid BIST Architecture                  | .110  |

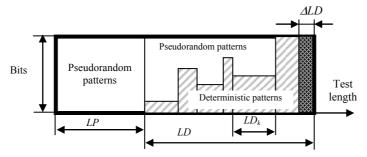

|    | 6.2.1. Basic Definitions and Problem Formulation        | .112  |

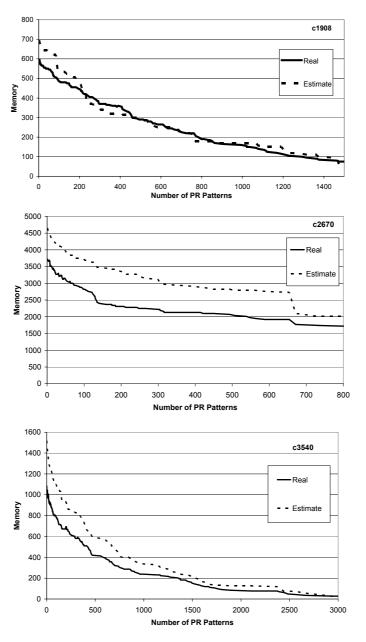

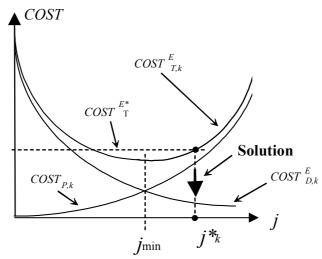

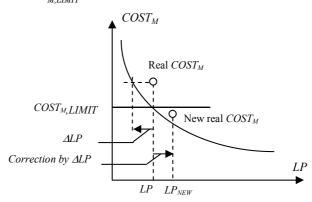

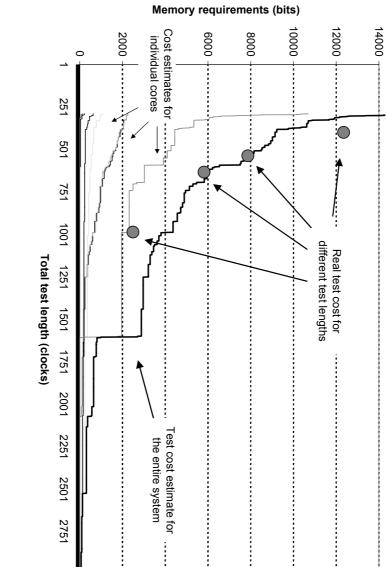

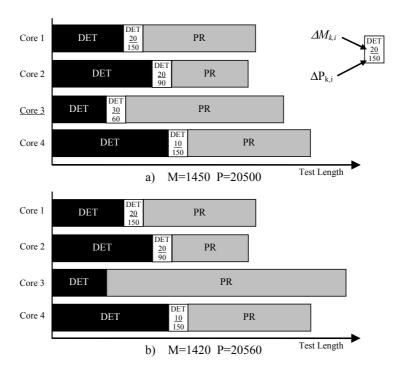

|    | 6.2.2. Test Set Generation Based on Cost Estimates.     | . 115 |

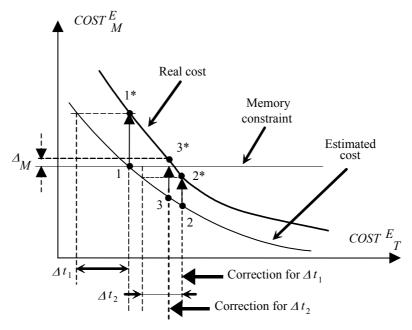

|    | 6.2.3. Test Length Minimization Under Memory            |       |

|    | Constraints                                             |       |

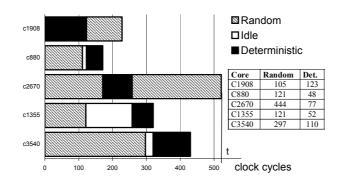

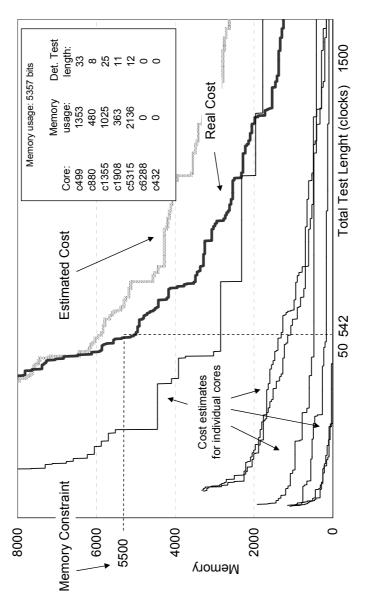

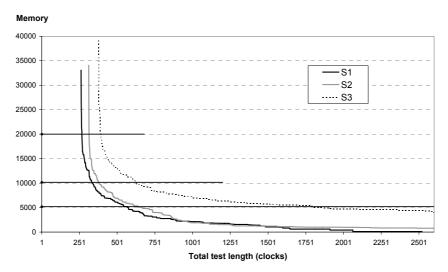

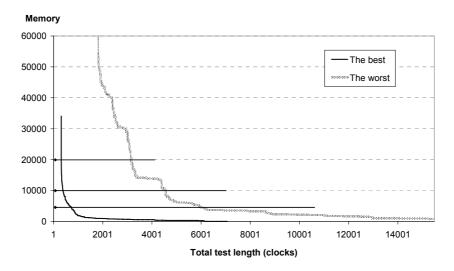

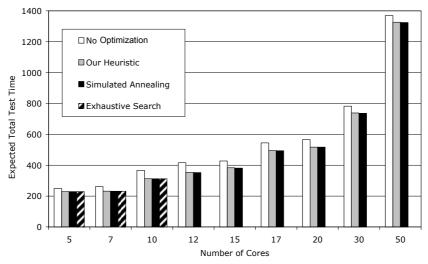

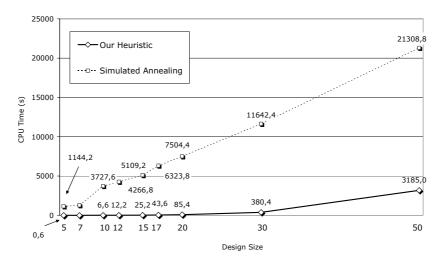

|    | 6.2.4. Experimental Results                             | .123  |

|    | 6.3. Broadcasting Based Hybrid BIST Architecture        | . 129 |

|    | 6.3.1. Straightforward Approach                         |       |

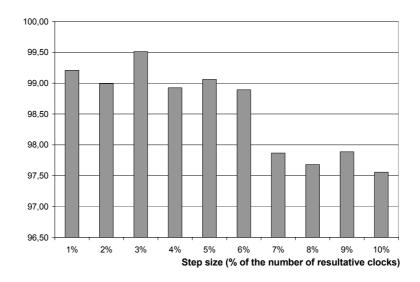

|    | 6.3.2. Iterative Approach                               | . 139 |

|    | 6.4. Conclusions                                        | . 147 |

| 7. | Hybrid BIST Energy Minimization                         | . 151 |

|    | 7.1. Introduction                                       | .151  |

|    | 7.2. Hybrid BIST and Possibilities for Energy Reduction | .152  |

|    | 7.3. Basic Definitions and Problem Formulation          | .154  |

|    | 7.3.1. Parameter Estimation                             | . 155 |

|    | 7.4. Heuristic Algorithms for Hybrid BIST Energy        |       |

|    | Minimization                                            | . 155 |

|    | 7.4.1. Local Gain Algorithm                             | . 156 |

|    | 7.4.2. Average Gain Algorithm                           | . 157 |

|    | 7.5. Experimental Results                               | . 159 |

|    | 7.6. Conclusions                                        | . 162 |

| 8. | Hybrid BIST in an Abort-on-First-Fail Environment       | . 163 |

|    | 8.1. Introduction                                       | .163  |

| 8.2. AOFF Test Scheduling                                                                            | . 164 |

|------------------------------------------------------------------------------------------------------|-------|

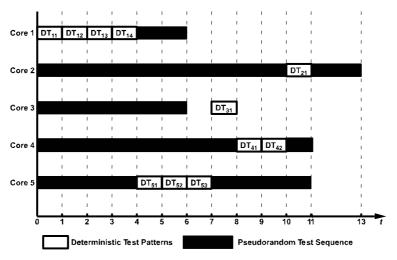

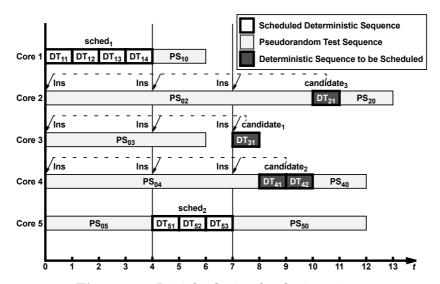

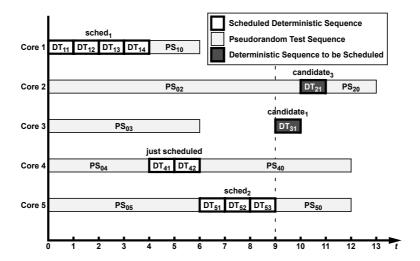

| 8.2.1. Definitions and Problem Formulation                                                           | . 165 |

| 8.2.2. Proposed Heuristic for Test Scheduling                                                        | .170  |

| 8.2.3. Experimental Results                                                                          | .173  |

| 8.3. Conclusions                                                                                     | .176  |

| Part III Hierarchical Test Generation                                                                | .177  |

| 9. Introduction and Modeling                                                                         | .179  |

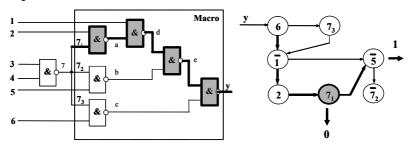

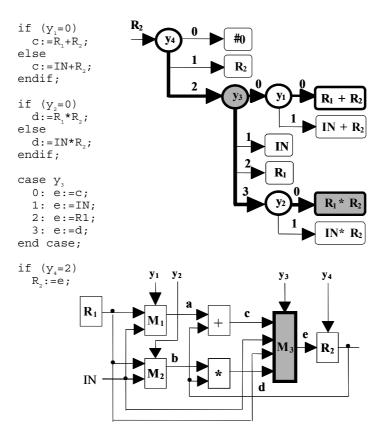

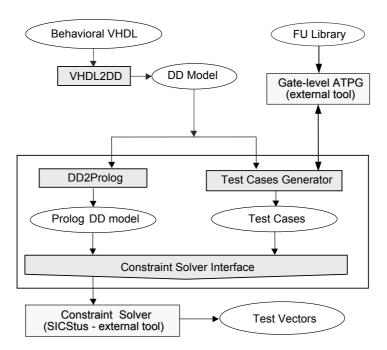

| 9.1. Modeling with Decision Diagrams                                                                 | .180  |

| 9.1.1. Introduction                                                                                  | . 181 |

| 9.2. Modeling Digital Systems by Binary Decision Diagrams                                            | . 182 |

| 9.3. Modeling with a Single Decision Diagram on Higher                                               |       |

| Levels                                                                                               | . 185 |

| 9.3.1. Decision Diagrams at the Behavioral Level<br>9.3.2. SICStus Prolog Representation of Decision | . 188 |

| Diagrams                                                                                             | .188  |

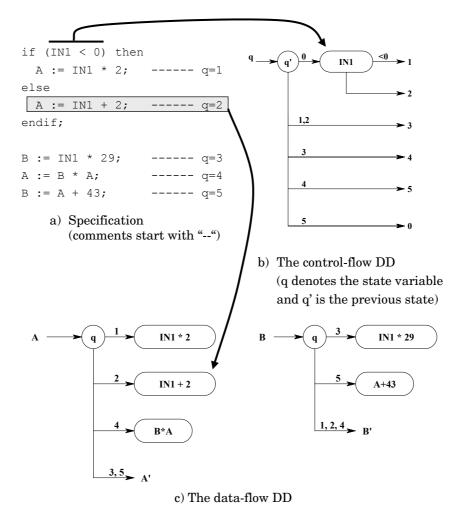

| 10. Hierarchical Test Generation with DDs                                                            | . 191 |

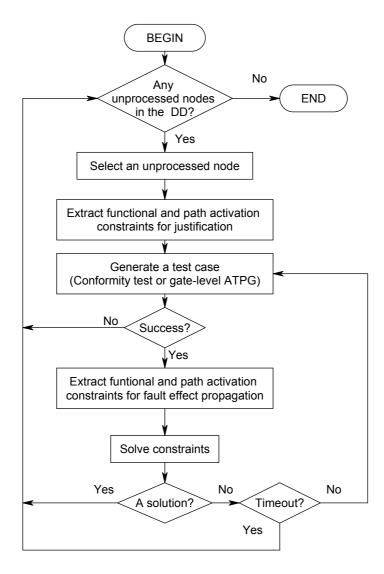

| 10.1. Test Generation Algorithm                                                                      | . 193 |

| 10.2. Scanning Test                                                                                  | . 195 |

| 10.2.1. Scanning Test in the HTG Environment                                                         | . 197 |

| 10.3. Conformity Test                                                                                | . 199 |

| 10.4. Experimental Results                                                                           | .203  |

| 10.5. Conclusions                                                                                    | .208  |

| Part IV Conclusions and Future Work                                                                  | .209  |

| 11. Conclusions                                                                                      | .211  |

| 12. Future Work                                                                                      | .215  |

| References                                                                                           | .219  |

# PART I PRELIMINARIES

# Chapter 1 Introduction

Jack S. Kilby devised the first integrated circuit (IC) almost five decades ago in 1958. Since that day, the semiconductor industry has distinguished itself by the rapid pace of improvement in its products. The most frequently cited trend is related to the integration level and is usually expressed via Moore's Law (i.e., the number of components per chip doubles every 18 months) [124]. The minimum feature sizes used to fabricate integrated circuits have decreased exponentially. The most significant trend from the consumers' point of view is the decreasing cost-per-function, which has led to significant improvements of productivity and quality of life through the proliferation of computers, electronic communication, and consumer electronics.

Until recently, reliability of electronic devices was mainly a concern in safety critical systems. In these systems, such as automotive or medical applications, failures may lead to catastrophic results and any failure should obviously be avoided. However, due to several reasons, reliability is becoming increasingly important also in other application domains, such as con-

sumer electronics, desktop computing, telecommunication systems and others. This is mainly because electronic systems are omnipresent in almost every modern system and any failure might lead to negative effects, in terms of financial loss or decreased comfort of life.

In order to achieve a desired level of reliability it is important to find errors before encountering their consequences. Due to the complexity of modern systems and multitude of problems related to error detection, these activities are usually carried out at various stages of the design and production flow and target different sub-problems. For example, one has to make sure that we have designed the correct system, as it has to satisfy certain properties or conditions, which may be either general or specific to the particular system, directly derived from the initial specification. In addition, we have to check whether we have designed our system correctly, i.e. we have to obtain confidence in the designed system's ability to deliver the service in accordance with an agreed-upon system specification. In general, these tasks are called *verification* [108]. Similarly, we also have to certify that the manufactured hardware system corresponds to its original specification and no faults have been introduced during the manufacturing phase. Such activity, commonly called *testing* [3], is characterized by execution of the system while supplying it with inputs, often using dedicated automatic test equipment (ATE). Testing is also used to guarantee that the system continues to work according to its specifications, as it can detect many field failures caused by aging, electromagnetic interference, environmental extremes, wear-out and others.

This thesis addresses the problem of hardware testing, in particular we will focus on issues related to testing of digital hardware.

#### INTRODUCTION

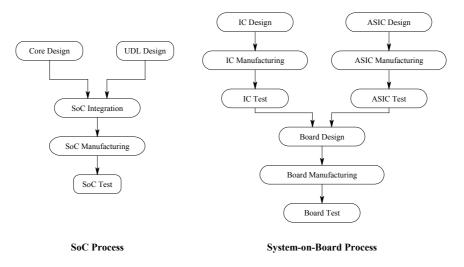

# 1.1. Digital Systems Design and Manufacturing Flow

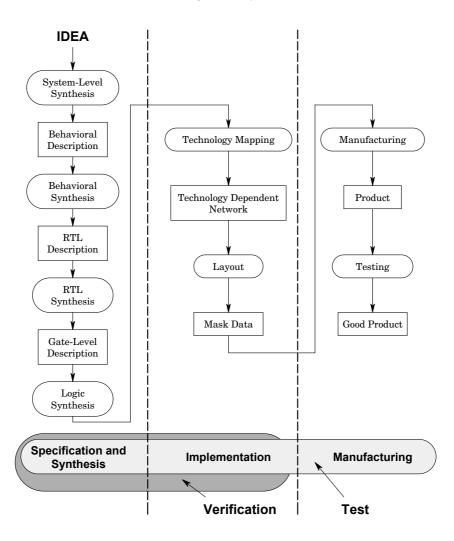

The development of a very large scale integrated (VLSI) system can typically be divided into three main phases: specification and synthesis, implementation, and manufacturing, as depicted in Figure 1.1. During the *specification and synthesis* phase, the functionality of the circuit is described. This can be done at different levels of abstraction [47]: behavioral, register-transfer (RT) or gate level, using VHDL, Verilog or any other hardware description language (HDL) [48]. The transformations between different abstraction levels are usually performed by synthesis algorithms. Typically, the following synthesis steps can be distinguished (from the highest abstraction level downwards) [120]:

- 1. System-level synthesis: The specification of a system at the highest level of abstraction is usually given by its functionality and a set of implementation constraints. The main task at this step is to decompose the system into several subsystems (communicating processes) and to provide a behavioral description for each of them, to be used as an input for behavioral synthesis.

- 2. Behavioral synthesis starts out with a description specifying the computational solution of the problem, in terms of operations on inputs in order to produce the desired outputs. The basic elements that appear in such descriptions are similar to those of programming languages, including control structures and variables with operations applied to them. Three major subtasks are:

- Resource allocation (selection of appropriate functional units),

- Scheduling (assignment of operations to time slots), and

- Resource assignment (mapping of operations to functional units).

Figure 1.1. Design and production flow.

The output of the behavioral synthesis process is a description at the register-transfer level (RTL), consisting of a datapath and a controller. The datapath, which typically consists of functional units (FUs), storage and interconnected hardware, performs operations on the input data in

#### INTRODUCTION

order to produce the required output. The controller controls the type and sequence of data manipulations and is usually represented as a state-transition table, which can be used in the later synthesis stages for controller synthesis.

- 3. RT-level synthesis then takes the RTL description produced by the previous step, which is divided into the datapath and the controller, as input. For the datapath, an improvement of resource allocation and assignment can be done, while for the controller actual synthesis is performed by generating the appropriate controller architecture from the input consisting of states and state transitions.

- 4. Logic synthesis receives as input a technology independent description of the system, specified by blocks of combinational logic and storage elements. It deals with the optimization and logic minimization problems.

During the *implementation* phase, the structural netlist of components, implementing the functions described in the specification, is generated and the design is transformed into layout masks. The transformation from the gate level to the physical level is known as technology mapping. The input of this step is a technology independent multi-level logic structure, a basic cell library, and a set of design constraints. During this phase appropriate library cells of a given target technology are selected for the network of abstract gates, produced as a result of logic synthesis, concluding thus the synthesis pipeline. The resulting layout gives designers possibility to extract design parameters, such as the load resistance and capacitance that are used for timing verification. Parameter extraction is becoming significantly important in modern deep submicron technologies.

At *manufacturing* stage the layout masks are used to produce the final circuitry in terms of a die on a wafer. The wafers are tested and all defective dies are identified. Good dies are pack-

aged, tested and, finally, all good chips are shipped to the customers.

The latest advance in microelectronics technology has enabled the integration of an increasingly large number of transistors into a single die. The increased complexity together with reduced feature sizes means that errors are more likely to appear. For improving reliability, two types of activities are normally used: verification and testing (Figure 1.1). According to the current state of the art, for verification, designs are usually *simulated* on different abstraction levels, prior to their implementation in silicon [44], [140]. In some situations, verification is also performed after the first prototype of the chip is available. As for complex designs exhaustive simulation is practically infeasible, simulation based verification gives only a certain level of assurance about the design correctness [34]. One of the alternatives would be formal verification that uses mathematical reasoning for proving correctness of designs [63], [100]. This approach, with few exceptional methods, such as equivalence checking [76], has not become the mainstream, mainly due to the lack of appropriate tools.

Testing verifies that the manufactured integrated circuit corresponds to the intended function of the implementation. Its purpose is not to verify the correctness of the design; on the contrary, it verifies the correctness of the manufacturing process. It is performed on actual dies or chips, using test patterns that are generated to demonstrate that the final product is fault-free. In addition, testing can also be used during the latter stages of the product life cycle, in order to detect errors due to aging, environment or other factors.

In order to ease the complexity of the test pattern generation process specific hardware constructs, usually referred to as design-for-testability structures, are introduced into the circuits. Testability issues are currently becoming incorporated into the standard design-flows, although several testability techniques,

#### INTRODUCTION

like scan-chain insertion and self-test techniques are well investigated and ready to be used.

Testing is one of the major expenses in the integrated circuit (IC) design and manufacturing process, taking up to 35% of all costs. Test, diagnosis and repair costs of complex electronic systems reach often 40-50% of the total product realization cost and very soon the industry might face the challenge that the test of a transistor is more expensive than manufacturing it [153].

#### 1.2. Motivation

As mentioned before, hardware testing is the process to check whether an integrated circuit is error-free. One of the reasons for errors are defects. As the produced circuits may contain different types of defects that are very complex, a model has to be defined to represent these defects to ease the test generation and test quality analysis problems. This is usually done at the logic level. Test patterns are then generated based on a defined fault model and applied to the manufactured circuitry. Most of the existing hardware testing techniques work at the abstraction levels where information about the final implementation architecture is already available. It has been proven mathematically that the generation of test patterns based on structural fault models is an NP-complete problem [80] and therefore different heuristics are usually used. Due to the increasing complexity of systems, these established low-level methods are not sufficient and more work has to be done at abstraction levels higher than the classical gate- and RT-level in order to ensure that the final design is testable and the time-to-market schedule is followed.

More and more frequently, designers also introduce special structures, called design for testability structures, during the design phase of a digital system for improving its testability. Several such approaches have been standardized and widely accepted. However, all those approaches entail an overhead in

terms of additional silicon area and performance degradation. Therefore it will be highly beneficial to develop DFT solutions that not only are efficient in terms of testability but also require minimal amount of overhead.

In addition, various researches have shown that the switching activity, and consequently the dynamic power dissipation, during the test mode, may be several times higher than during the functional mode [32], [174]. Self-tests, regularly executed in portable devices, can hence consume significant amounts of energy and consequently reduce the lifetime of batteries [52]. Excessive switching activity during the test mode can also cause problems with circuit reliability [54]. The increased current levels can lead to serious silicon failure mechanisms (such as electromigration [115]) and may need expensive packages for removal of the excessive heat. Therefore, it is important to find ways for reducing power dissipation during testing.

Most DFT techniques require external test equipment for test application. *Built-in self-test* (BIST) technique, on the other hand, implements all test resources inside the chip. This technique does not suffer from the bandwidth limitations that exist for external testers and allows applying at-speed tests. The disadvantage of this approach is that it cannot guarantee sufficiently high fault coverage and may lead to very long test sequences. Therefore, it is important to address the weakness of the classical BIST techniques in order to utilize its potentials completely.

#### 1.3. Problem Formulation

The previous section has presented the motivation for our work and given an indication of the current trends in the area of digital systems testing. The aim of the current thesis is twofold. First, we would like to propose a BIST strategy that can be used for reducing the testing effort for modern SOC designs and, sec-

#### INTRODUCTION

ondly, we are interested in performing test pattern generation as early as possible in the design process.

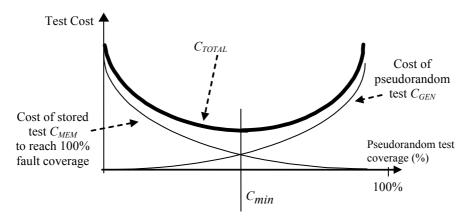

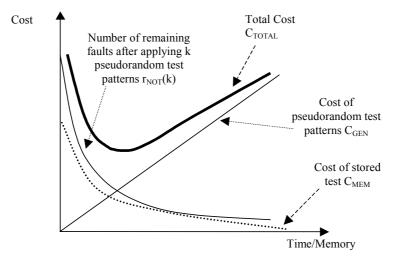

Since BIST structures are becoming more and more common in modern complex electronic systems, more emphasis should be put into minimization of costs caused by insertion of those structures. Our objective is to develop a hybrid BIST architecture that can guarantee high test quality by combining pseudorandom and deterministic test patterns, while keeping the requirements for BIST overhead low. We are particularly interested in methods to find the optimal combination of those two test sets as this can lead to significant reductions of the total test cost. This requires development of optimization methods that can take into account different design constraints imposed by the process technologies, such as tester memory, power dissipation, total energy and yield.

To deal with test pattern generation problem in early stages of the design flow we would like to develop a method that allows generation of test vectors starting directly from an implementation independent behavioral description. The developed method should have an important impact on the design flow, since it allows us to deal with testability issues without waiting for the structural description of the system to be ready. For this purpose high-level fault models and testability metrics should also be investigated in order to understand the links between high-level and low-level testability.

#### 1.4. Contributions

The main contributions of this thesis are as follows:

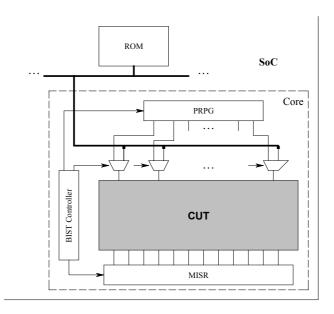

• A hybrid built-in self-test architecture and its optimization. We propose to use, for self-test of a system, a hybrid test set which consists of a limited number of pseudorandom and deterministic test vectors. The main idea is to apply a limited number of pseudorandom test vectors, which is then followed by the application of a stored deterministic test set,

specially designed to shorten the pseudorandom test cycle and to target the random resistant faults. For supporting such a test strategy, we have developed several hybrid BIST architectures that target different test scenarios. As the test lengths of the two test sequences are one of the very important parameters in the final test cost, we have to find the most efficient combination of those two test sets, while not sacrificing the test quality. In this thesis, we propose several different algorithms for calculating possible combinations between pseudorandom and deterministic test sequences while taking into account different design constraints, such as tester memory limitations and power dissipation. In addition, we have also developed methods where the information about the quality of the manufacturing process can be incorporated into the optimization algorithms.

A novel hierarchical test pattern generation algorithm at the behavioral level. We propose a test generation algorithm that works at the implementationindependent behavioral level and requires only limited knowledge about the final implementation. The approach is based on a hierarchical test generation method and uses two different fault models. One fault model is used for modeling errors in the system behavior and the other is related to the failures in the final implementation. This allows us to perform testability evaluation of the resulting system at the early stages of the design flow. In addition, it can identify possible hard-to-test modules of the system without waiting for the final implementation to be available. We perform experiments to show that the generated test vectors can be successfully used for detecting stuck-at faults and that our algorithm, working at high levels of abstraction, allows significant reduction of the test generation effort while keeping the same test quality.

#### INTRODUCTION

#### 1.5. Thesis Overview

The rest of the thesis is structured as follows. Chapter 2 introduces the topic of digital systems test and design for testability. We cover typical failure mechanisms and methods for fault modeling and introduce concepts of automatic test pattern generation and different test application methods. Thereafter an overview of the most common design for test methods are given, followed by a discussion of emerging problems in the area of SOC testing.

Part II of the thesis is dedicated to the hybrid BIST techniques. In Chapter 3 we discuss the problems related to classical BIST schemes and give an overview of different methods devised for its improvement. Chapter 4 gives an overview of the proposed hybrid BIST approach, followed, in Chapter 5, by test cost minimization methods for single core designs. In Chapter 6 different algorithms for hybrid BIST time minimization for SOC designs are presented. In the first part of this chapter we concentrate on parallel hybrid BIST architectures while in the latter part of the chapter the test pattern broadcasting based architecture is covered. Chapter 7 introduces possibilities for hybrid BIST energy minimization and in Chapter 8 algorithm for hybrid BIST scheduling in an abort-on-first-fail environment is presented. In every chapter, the proposed algorithms are described together with experimental results to demonstrate the feasibility and usefulness of the algorithms.

The third part of this thesis covers the proposed hierarchical test generation algorithm. It starts with a detailed discussion of behavioral level decision diagrams used to capture a design at several levels of abstraction. Thereafter we describe selected fault models and present our test pattern generation algorithm. The chapter concludes with experimental results where we demonstrate the efficiency of our approach for generating manufacturing tests.

Part IV concludes this thesis and discusses possible directions for future work.

# Chapter 2 Testing and Design for Testability

The aim of this chapter is to provide background for the thesis. It starts with an introduction to electronic systems testing. We will go through different fault types of complementary metal-oxide semiconductor (CMOS) integrated circuits and describe the ways to model them. Thereafter the chapter continues with the description of different testing and design-for-testability techniques. We give a short overview of the automatic test pattern generation (ATPG) algorithms and strategies and describe some systematic design modification techniques that are intended for improving testability, such as scan-chain insertion and built-in self-test (BIST).

The shift toward submicron technologies has enabled IC designers to integrate entire systems into a single chip. This new paradigm of system-on-chip (SOC) has introduced a magnitude of new testing problems and therefore at the end of this chapter emerging problems in SOC testing will also be described. We will

in particular focus on power dissipation, test access and test scheduling problems.

#### 2.1. Introduction to Hardware Testing

The testing activities for hardware systems can be classified according to many criteria. Generally speaking, we can distinguish two different types of testing: *parametric testing* and *functional testing*.

- 1. **Parametric Testing** measures electrical properties of pin electronics. This is done to ensure that components meet design specification for delays, voltages, power, etc. One of the parametric testing methodologies that has gained recently much attention is IDDq testing, a parametric technique for CMOS testing. IDDq testing monitors the current, IDD, a circuit draws when it is in a quiescent state. It is used to detect faults such as bridging faults, transistor stuck-open faults, gate oxide leaks, which increase the normally low IDD [84]. IDDq testing can detect some defects that are not detectable with other testing techniques and the results of IDDq testing can be used for reliability estimation.

- 2. Functional Testing aim at finding faults which cause a change in the functional behavior of the circuit. It is used in conjunction with the manufacturing process in order to ensure that only error-free chips are delivered to the customers. Some forms of functional testing can be used also for detecting faults that might occur during the chip lifetime, due to aging, environment and other factors.

Although highly important, this thesis will not cover aspects related to parametric testing and will focus solely on aspects related to functional testing of hardware circuits and systems. Therefore, also the word testing is used throughout this thesis to

#### TESTING AND DESIGN FOR TESTABILITY

denote functional testing of manufactured hardware systems, unless specified otherwise.

The purpose of hardware testing is to confirm that the function of each manufactured circuit corresponds to the function of the implementation [3]. During testing, the circuitry is exercised by applying the appropriate stimuli and its resulting responses are analyzed to determine whether it behaved correctly. If verification has assured that the design corresponds to its specification, then the incorrect behavior can be caused by defects introduced during the manufacturing process. There are many different types of defects, such as aging, misalignment, holes, contamination and others [130]. The diversity of defects leads to the very complex testing process, as the complexity of physical defects does not facilitate mathematical treatment of testing. Therefore, an efficient test solution requires an approach, where defects can be modeled by capturing the effect of the defect on the operation of the system at certain level of abstraction. This is called *fault modeling*. The most common alternative is to model faults at the logic level, such as *single stuck-at (SSA)* fault model. However, the increasing complexity of electronic systems necessitates the use of fault models that are derived from descriptions at higher abstraction levels, such as register-transfer (RT) and behavioral level.

After a fault model has been devised, efficient test stimuli can be generated by using an ATPG program that is applied to the circuit under test (CUT). However, this might not always be feasible, mainly because of the complexity of the testing process itself but also due to the complexity of the CUTs. Therefore, increasingly often designers introduce special structures, called design for testability structures, during the design phase of a digital system. The purpose of these structures is to make test pattern generation and test application easier and more efficient. Examples of typical DFT methods include scan-chain insertion and BIST.

In the following, we are going to describe these basic concepts of digital hardware testing in more detail. We will give the background needed for better understanding of the thesis and introduce the state-of-the-art in the areas of the thesis contributions.

#### 2.2. Failures and Fault Models

A typical 200-mm wafer in 0.25- $\mu$ m CMOS technology can potentially contain a million printed geometries—the typically rectangular shapes that are the layout of transistors and the connections between them—in both x and y directions. This amounts to about  $10^{12}$  possible geometries on each printed layer of a wafer. A few years back a chip typically had about six metal layers and a total number of lithography layers over 20 [130]. In 2004, we had already mass-market products produced in 90-nm technology, using 300-mm wafers with 7 interconnect layers [1]. Errors could arise in any geometry on any layer, so the possible number of defects is enormous.

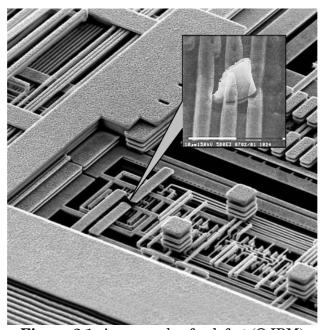

Chip manufacturing is performed in multiple steps. Each of those steps, such as depositing, conducting, and insulating material, oxidation, photolithography, and etching [151], may introduce defects. Therefore, in an integrated circuit (IC) we can observe a wide range of possible defects. These include particles (small bits of material that might bridge lines, Figure 2.1), incorrect spacing (variations, which may short a circuit), incorrect implant value (due to machine error), misalignment (of layers), holes (exposed etched area), weak oxides (that might cause gate oxide breakdown), and contamination (unwanted foreign material) [130]. On circuit level, these defects appear as *failure modes*. Most common of them are shorts, opens and parameter degradations. However, at this low level of abstraction testing is still practically infeasible.

#### TESTING AND DESIGN FOR TESTABILITY

Figure 2.1. An example of a defect (© IBM)

At the logical level, the effects of failure modes appear as incorrect signal values and in order to device efficient testing methods the effects of different failures should be captured in different *fault models*. The fault model does not necessarily have to capture the exact effect of the defect; rather it has to be useful in detecting the defects.

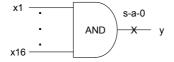

#### 2.2.1. Stuck-At Fault Model

The earliest and most well-known fault model is the single stuck-at (SSA) fault model [38] (also called single stuck line (SSL) fault model), which assumes that the defect will cause a line in the circuit to behave as if it is permanently stuck at a logic value 0 (stuck-at-0) or 1 (stuck-at-1). This means that with the SSA fault model it is assumed that the elementary components are fault-free and only their interconnects are affected [3]. This will reduce the number of faults to 2n, where n is the num-

ber of lines on which SSA faults can be defined. Experiments have shown that this fault model is useful (providing relatively high defect coverage, while being technology-independent) and can be used even for identifying the presence of multiple faults that can mask each other's impact on the circuit behavior. The possibility to analyze the behavior of the circuit using Boolean algebra has contributed to research in this domain very much. There are several approaches to identify test vectors using purely Boolean-algebraic techniques, search algorithm based techniques or techniques based on the combination of the two. Nevertheless, there are also several problems related to the SSA fault model, which become more obvious with the growth of the size of an IC. The main problem lies in the fact that the computation process to identify tests can be extremely resource and time intensive and, additionally, the stuck-at fault model is not good at modeling certain failure modes of CMOS, the dominant IC manufacturing technology at the present time.

The SSA fault model assumes that the design contains only one fault. However, with decreased device geometry and increased gate density on the chip, the likelihood is greater that more than one SSA fault can occur simultaneously and they may mask each other in such a way that the SSA test vectors cannot detect them. Therefore, it may be necessary to assume explicitly multiple stuck-at faults as well.

Despite all its shortcomings, the stuck-at fault model has been the dominant fault model for several decades, and continues to be dominant even today, for both its simplicity and its demonstrated utility. Therefore, also in this thesis we are going to discuss testing in the context of testing for single stuck-at (SSA) fault model and the required fault coverage refers to stuck-at fault coverage.

#### TESTING AND DESIGN FOR TESTABILITY

#### 2.2.2. Other Structural Fault Models

Although the SSA fault model is widely used both in academia and in industry, it is evident that the SSA fault model does not cover all possible defects. During recent years, several other fault models have gained popularity, such as *bridging faults*, *shorts* and *open faults*. However, these fault models still cannot address all the test issues with CMOS circuits. As a solution to this problem, two technologies have been proposed: Inductive fault analysis (IFA) [145] and inductive contamination analysis (ICA) [101]. These techniques present a closer relationship between physical defects and fault models. The analysis of a fault is based on analyzing the given manufacturing process and layout of a particular circuit.

A completely different aspect of fault model based testing is testing for *delay faults*. An IC with delay faults operates correctly at sufficiently low speed, but fails at rated speed. Delay faults can be classified into gate delay faults (the delay fault is assumed to be lumped at some gate output) and path delay faults (the delay fault is the result of accumulation of small delays as a signal propagates along one or more paths in a circuit).

#### 2.2.3. High-Level Fault Models

When test issues are addressed at an abstraction level higher than the traditional gate-level, the first problem that must be addressed is the identification of a suitable high-level fault model. Most of the cited approaches rely on high-level fault models for behavioral HDL descriptions that have been developed by the current practice of software testing [14], and extend them to cope with hardware descriptions. Several authors have proposed alternative fault models. Nevertheless, a reference fault model playing, at the behavioral level, the same role the well-known SSA is playing at the gate level is still missing.

By working on system models that hide the detailed information gate-level netlists capture, the high-level fault models are

not able to precisely foresee the gate-level fault coverage, which is normally used as the reference measure to quantify a circuit's testability. Nevertheless, they can be exploited to rank test sequences according to their testability value. The most common high-level fault models proposed in literature as metrics of the goodness of test sequences when working at higher levels of abstraction (RT level and behavioral level) include the following:

- Statement coverage: this is a well-known metric in the software testing field [14] indented to measure the percentage of statements composing a model that are executed by a set of given test patterns. Further improvements of this metric are the Branch coverage metric, which measures the percentage of branches of a model that are executed by the given test patterns, and the Path coverage metric which measures the percentage of paths that are traversed by the given test patterns, where a path is a sequence of branches that should be traversed for going from the start of the model description to its end.

- *Bit coverage*: in this model [42], [107] it is assumed that each bit in every variable, signal or port in the model can be stuck to zero or one. The bit coverage measures the percentage of stuck-at bits that are propagated to the model outputs by a given test sequence.

- Condition coverage: the model is proposed in [42] and it is intended to represent faults located in the logic implementing the control unit of a complex system. The authors assume that each condition can be stuck-at true or stuck-at false. Then, the condition coverage is defined as the percentage of stuck-at conditions that are propagated to the model outputs by a given test sequence. This model is used in [42] together with bit coverage for estimating the testability of complex circuits.

- Mutation testing [31] concentrates on selecting test vectors that are capable to distinguish a program from a set of

#### TESTING AND DESIGN FOR TESTABILITY

faulty versions or mutants. A mutant is generated by injecting a single fault into the program. For example, if we have the expression:

$$X := (a + b) - c;$$

To rule out the fault that the first "+" is changed to "-", b must not be 0 (because a + 0 = a - 0 and this fault cannot be detected). Additionally, to rule out the fault that instead of "+" there is " $\times$ ", we have to assure that  $a + b \neq a \times b$ .

All these fault models target faults in the circuit's behavior, not in its structure. For targeting errors in the final implementation, it is very important to establish the relationship between the high-level fault models and the lower level ones. This has been done so far only experimentally (e.g. [90]) and there are no systematic methods currently available.

#### 2.3. Automatic Test Pattern Generation

Digital systems are tested by applying appropriate stimuli and checking the responses. Generation of such stimuli together with calculation of their expected responses is called *test pattern generation*. Test patterns are in practice generated by an *automatic test pattern generation* (ATPG) tool and typically applied to the circuit using *automatic test equipment* (ATE). Due to several limitations of ATE, there exist approaches where the main functions of the external tester have been moved onto the chip. Such DFT practice is generally known as BIST.

With the evolution of test technology, various techniques have been developed for IC testing.

Exhaustive test: The most straightforward approach, where all possible input combinations are generated and applied to the CUT. Exhaustive test set is easy to generate and guarantees 100% fault coverage for combinatorial circuits. However, for an n-input combinational circuit the number of possible test vectors is  $2^n$  and therefore this approach is practically infeasible for large

circuits. As an example, it takes approx. 6 centuries to exhaustively test a 32-bit adder at a speed of 1 GHz ( $2^{64} \approx 1,84 \times 10^{19}$  test patterns).

Pseudo-exhaustive test: The CUT is divided into smaller parts and every part is tested exhaustively [119]. This type of partitioning results in much smaller number of test vectors, but pseudo-exhaustive testing might still be infeasible with systems that are more complex and the hardware implementation of the pseudo-exhaustive test generator is difficult.

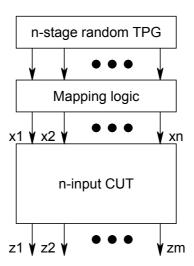

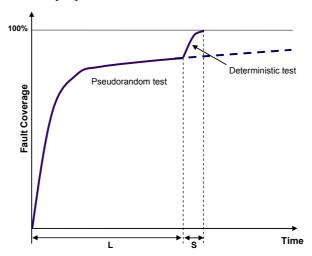

Pseudorandom test: A low-cost IC test solution, where test patterns are generated randomly. The process however is not truly random, as patterns are generated by a deterministic algorithm such that their statistical properties are similar to a randomly selected test set. The advantage of this approach is the ease of pattern generation, as the approach usually does not take into account the function or the structure of the circuit to be tested. The clear disadvantage of pseudorandom testing is the size of the generated test set (it might be several orders of magnitude larger than the same quality deterministic test set). And, due to the size, determining the quality of a test is problematic. Another difficulty is due to the so-called *random-pattern-resistant* or *hard-to-detect* faults that require a different approach than pseudorandom testing [37]. This problem will be discussed in conjunction with BIST later in this chapter.

There are several methods for pseudorandom test pattern generation. It is possible to use a software program, but more widespread methods are based on *linear feedback shift registers* (LFSR). An LFSR has a simple, regular structure and can be used for test pattern generation as well as for output response analysis. LFSRs are frequently used for on-chip test pattern generation in BIST environments and they will be discussed at a greater length later in the thesis.

Deterministic test: Deterministic tests are generated based on a given fault model and the structure of the CUT. This approach

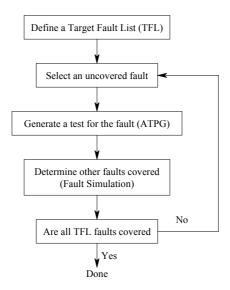

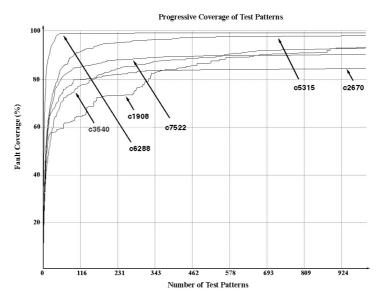

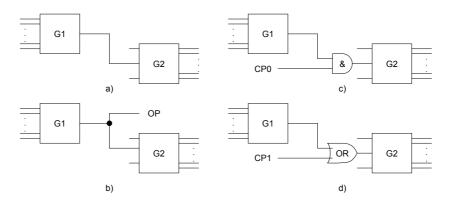

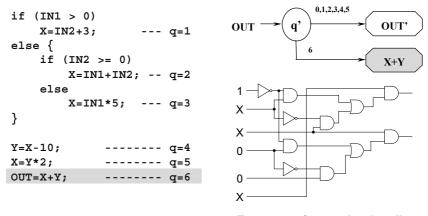

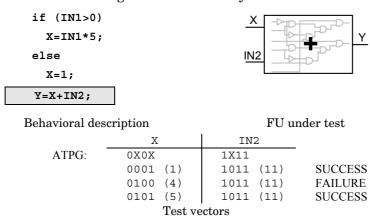

is sometimes also referred to as *fault-oriented* or *structural* test generation approach. As a first step of the test generation process, the structure of the CUT will be analyzed and a list of all possible faults in the CUT will be generated. Thereafter, the tests are generated using an appropriate test pattern generation algorithm. The typical process of a structural test generation methodology is depicted in Figure 2.2.

Figure 2.2. Structural test generation.

Deterministic test pattern generation belongs to a class of computationally difficult problems, referred to as NP-complete [80]. Several heuristics have been developed to handle test generation for relatively large combinational circuits in a reasonable time. These include the D-algorithm [139], the path-oriented decision-making (PODEM) algorithm [60], and the fan-oriented test generation (FAN) algorithm [45].

Test generation for sequential circuits is more difficult than for combinational circuits [73], [121]. There exist methods for test pattern generation for relatively small sequential circuits

[27], [131], but for large sequential circuits test generation remains basically an unsolved problem, despite rapid increase of computational power. A possible solution can be found by moving to higher levels of abstraction and using more advanced test generation methods, like hierarchical test generation. Promising results in this domain have been reported in [136].

### 2.4. Test Generation at Higher Levels of Abstraction

While the design practice is quickly moving toward higher levels of abstraction, test issues are usually considered only when a detailed description of the design is available, typically at the gate level for test sequence generation and at RT-level for design for testability structure insertion.

Recently intensive research efforts have been devoted to devise solutions tackling test sequence generation in the early design phases, mainly at the RT level, and several approaches have been proposed. Most of them are able to generate test patterns of good quality, sometimes comparable or even better than those produced by gate-level ATPG tools. However, lacking general applicability, these approaches are still not widely accepted by the industry. The different approaches are based on different assumptions and on a wide spectrum of distinct algorithmic techniques. Some are based on extracting from a behavioral description the corresponding control machine [125] or the symbolic representation based on binary decision diagrams [41], while others also synthesize a structural description of the data path [40]. Some approaches rely on a direct examination of the HDL description [25], or exploit the knowledge of the gate-level implementation [141]. Some others combine static analysis with simulation [28]. In [97] the applicability of some classical software testing methods for hardware test generation has been investigated with not very encouraging results. The applicability of

a particular software testing technique, mutation testing [31], for hardware testing is discussed in [7], with results that are slightly better than those reported in [97]. However, it has been demonstrated that high-level test pattern generation methodology can successfully be used both for design validation and to enhance the test effectiveness of classic, gate-level test generation [144].

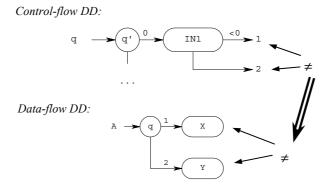

An alternative to these solutions are hierarchical test generation methods. The main idea of the hierarchical test generation (HTG) technique is to use information from different abstraction levels while generating tests. One of the main principles is to use a modular design style, which allows to divide a larger problem into several smaller problems and to solve them separately. This approach allows generating test vectors for the lower level modules based on different techniques suitable for the respective entities.

In hierarchical testing, two different strategies are known: top-down and bottom-up. In the bottom-up approach [126], tests generated at the lower level will be assembled at the higher abstraction level. The top-down strategy, introduced in [113], uses information, generated at the higher level, to derive tests for the lower level.

#### 2.5. Test Application

As previously mentioned, hardware testing involves test pattern generation, discussed above, and test application. Test application can be performed either on-line or off-line. The former denotes the situation where testing is performed during normal operational mode and the latter when the circuit is not in normal operation but in so-called test mode. The primary interest of this thesis is off-line testing although some of the results can be applied in an on-line testing environment as well.

#### 2.5.1. Off-line Test Application

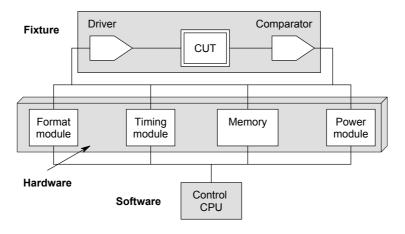

Off-line tests can be generated either by the system itself or outside the chip, using an ATPG, and applied by using Automatic Test Equipment (ATE). In Figure 2.3 a generic structure of the ATE is given [130]. It can be divided into 3 main modules: fixture, hardware and software. The module that holds the CUT and provides all necessary connections is usually referred to as a fixture. The fixture is connected to the hardware module that is a computer system with sufficient memory. The testing process is controlled by the tester software that guarantees correct format and timing of the test patterns.

**Figure 2.3.** Block diagram of ATE.

The ATE memory size defines the amount of test patterns the ATE can apply in one test run, without memory reload. Such reloads are time consuming, thus making them undesired. Therefore, the test set should be devised so that all test patterns fit into the tester memory. However, with increased device density, the volume of test data is becoming increasingly large, thus setting difficult constraints for test engineers.

With the emerging of sub-micron and deep sub-micron technologies, the ATE approach is becoming increasingly problematic. There are several reasons for that:

- Very expensive test equipment: It is predicted that between 2009 and 2012 ICs will dissipate 100 to 120 W (at 0.6 V), run at frequencies between 3.5 and 10 GHz and have microprocessors with greater than 1 billion transistors. A tester for such a chip will bear 1 400 pins and have a price tag greater than 20 million USD [8], [153].

- Due to the increasing complexity and density of ICs, testing time is continuously increasing and time to market becomes unacceptably long.

- The test sizes and consequently memory requirements for ATEs are continuously increasing.

- The operating frequencies of ATEs should be higher or equal to the frequencies of CUT. This rules out testing cutting edge ICs as the frequency of existing ATEs is always one step behind the latest developments (it takes time until the latest technology reaches the ATE products). This increases inaccuracy of the testing process.

All those reasons have led to the investigation of different alternatives that could make testing of complex ICs more feasible. Several methods have been developed that reduce the significance of external testers and reduce the cost of the testing process, without compromising on quality. One of the alternatives is to partition the test function into on-chip and off-chip resources [74], [110]. By embedding different test activities on-chip makes it possible to use an ATE with significantly reduced requirements. Those methods are in general known as DFT techniques and are described in greater length later in this chapter.

#### 2.5.2. Abort-on-First-Fail Testing

In a production test environment, where a large number of chips have to be tested, an *abort-on-first-fail* (AOFF) approach is usu-

ally utilized. It means that the test process is stopped as soon as a fault is detected. This approach leads to reduced test times and consequently to reduced production costs, as faulty chips can be eliminated before completing the entire test flow. In such a test environment, the likelihood of a block to fail during the test should be considered for test scheduling in order to improve test efficiency [78], [85], [104], [111], [122]. In [104], for example, it was proposed to reduce the average test completion time by applying tests with short test times first. In [78] and [85], it was proposed to use defect probabilities of individual cores for efficient scheduling in an AOFF environment. Such probabilities can be extracted from the statistical analysis of the manufacturing process.

In general, these approaches reduce average test time in largescale manufacturing test environments. However, it should be noted here, that this approach has especially high significance during the early phases of the production, when the yield is low and the defects are more likely to appear.

#### 2.6. Design for Testability

Test generation and application can be more efficient when testability is already considered and enhanced during the design phase. The generic aim of such an enhancement is to improve controllability and observability with small area and performance overhead. Controllability and observability together with predictability are the most important factors that determine the complexity of deriving a test set for a circuit. Controllability is the ability to establish a specific signal value at each node in a circuit by setting values on the circuit's inputs. Observability, on the other hand, is the ability to determine the signal value at any node in a circuit by controlling the circuit's inputs and observing its outputs. DFT techniques, used to improve a circuit's

controllability and observability, can be divided into two major categories:

- DFT techniques that are specific to one particular design (ad hoc techniques) and cannot be generalized to cover different types of designs. Typical examples are test point insertion and design partitioning techniques.

- Systematic DFT techniques are techniques that are reusable and well defined (can be even standardized).

In the following sections some systematic DFT techniques, that are significant in the context of this thesis, will be discussed.

#### 2.6.1. Scan-Path Insertion

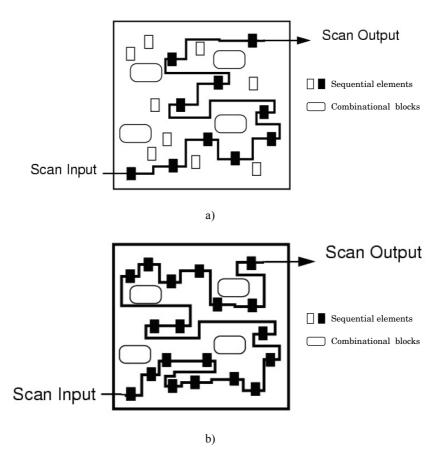

To cope with the problems caused by global feedback and complex sequential circuits, several DFT techniques have been proposed. One of them is *scan-path* insertion [169]. The general idea behind scan-path is to break the feedback paths and to improve the controllability and observability of the sequential elements by introducing an over-laid shift register called scan path (or scan chain). Despite the increase in fault coverage and reduced ATPG complexity, there are some disadvantages with using scan techniques, like increase in silicon area, additional pins, increased power consumption, increase in test application time and decreased clock frequency. We can distinguish two different types of scan-based techniques — *partial scan* and *full scan*, which are illustrated in Figure 2.4.

In case of partial scan (Figure 2.4a), only a subset of the sequential elements will be included in the scan path. This leads to moderate increase in terms of silicon area while requiring more complex ATPG. The full scan approach (Figure 2.4b), in contrast, connects all sequential elements into one or multiple scan chains. The main advantage of this approach is that this reduces the ATPG problem for sequential circuits to the more computationally tractable problem of ATPG for combinatorial circuits.

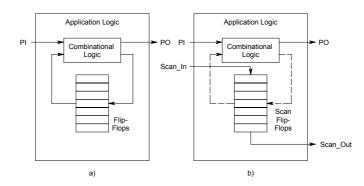

The scan-path insertion is illustrated in Figure 2.5 [128]. The original circuit is given in Figure 2.5a and the modified circuit with inserted scan-path in Figure 2.5b. Here, in the test mode, all sequential elements will be disconnected from the circuit and configured as a shift register. In large circuits the sequential elements can be divided between multiple scan-paths.

Figure 2.4. a) Partial scan b) Full scan.

Figure 2.5. a) Original design b) Design with scan-path.

When a design does not contain any scan-paths, test patterns can be applied to the CUT at every clock cycle and the approach is called *test-per-clock*. The introduction of the scan-path requires test pattern application in so-called scan cycles. In such a *test-per-scan* approach, the test patterns are shifted into a scan chain before the pattern at the primary inputs can be applied. Thereafter the test responses are captured in the scan flip-flops and shifted out while a new test is being shifted in. The length of such a cycle is defined by the length of the scan-path and therefore such a test-per-scan approach is much slower than test-per-clock testing. It also makes at-speed testing impossible. The obvious advantage, on the other hand, is the reduced ATPG complexity. It offers also high fault coverage and enables efficient fault diagnosis by providing the direct access to many internal nodes of the CUT.

#### 2.6.2. Built-In Self-Test

The main idea behind a BIST approach is to eliminate or reduce the need for an external tester by integrating active test infrastructure onto the chip. The test patterns are not any more generated externally, as it is done with ATE, but internally, using special BIST circuitry. BIST techniques can be divided into *offline* and *on-line* techniques. On-line BIST is performed during

normal functional operation of the chip, either when the system is in idle state or not. Off-line BIST is performed when the system is not in its normal operational mode but in special test mode. A prime interest of this thesis is off-line BIST that will be discussed further below. Every further reference to the BIST technique is in the context of off-line BIST.

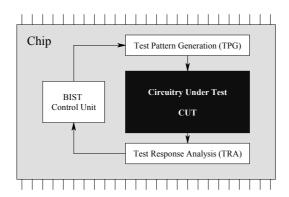

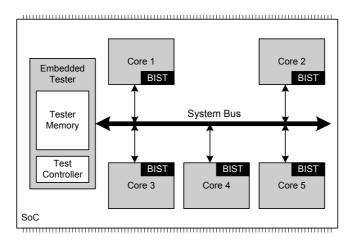

A typical BIST architecture consists of a test pattern generator (TPG), a test response analyzer (TRA), and a BIST control unit (BCU), all implemented on the chip (Figure 2.6). Examples of TPG are a ROM with stored patterns, a counter, or a LFSR. A typical TRA is a comparator with stored responses or an LFSR used as a signature analyzer. A BCU is needed to activate the test and analyze the responses. This approach eliminates virtually the need for an external tester. Furthermore, the BIST approach is also one of the most appropriate techniques for testing complex SOCs, as every core in the system can be tested independently from the rest of the system. Equipping the cores with BIST features is especially preferable if the modules are not easily accessible externally, and it helps to protect intellectual property (IP) as less information about the core has to be disclosed.

**Figure 2.6.** A typical BIST architecture.

In the following, the basic principles of BIST will be discussed. We are going to describe test pattern generation with LFSRs,

problems related to such an approach and describe some more known BIST architectures.

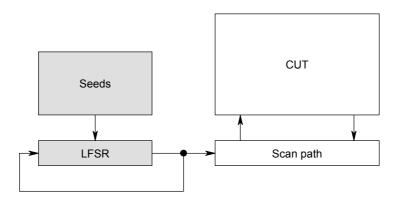

#### Test Pattern Generation with LFSRs

Typical BIST schemes rely on either exhaustive, pseudoexhaustive, or pseudorandom testing and the most relevant approaches use LFSRs for test pattern generation [5], [12], [172]. This is mainly due to the simple and fairly regular structure of the LFSR. Although the LFSR generated tests are much longer than deterministic tests, they are much easier to generate and have good pseudorandom properties.

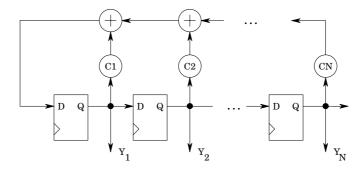

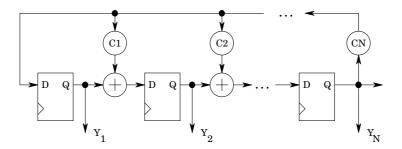

In Figure 2.7 a generic structure of the *n*-stage *standard* LFSR (also known as type 1 LFSR or external-XOR LFSR) and in Figure 2.8 a generic structure of the *n*-stage modular LFSR (also known as type 2 LFSR or internal-XOR LFSR) is given. An LFSR is a shift register, composed from memory elements (latches or flip-flops) and exclusive OR (XOR) gates, with feedback from different stages. It is fully autonomous, i.e. it does not have any input beside the clock. Ci in Figure 2.7 and Figure 2.8 denotes a binary constant and if Ci = 1 then there is a feedback from/to the ith D flip-flop; otherwise, the output of this flip-flop is not tapped and the corresponding XOR gate can be removed. The outputs of the flip-flops  $(Y_p, Y_2, ..., Y_N)$  form the test pattern. The number of unique test patterns is equal to the number of states of the circuit, which is determined, by the number and locations of the individual feedback tabs. The configuration of the feedback tabs can be expressed with a polynomial, called characteristic or feedback polynomial. For an LFSR in Figure 2.8 the characteristic polynomial P(x) is

$$P(x)=1+c_1x+c_2x^2+...+c_nx^n$$

.

An LFSR goes through a cyclic or periodic sequence of states and produces periodic output. The maximum length of this period is  $2^n$ -1, where n is the number of stages, and the characteristic polynomials that cause an LFSR to generate maximum-length

sequences are called *primitive polynomials* [62]. A necessary condition for a polynomial to be primitive is that the polynomial is irreducible, i.e. it cannot be factored.

Figure 2.7. Generic standard LFSR.

Figure 2.8. Generic modular LFSR.

The test vectors generated by an LFSR appear to be randomly ordered. They satisfy most of the properties of random numbers even though we can predict them deterministically from the LFSR's present state and its characteristic polynomial. Thus, these vectors are called *pseudorandom* vectors and such LFSRs can be called *pseudorandom pattern generator* (PRPG).

Test Response Analysis with LFSRs.

As with any other testing method, also with BIST, the response of the circuit has to be evaluated. This requires knowledge about the behavior of the fault-free CUT. For a given test sequence this can be obtained by simulating the known-good CUT. It is however infeasible to compare all response values on chip, as the number of test patterns in a test sequence can be impractically long. Therefore a better solution is to compact the responses of a CUT into a relatively short binary sequence, called a *signature*. Comparison of faulty and fault-free signatures can reveal the presence of faults. As such a compaction is not lossless, the signatures of faulty and fault-free CUT can be the same, although the response sequences of the two are different. This is called aliasing. The compression can be performed in two dimensions: time and space. Time compression compresses long sequences to a shorter signature and space compression reduces a large number of outputs to a smaller number of signals to be observed.

There are several compaction testing techniques, like parity testing, one counting, transition counting, syndrome calculation and signature analysis. In the following one of the most common techniques — *signature analysis* — is briefly described.

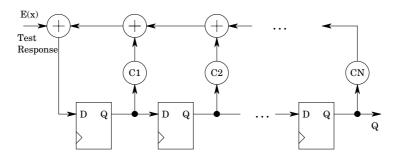

Signature analysis is a compression technique based on the concept of cyclic redundancy checking and implemented in hardware using LFSRs [46]. The responses are fed into the LFSR and at the end of the test application, the content of the LFSR is used as a signature. The simplest form of signature analysis is based on serial-input signature register. This kind of "serial" signature analysis, based on SLFSR, is illustrated in Figure 2.9. Here the LFSR is modified to accept an external input in order to act as a polynomial divider.

Figure 2.9. SLFSR based signature analysis

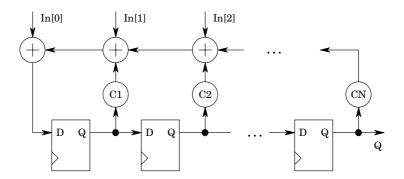

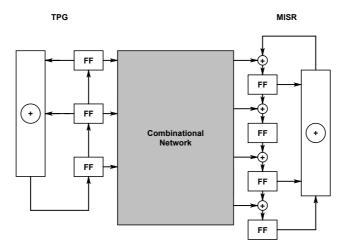

An extension of the serial-input signature register is the *multiple-input signature register* (MISR), where output signals are connected to the LFSR in parallel. There are several ways to connect the inputs (CUT outputs) to both types (standard and modular) of LFSRs to form an MISR. One of the possible alternatives is depicted in Figure 2.10. Here a number of XOR gates are added to the flip-flops. The CUT outputs are then connected to these gates.

**Figure 2.10.** Multiple-input signature register.

#### $Classification\ of\ BIST\ Architectures$

BIST Architectures can be divided, based on test application methods, into two main categories: parallel BIST (a.k.a. in-situ

BIST) and serial BIST (a.k.a. scan BIST). A parallel BIST scheme uses special registers, which work in four modes. In the system mode they operate just as D-type flip-flops. In the pattern generation mode they perform autonomous state transitions, and the states are the test patterns. In the response evaluation mode the responses of the CUT are compressed, and in the shift mode the registers work as a scan path. In this approach, one test pattern is applied at every clock cycle. Hence, such architectures are called test-per-clock BIST architectures. Examples of such architectures are built-in logic block observer (BILBO) and circular self-test path (CSTP). In contrast, serial BIST architectures assume that test patterns are applied via the scan chain. Such testper-scan approach requires SCL+1 clock cycles to shift in and to apply a test pattern and the same amount of clock cycles to shift out the test response, where SCL is the length of the longest scan chain, making it thus much slower than the test-per-clock approach. Although slower, this approach has several advantages, similar to the general scan-path based testing:

- It takes advantage of the traditional scan-path design, making it thus compatible with any commercial tool flow that supports scan chains, and requires a very small amount of additional design modifications.

- It can be implemented at the chip level even when the chip design uses modules that do not have any BIST circuitry, provided that they have been made testable using scan.

- Due to the scan path it requires simpler ATPG and has improved observability.

- Its overall hardware overhead is smaller than in test-perclock architectures, as it requires simpler test pattern generators for pseudorandom testing.

- In most cases, the BIST control of a test-per-scan scheme is simpler than the BIST control of a test-per-clock scheme.

The main advantage of parallel BIST is that it supports testing at the normal clock rate of the circuit, i.e., at speed testing.

This enables detection of faults that appear only at normal operational speed, such as transient faults in the power/ground lines caused by the switching of circuit lines. With a test-per-clock approach also a larger number of test patterns can be applied in a given test time, consequently a higher number of random pattern resistant faults could be detected. Therefore, test-per-scan architectures might require more complex TPGs, thus eliminating any advantage of the area overhead of serial BIST.

In the following, several BIST architectures will be described. We will describe architectures based on both paradigms, test-per-clock or *parallel BIST* and test-per-scan or *serial BIST*. Additional BIST architectures can be found in [3] and [12].

#### Parallel BIST Architectures

One of the first parallel BIST architectures was *built-in evaluation and self-test* (BEST). It is a simple architecture, where CUT inputs are driven by the PRPG and test responses are captured by a MISR, similar to Figure 2.6. This approach requires extensive fault simulation to determine an acceptable balance between fault coverage and test length, and might be ineffective for some circuits.

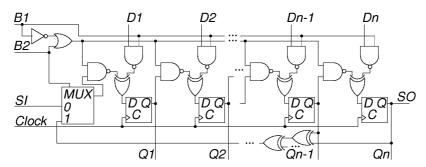

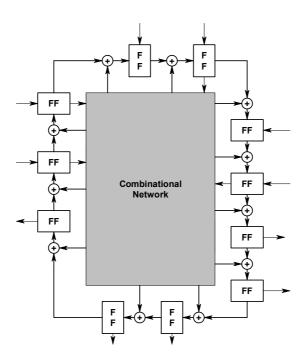

More widespread are built-in logic block observer (BILBO) and circular self-test path (CSTP) architectures. A BILBO register is a register that can operate both as a test pattern generator and as a signature analyzer [106] (Figure 2.11). In the test mode, the BILBO is configured as an LFSR or a MISR (Figure 2.12). A simple form of BILBO BIST architecture consists of partitioning a circuit into a set of registers and blocks of combinational logic, where the normal registers are replaced by BILBO registers.

Figure 2.11. n-bit BILBO register.

The synthesis of a test-per-clock scheme is implemented in the easiest way by a circular BIST or a circular self-test path (CSTP) [105] (Figure 2.13). The scheme has two modes, the system mode and the test mode, where the flip-flops form the LFSR. Two arbitrary flip-flops may be the scan-in and scan-out inputs. In the test mode, the system performs signature analysis and pattern generation concurrently, and only a single control line is required for the basic cells of this scheme. The disadvantage of this scheme is low fault coverage for some circuits.

Figure 2.12. BIST Design with BILBO registers.

Figure 2.13. Circular self-test path.

#### Serial BIST Architectures

We describe two main types of scan-based BIST architectures. In the first type, all primary inputs are connected to the taps of a pseudorandom generator and all primary outputs are connected to a MISR. All or a subset of state flip-flops are configured as scan chains, while the primary input flip-flop (scan-in signal) is connected to another LFSR and the primary output flip-flop (scan-out signal) is connected to a SLFSR. Examples of this architecture are *random test socket* (RTS) [11] and *partial scan BIST* (PS-BIST) [116].

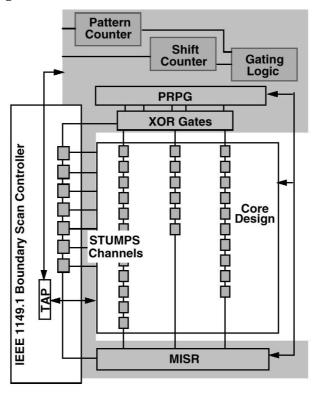

More efficient DFT approaches are modifications of these methodologies, such as Self-Test Using MISR and Parallel SRSG (STUMPS) [11] and LSSD on-chip self-test (LOCST) [112]. The

acronym SRSG (Shift Register Sequence Generator) may be considered as equivalent to PRPG, mentioned above.

The STUMPS architecture is shown in Figure 2.14. The basic assumption is that the memory elements of the CUT are included into the scan path. Often, a scan path is split into several scan chains. The multiplicity of scan chains speeds up test application, because the length of one test cycle is determined by the length of the scan path. At the same time, it equals only to the length of the longest scan chain for a CUT with multiple scan chains. However, there is always a trade-off: the more scan chains a core has the more scan inputs are required for it and thus longer LFSRs are needed.

**Figure 2.14.** Self-Test Using MISR and Parallel SRSG (© Mentor Graphics).

The general idea of the STUMPS approach is the following. PRPG, MISR and scan registers are clocked simultaneously. All scan registers are loaded from PRPG. This takes *SCL* clock cycles, where *SCL* is the length of the longest scan chain. After test application, the data captured by scan registers is scanned out, and the results are analyzed by a MISR.

The sequences obtained from adjacent bits of a parallel LFSR are not linearly independent; the neighboring scan chains contain test patterns that are highly correlated [24]. This can affect fault coverage negatively since the patterns seen by the CUT do not really form a random sequence.

## 2.7. Emerging Problems in System-on-Chip Testing

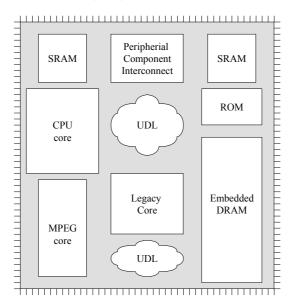

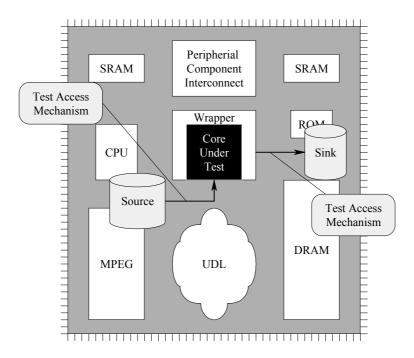

The latest advances in microelectronics manufacturing technology have enabled integration of an increasingly large number of transistors. This shift toward very deep submicron technologies facilitates implementation of an entire system on a single chip. Such systems are usually composed from a large number of different functional blocks, usually referred as cores. This kind of design style allows designers to reuse previous designs, which will lead therefore to shorter time-to-market, and reduced cost. Such a *system-on-chip* (SOC) approach is very attractive from the designers' perspective. Testing of such systems, on the other hand, is problematic and time consuming, mainly due to the resulting IC's complexity and the high integration density [127].

A typical SOC consists of many complex blocks (embedded cores, RAM, ROM, user-defined logic (UDL), analog blocks etc.) as depicted in Figure 2.15. Until recently such designs were implemented using several ICs mounted together into a printed circuit board (PCB) (also called as systems on board (SOB)). Using the SOCs instead of the PCBs gives a possibility to produce chips

with better performance, lower power consumption and smaller geometrical dimensions [175].

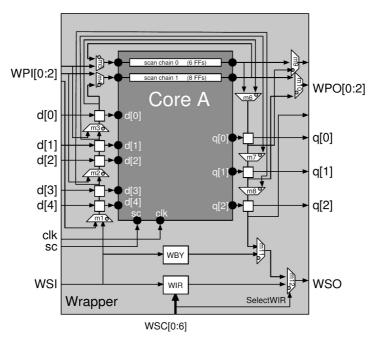

Figure 2.15. System-on-chip.

To cope with the difficulties to build such complex chips, a new design paradigm, called design reuse, has emerged. The main idea here is to use predefined and preverified reusable blocks to build up the chip. These reusable building blocks, so-called embedded cores, have several advantages. For example, in addition to reuse, embedded cores enable also import of an external design expertise, like high-end CPUs and DRAMs [118].

Embedded cores can be divided into three categories: soft, firm and hard [65]:

- Soft cores

- May be available as synthesizable, technology-independent, HDL descriptions (RTL or higher).

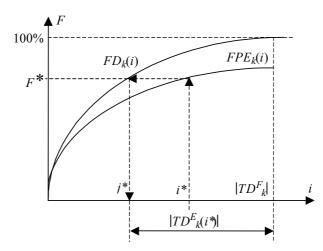

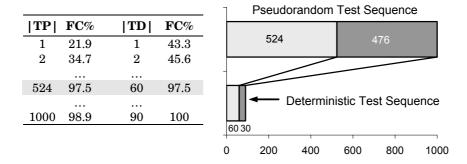

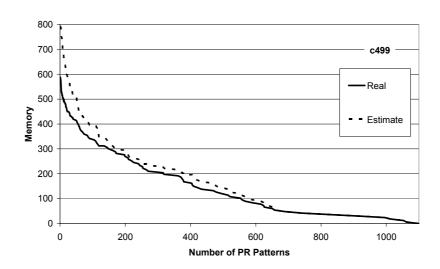

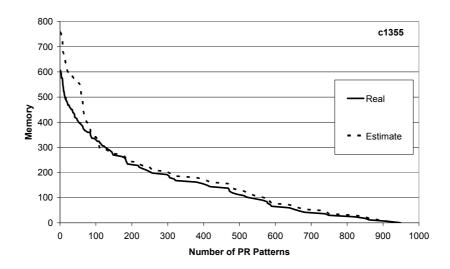

- Do not provide any protection for intellectual property.