Linköping Studies in Science and Technology

Dissertation No. 660

## An Integrated System-Level Design for Testability Methodology

by

## **Erik Larsson**

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

Linköping 2000

ISBN 91-7219-890-7 ISSN 0345-7524 To Eva and Knut

## Abstract

HARDWARE TESTING is commonly used to check whether faults exist in a digital system. Much research has been devoted to the development of advanced hardware testing techniques and methods to support design for testability (DFT). However, most existing DFT methods deal only with testability issues at low abstraction levels, while new modelling and design techniques have been developed for design at high abstraction levels due to the increasing complexity of digital systems.

The main objective of this thesis is to address test problems faced by the designer at the system level. Considering the testability issues at early design stages can reduce the test problems at lower abstraction levels and lead to the reduction of the total test cost. The objective is achieved by developing several new methods to help the designers to analyze the testability and improve it as well as to perform test scheduling and test access mechanism design.

The developed methods have been integrated into a systematic methodology for the testing of system-on-chip. The methodology consists of several efficient techniques to support test scheduling, test access mechanism design, test set selection, test parallelization and test resource placement. An optimization strategy has also been developed which minimizes test application time and test access mechanism cost, while considering constraints on tests, power consumption and test resources.

Several novel approaches to analyzing the testability of a system at behavioral level and register-transfer level have also been developed. Based on the analysis results, difficult-to-test parts of a design are identified and modified by transformations to improve testability of the whole system.

Extensive experiments, based on benchmark examples and industrial designs, have been carried out to demonstrate the usefulness and efficiency of the proposed methodology and techniques. The experimental results show clearly the advantages of considering testability in the early design stages at the system level.

## Acknowledgements

IT HAS BEEN an amazingly good time working with this thesis. Many people have contributed in different ways. I am grateful for this and I would like to acknowledge the support.

I was lucky to get the opportunity to join the Embedded System Laboratory (ESLAB). My supervisor Professor Zebo Peng has got a talent for creating a good working atmosphere. For my work, he gave me valuable guidelines and hints combined with much freedom. An important combination for me.

The present and former members of ESLAB and CADLAB have created a creative and enjoyable environment to be part of. It is a joy to be among such persons. Colleagues at IDA have also given a nice atmosphere to work in and I would especially like to mention the effort made by the department to support the graduate students.

I would like to thank Dr. Xinli Gu for the early cooperation presented in Chapter 9 and several members at the Electronics Systems group, ISY, who helped me with the Mentor Graphics tool set.

The research, funded by NUTEK<sup>1</sup>, has been carried out in close cooperation with the industry, especially with Gunnar Carlsson at CadLab Research Center, Ericsson. The cooperation and Gunnar's humble hints have provided me with many insights and a platform to demonstrate the developed techniques.

I am also happy to have the friends I have. And finally, I would like to mention my parents, Knut and Eva, and my brothers, Magnus and Bengt, who always have been the greatest support.

> Erik Larsson Linköping, November 2000

<sup>1.</sup> Swedish National Board for Industrial and Technical Development.

## Contents

| I Preliminaries                        | 1  |

|----------------------------------------|----|

| 1 Introduction                         | 3  |

| 1.1 Motivation                         | 4  |

| 1.2 Problem Formulation                | 6  |

| 1.3 Contributions                      | 7  |

| 1.4 Thesis Overview                    | 9  |

| 2 Background                           | 11 |

| 2.1 Introduction                       | 11 |

| 2.2 Design Representations             | 14 |

| 2.3 High-Level Synthesis               | 17 |

| 2.4 Testing and Design for Testability |    |

| II Test Scheduling and                 |    |

| Test Access Mechanism Design           | 27 |

| 3 Introduction and Related Work        | 29 |

| 3.1 Introduction                       | 29 |

| 3.2 Test Access Mechanism Design       | 35 |

| 3.3 Test Isolation and Test Access     |    |

| 3.4 Test Scheduling                    | 53 |

| 3.5 Test Set Selection                 | 64 |

| 4 Test Scheduling and                                                               |     |                           |    |

|-------------------------------------------------------------------------------------|-----|---------------------------|----|

| Test Access Mechanism Design4.1 Introduction4.2 System Modelling4.3 Test Scheduling | 69  |                           |    |

|                                                                                     |     | 4.4 Test Floor-planning   |    |

|                                                                                     |     | 4.5 Test Set              | 76 |

|                                                                                     |     | 4.6 Test Access Mechanism | 77 |

| 4.7 The System Test Algorithm                                                       | 84  |                           |    |

| 4.8 Simulated Annealing                                                             | 100 |                           |    |

| 4.9 Tabu Search                                                                     |     |                           |    |

| 4.10 Conclusions                                                                    | 103 |                           |    |

| 5 Experimental Results                                                              | 105 |                           |    |

| 5.1 Introduction                                                                    |     |                           |    |

| 5.2 Test Scheduling                                                                 |     |                           |    |

| 5.3 Test Access Mechanism Design                                                    |     |                           |    |

| 5.4 Test Scheduling and                                                             |     |                           |    |

| Test Access Mechanism Design                                                        | 122 |                           |    |

| 5.5 Test Parallelization                                                            | 136 |                           |    |

| 5.6 Test Resource Placement                                                         | 138 |                           |    |

| 5.7 Summary                                                                         | 142 |                           |    |

|                                                                                     |     |                           |    |

| III Testability Analysis and                                                        |     |                           |    |

| 6 Introduction and Related Work | 145 |

|---------------------------------|-----|

| 6.1 Testability Analysis        |     |

| 6.2 Testability Improvement     |     |

| 6.3 Summary                     |     |

## CONTENTS

| 7 Testability Analysis                                                                                                                                                                                                                                                                    | 177                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 7.1 Preliminaries                                                                                                                                                                                                                                                                         | 178                                                         |

| 7.2 Behavioral Testability Metrics                                                                                                                                                                                                                                                        | 178                                                         |

| 7.3 Application of the Behavioral Testability Metrics                                                                                                                                                                                                                                     | 184                                                         |

| 7.4 Behavioral Testability Analysis Algorithm                                                                                                                                                                                                                                             | 185                                                         |

| 7.5 Experimental Results                                                                                                                                                                                                                                                                  | 186                                                         |

| 7.6 Conclusions                                                                                                                                                                                                                                                                           | 193                                                         |

| 8 Testability Improvement Transformations                                                                                                                                                                                                                                                 | 195                                                         |

| 8.1 Basic Transformations                                                                                                                                                                                                                                                                 | 195                                                         |

| 8.2 Cost Function for DFT Selection                                                                                                                                                                                                                                                       | 200                                                         |

| 8.3 Application of the Testability                                                                                                                                                                                                                                                        |                                                             |

| Improvement Transformations                                                                                                                                                                                                                                                               | 202                                                         |

| 8.4 Experimental Results                                                                                                                                                                                                                                                                  | 208                                                         |

| 8.5 Variable Dependency                                                                                                                                                                                                                                                                   | 214                                                         |

| 8.6 Conclusions                                                                                                                                                                                                                                                                           | 218                                                         |

|                                                                                                                                                                                                                                                                                           |                                                             |

| 9 Testability Analysis and                                                                                                                                                                                                                                                                |                                                             |

| 9 Testability Analysis and<br>Enhancement of the Controller                                                                                                                                                                                                                               | 219                                                         |

|                                                                                                                                                                                                                                                                                           | ~                                                           |

| Enhancement of the Controller                                                                                                                                                                                                                                                             | 219                                                         |

| <b>Enhancement of the Controller</b><br>9.1 Introduction                                                                                                                                                                                                                                  | 219<br>220                                                  |

| <b>Enhancement of the Controller</b><br>9.1 Introduction<br>9.2 Preliminaries                                                                                                                                                                                                             | 219<br>220<br>223                                           |

| Enhancement of the Controller<br>9.1 Introduction<br>9.2 Preliminaries<br>9.3 Controller Testability Analysis                                                                                                                                                                             | 219<br>220<br>223<br>226                                    |

| Enhancement of the Controller<br>9.1 Introduction<br>9.2 Preliminaries<br>9.3 Controller Testability Analysis<br>9.4 State Reachability Analysis Algorithm                                                                                                                                | 219<br>220<br>223<br>226<br>229                             |

| Enhancement of the Controller9.1 Introduction                                                                                                                                                                                                                                             | 219<br>220<br>223<br>226<br>229<br>232                      |

| <ul> <li>Enhancement of the Controller</li> <li>9.1 Introduction</li> <li>9.2 Preliminaries</li> <li>9.3 Controller Testability Analysis</li> <li>9.4 State Reachability Analysis Algorithm</li> <li>9.5 Controller Testability Enhancements</li> <li>9.6 Experimental Results</li> </ul> | 219<br>220<br>223<br>226<br>229<br>232                      |

| Enhancement of the Controller9.1 Introduction                                                                                                                                                                                                                                             | 219<br>220<br>223<br>226<br>229<br>232<br>234               |

| Enhancement of the Controller         9.1 Introduction                                                                                                                                                                                                                                    | 219<br>220<br>223<br>226<br>229<br>232<br>234<br><b>235</b> |

## CONTENTS

| 11 Future Work                                 | 243 |

|------------------------------------------------|-----|

| 11.1 Estimation of Test Parameters             | 243 |

| 11.2 Test Scheduling and Test Access Mechanism | 244 |

| 11.3 Testability Analysis and                  |     |

| Testability Enhancements                       | 245 |

## V Appendix

## 249

| Appendix A      | 251  |

|-----------------|------|

| Design Kime     | 251  |

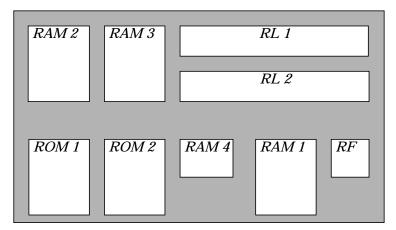

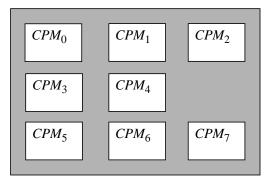

| System S        | 252  |

| Design Muresan  | 253  |

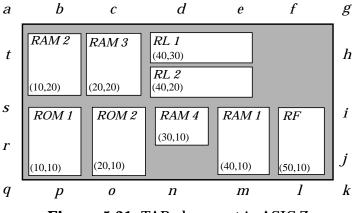

| ASIC Z          | 254  |

| Extended ASIC Z |      |

| System L        | 258  |

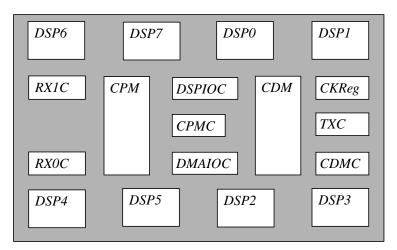

| Ericsson design | 258  |

|                 |      |

|                 | 0.07 |

## Bibliography

# Preliminaries

PART I

## Chapter 1 Introduction

THIS THESIS DEALS with the problems of hardware testing and focuses on problems at the early stage in the design process. Most previous work in hardware testing has mainly considered test problems at lower abstraction levels. However, the increasing complexity of digital designs has led to the development of new modelling techniques at higher and higher abstraction levels. Design tools operating at the high abstraction levels have been developed, but test and design for testability tools have not kept pace and testing of complex hardware structure remains a major problem.

The main aim of hardware testing is to detect physical faults introduced during or after production. It should be distinguished from hardware verification where the aim is to detect design errors. In hardware testing a set of test vectors are applied to the system and their responses are compared with expected responses. Due to the increasing complexity of digital systems, large systems are often partitioned to allow concurrent testing of different partitions.

In this thesis an integrated framework for testing system-onchip (SOC) including a set of algorithms is proposed. The objec-

tives are to minimize the total test application time and the test access mechanism while considering several issues. Constraints among tests and limitation on test power consumption, tester bandwidth and tester memory are considered. Further, the approach considers also the placement of test resources, test set selection and test parallelization for each block in the system.

It is also important to predict and improve testability as early as possible in the design process. In this thesis a technique to analyze testability and a transformation technique to improve it for a behavioral VHDL specification are defined. A technique to analyze the testability for a controller on register-transfer level and a technique to enhance its testability are also proposed.

The rest of this chapter is organized as follows. The motivation for the thesis is given in Section 1.1 followed by the problem formulation in Section 1.2. The contributions of the thesis are presented in Section 1.3 and finally an overview of the thesis is given in Section 1.4.

## 1.1 Motivation

The objective of hardware testing is to ensure fault-free electronic products and it is carried out after production and/or certain period of operation. Much work in modelling techniques and development of design tools has been performed at low abstraction levels such as the gate level. The increasing complexity of digital designs has led to the need for and the development of new modeling techniques and new design tools at higher abstraction levels. The prediction and enhancement of testability and the integration of testability at an early design stage are therefore becoming very important.

### INTRODUCTION

## 1.1.1 TEST SCHEDULING AND TEST ACCESS MECHANISM DESIGN

An effect of the increasing complexity of digital systems is increasing test application time. In order to minimize it, it is important to consider testability of a design at higher abstraction levels where the objective is to ensure that the final design is testable at a low cost.

Minimization of test application time is especially important for core-based designs. The core-based design approach is developed to handle the increasing design complexity. Cores which are developed by different design teams or purchased from different vendors, known as intellectual properties (IP) cores, are integrated usually into a single chip.

A test schedule for such a system determines the order of the tests and in order to minimize the total test time, several tests are to be scheduled concurrently. However, there may exist several types of constraint which reduces the ability for simultaneously execution of tests. Several test scheduling techniques have been proposed. However, most consider only a few issues. In order to give the designer an early overall feeling for the test problems and to allow the designer to efficiently explore the design space, it is important to consider many issues affecting the application time. Furthermore, an access mechanism for transporting test data in the system has to be designed at a minimal cost.

## **1.1.2 TESTABILITY ANALYSIS AND ENHANCEMENT**

In order to reduce the test generation and application complexity, it is important to consider and to predict testability of a design at higher abstraction levels in order to ensure that the final design is testable at a low cost. At higher abstraction levels the functional properties of the design can be explicitly captured and it can be used to speed up testability analysis. Such information is difficult to extract from a gate-level design.

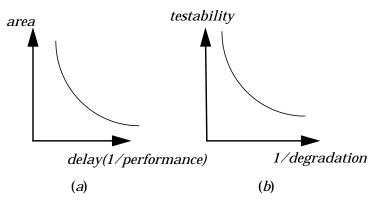

An introduction of a design-for-testability (DFT) technique in a system improves the testability but it may also introduce some degradation. It is therefore important to analyze the testability and find a trade-off between testability and design degradation. Several testability analysis approaches have been proposed. However, most are defined for low abstraction levels and those defined for higher abstraction levels, register-transfer level, usually only consider either the data path or the control part of the design.

Therefore a testability analysis technique considering the whole design at high abstraction level is needed. Furthermore, due to the fact that the feed-back loop structure is a major problem in hardware testing, the testability analysis approach must be capable of handling such structures. In order to make the testability analysis technique useful for the designer, the computational cost of the analysis technique must be reasonable.

## 1.2 Problem Formulation

The aim of our work is to reduce the testing cost, which is usually a large part of the production cost, when developing digital systems such as core-based systems. This thesis fulfils the objectives by considering:

- Test scheduling, which is an ordering of the tests.

- *Test access mechanism design*, the design of an infrastructure to transport test data in the system.

- *Testability analysis*, where the hard-to-test parts of the system are detected.

- *Testability improvement* where the detected hard-to-test parts are modified to be easier to test.

Our main goal is to develop efficient methods to improve the test quality at an early design stage. By test quality we mean fault coverage, test generation time and test application time. The

### INTRODUCTION

fault coverage is defined for the single stuck-at-fault model. By efficiency, we mean low computational time, low area overhead and small performance degradation. Early in the design stage refers to stages at register-transfer level and above.

The objective of reducing test application time is to be achieved by efficient test scheduling and the objective of reducing test generation time and improving fault coverage by highlevel testability enhancement technique. Since, the introduction of testability improvement techniques may also degrade the design in terms of extra area and/or extra delay, the developed testability analysis technique should be able to find a good trade-off between testability and design degradation.

## 1.3 Contributions

The main contributions of this thesis are as follows:

- A framework for the testing of system-on-chip (SOC), which includes a set of design algorithms to deal with test scheduling, test access mechanism design, test sets selection, test parallelization, and test resource placement. The approach minimizes the test application time and the test access mechanism cost while considering constraints on tests, power consumption and test resources.

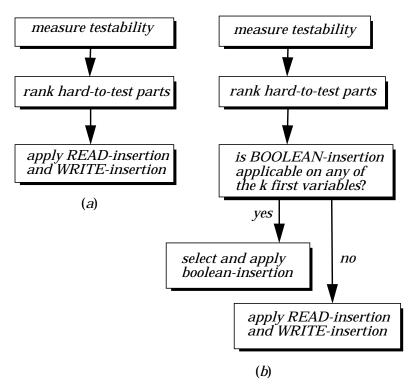

- A testability analysis technique to detect hard-to-test parts and a set of testability enhancement transformations to improve the testability and a selection strategy.

The rest of this section describes the contributions in more detail.

## 1.3.1 A FRAMEWORK FOR THE TESTING OF SYSTEM-ON-CHIP

In this thesis, a combined test scheduling and test access mechanism design approach is introduced. The approach minimizes the test application time while several factors are considered; these factors are: conflicts among tests, power limitations, test

resource placement, test parallelization and the minimization of the test access mechanism. Conflicts among tests include, for instance, sharing of test resources. These issues are of importance in the development of core-based system.

Experiments have been performed where the efficiency of the test scheduling technique has been shown. Its low computational cost allows it to be used for industrial designs. The test scheduling in combination with test access mechanism design has been investigated and an optimization technique is proposed. Furthermore, a technique for the placement of test resources is proposed.

Experiments have been performed to show the efficiency of the proposed approach. Regarding the test scheduling the proposed technique shows better results when comparing with other techniques in respect to test time and computational cost. The detailed experimental results could be found in [Lar99b], [Lar00a], [Lar00b], [Lar00c], [Lar00d] and [Lar00e].

### **1.3.2 TESTABILITY ANALYSIS AND ENHANCEMENT**

A testability analysis technique that detects hard-to-test parts at a high abstraction level design representation of a system has been developed. The analysis is based on a qualitative metrics. The advantage is that the designer gets an early feeling for the test problems and can use this information to improve the testability of the design. Another advantage of early considerations of testability is that functional properties are easier to be found in a high-level design representation compared to a gate-level design.

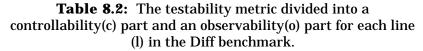

Our testability metric is a combination of variable range, operation testability and statement reachability. We show an application of the testability metrics for partial scan selection and we present an algorithm to calculate the metrics. We perform experiments to show correlation between our test metrics and the fault coverage. We compare our behavioral level analy-

#### INTRODUCTION

sis with a commercial gate-level tool and show that the hard-totest parts can be predicted accurately at the behavioral level.

We have focused on testability analysis and enhancement for the controller part of a digital design. The controller usually has a large impact on the testability of the whole design and by considering it the test problems for the whole design will be reduced. The controller metrics are based on statement reachability and the enhancement technique is based on loop termination, branch control and register initialization. We show by experiments that our enhancement technique improves the testability.

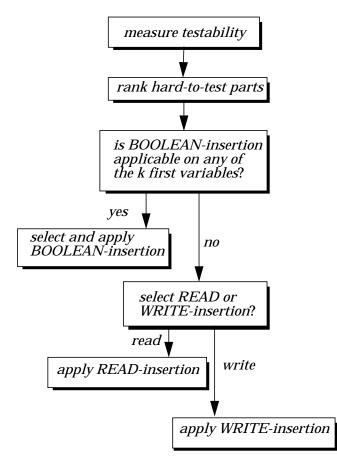

We propose a set of behavioral level testability transformations, which include write-insertion, read-insertion, booleaninsertion and reach-insertion, and a transformation selection strategy. The transformations are applicable directly on the behavioral VHDL specification and they do not impose any restrictions on the high-level synthesis process. We propose a selection strategy and by experiments we show the efficiency of our approach. We also present a partitioning scheme based on dependency among variables. By partitioning the variables it is possible to improve the testability for several hard-to-test parts in each design iteration. The work is reported in [Gu97], [Lar97], [Lar98a], [Lar98b], [Lar99a].

## 1.4 Thesis Overview

This thesis is divided into four parts:

- **Preliminaries**. A general background to hardware testing is described where the focus is on synthesis for testability as well as the basic terminology of testability techniques.

- **Test Scheduling and Test Access Mechanism Design**. In Part II, the background to the testing of system-on-chip (SOC) is given as well as an overview of related work. Followed by introducing the test scheduling and test access

mechanism design algorithms. An integrated framework including a set of design algorithms for testing of system-onchip. The aim of the test scheduling is to order the tests in the system to minimize the test application time while considering several important constraints. The test access mechanism algorithm minimizes the size of the infrastructure used for transportation of test data. An integrated approach is defined where test scheduling, test access mechanism design, test parallelization and test set selection are combined. Part II concludes with several experiments on benchmarks as well as on industrial designs.

- Testability Analysis and Testability Improvement Transformations. Part III opens with an overview of previous approaches to analyzing the design as well as techniques to improve the testability. The behavioral level testability metrics are given in Chapter 7, including an algorithm to calculate the metrics and we show an application of it for partial scan selection. The chapter concludes with experimental results where we show that our metrics detect hardto-test parts and that we can predict testability on the behavioral level. In Chapter 8 we propose a design transformation technique and a selection strategy that improves the testability of a behavioral specification. Experimental results are presented to show that the approach makes the design testable. In Chapter 9 a technique to analyze the testability of the controller and a technique to improve the testability are proposed. The analysis is based on statement reachability and the enhancement technique consists of loop breaking, branch control and register initialization. Through experiments we show that our approach improves testability.

- **Conclusions and Future Work**. In Part IV, the thesis concludes with conclusions and a discussion on future work.

## Chapter 2 Background

TESTABILITY HAS A LARGE impact on all stages in the design flow and much research has been devoted to it. This chapter gives the background and an introduction to modelling techniques and basic definitions and techniques used for design for test (DFT) ability.

After the introduction in Section 2.1, design representations are discussed in Section 2.2. In Section 2.3 high-level synthesis is discussed and the chapter concludes with a discussion on DFT, Section 2.4.

## 2.1 Introduction

The development of microelectronic technology has lead to the implementation of system-on-chip (SOC), where a complete system, consisting of several application specific integrated circuits (ASIC), microprocessors, memories and other intellectual properties (IP) blocks, is implemented on a single chip.

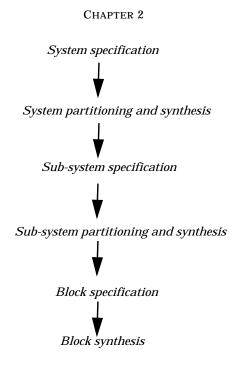

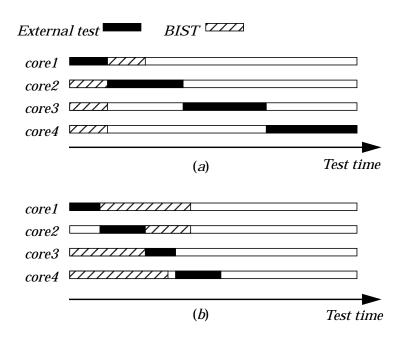

Designing such systems usually starts with a system specification where the system's functionality is captured, see Figure 2.1. The specification is partitioned and synthesised

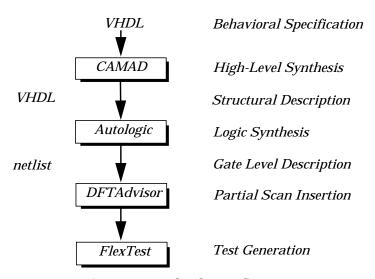

Figure 2.1: High-level design for digital systems.

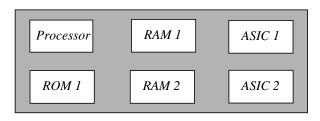

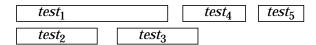

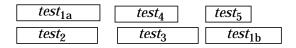

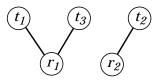

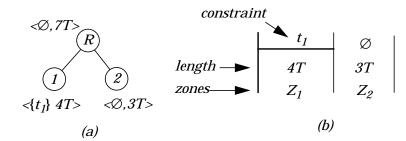

(implementation specific details are added) into sub-system specifications, see Figure 2.2 for an example. The sub-systems may be further partitioned into blocks and then a design flow as in Figure 2.3 may be applied on each block.

In order to reduce the design time complete sub-systems or blocks may be reused. When sub-systems or blocks are reused some steps in the design flow in Figure 2.3 may not be needed. For instance, assuming that the microprocessor in Figure 2.2 will be given as a structural specification due to the reuse of the previously designed microprocessor, then the high-level synthesis step is not performed.

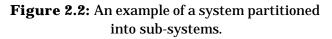

Modelling techniques at higher abstraction levels have been developed due to the increasing complexity of digital designs. In the design flow illustrated in Figure 2.3 three different abstraction levels are distinguished, behavioral, structural and gate

### BACKGROUND

Figure 2.3: The synthesis flow for basic blocks.

level. The design work can start with a sub-system or block captured in a behavioral specification which is transformed to a structural specification by the high-level synthesis process. The logic synthesis process transforms the structural specification to a layout which is sent for production.

In order to decrease the development time it is also common to reuse previously designed parts which are incorporated as subparts in the final system. These pre-designed parts, called cores, may be incorporated at any abstraction level. For instance if a processor is incorporated, it is usually delivered as a gate-level specification by the core provider.

When the design is completed, the system is manufactured and then production tests are performed to detect production errors. Testing of the system may also be performed during the operation and maintenance of it. Hardware testing may also be used to detect design errors. However, a test for all possible errors may require a large test effort. In order to minimize the test effort and maximize the test coverage, we have to consider the test problems during the design process.

## 2.2 Design Representations

During the design process, a system or a part of it can be described at different abstraction levels. At higher abstraction levels fewer implementation-specific properties are found, while at lower abstraction levels more implementation-specific properties are added. Since a model at a high abstraction level contains fewer implementation-specific details, it is less complex and easier to grasp for a designer than a model at a lower level.

In this section we will cover behavioral, structural and intermediate representations. System-level modelling techniques as proposed by Cortes *et al.* [Cor00] and gate-level formats are not covered.

### 2.2.1 BEHAVIORAL REPRESENTATION

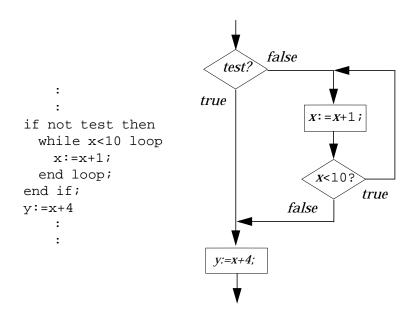

The design work starts with a behavioral representation. The term *behavioral representation* is used to reflect that the representation at this level only captures the behavior of the design. The required resources and implementation structure timing are not specified.

As an example, the CAMAD high-level synthesis tool, a research system developed by our research group, accepts as input a behavioral specification in VHDL [Ele92] or ADDL, Algorithmic Design Description Language [Fje92], [Pen94]. The latter was constructed especially for the CAMAD system. It is close to a subset of Pascal, with a few extensions [Fje92]. Some restrictions have been introduced in ADDL compared to full Pascal, motivated since it is to be used for hardware synthesis. Dynamic structures, files and recursion are not included in ADDL.

The extensions to Pascal are the use of *ports, modules* and *parallel statements.* A *port* is a connection to the external environment and a *module* is syntactically close to a procedure. However, a *module* is seen as a primitive operation mapped to a supposed hardware module. Parallel statements, enclosed by *cobegin* and *coend*, specify that the enclosed statements may execute in parallel, and synchronised at the *coend*.

## 2.2.2 STRUCTURAL REPRESENTATION

The structural representation, which is usually generated as the output of the high-level synthesis process, contains more implementation specific properties than the behavioral representation. From a representation at this level it is possible to derive the number of components and at what time (clock period) a certain operation is performed.

A structural representation captured in VHDL typically includes component instantiations, the way that the components are connected with each other with signals and a finite state

machine describing the controller. It is usually used as input to a logic synthesis tool.

For example, the subset of VHDL accepted by Mentor Graphics' synthesis tool, Autologic, includes several processes, variables, signals, functions, component declaration, etc. [Me93a], [Me93b]. However, only one wait-statement is accepted for each process.

Another limitation is that the bounds for loops must be known, *i.e.* no variable loop-statements, which means that all loops can be unrolled.

## 2.2.3 INTERMEDIATE REPRESENTATION

In high-level synthesis, where a structural representation is generated from a behavioral representation, it is common to first transform the behavioral representation to an intermediate representation to allow efficient design space exploration of different design alternatives.

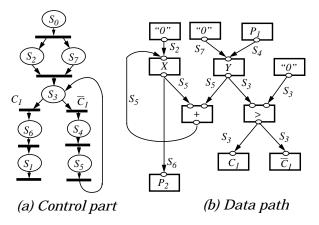

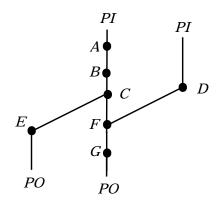

There exist several intermediate representations, such as the control flow graph, data flow graph and control/data flow graph [Gaj92]. We will here briefly describe a representation called Extended Timed Petri Net, ETPN [Pen94]. The ETPN representation is based on a data flow part that captures the data path operations and a control flow part that decides the partial ordering of data path operations.

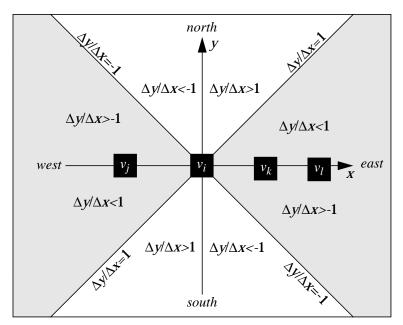

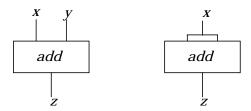

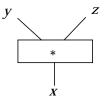

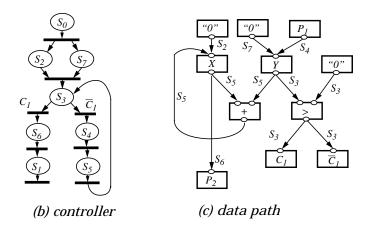

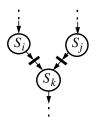

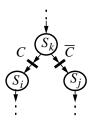

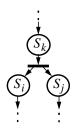

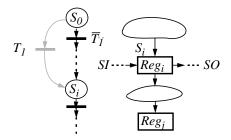

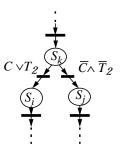

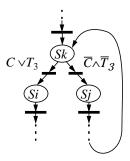

The control flow part is modelled by a Petri net notation and the data path by a directed graph where each vertex (node) has the possibility of multiple inputs and/or outputs, see Figure 2.4. In the figure, Petri net places (S-elements) are the circles while the transitions (T-elements) are the bars in Figure 2.4.

Initially a token is placed at  $S_0$ , which is an initial place, see Figure 2.4. A transition is enabled if all its input places have at least one token and it may be fired when the transition is enabled and the guard condition is true. Firing an enabled transition removes a token from each of its input places and deposits a

Figure 2.4: An example of ETPN.

token in each of its output places. If no token exists in any of the places, the execution is terminated.

When a place holds a token, its associated arcs in the data path will open for data to flow. For instance when place  $S_2$  holds a token, the edges controlled by  $S_2$  in the data path activate and data is moved.

Some of the intermediate representations are close to behavioral representations, while others are closer to structural representations. For instance, data flow graphs and control data flow graphs can be placed in the former class, while representations given as ETPN belong to the latter. With the ETPN it is possible to analyze the number of modules needed for the data path and the partial order of operations.

## 2.3 High-Level Synthesis

High-level synthesis is the transformation of a behavioral representation into a structural implementation [Gaj92]. It consists mainly of highly dependent, but usually treated as separated, tasks, namely scheduling, allocation and binding of operations to components to fulfill some given design constraint.

Scheduling is basically assignment of operations to a time slots, or control step, which corresponds to a certain clock cycle. If several operations are assigned to the same control steps, several functional units are needed. This results in fewer control steps, which results in a faster design, but also leads to more expensive circuits [Gaj92].

The allocation task is to select the number and types of hardware units to be used in a design. Sharing of hardware resources reduces the design size but it is only allowed if the units are not used by different operations at the same time. Binding deals with the operations mapping to a certain module library components.

High-level synthesis has traditionally been considered as an optimization of a two-dimensional design space defined by area and performance. However, recently the design space has been extended to include power consumption [Gru00] and testability, as well as other criteria such as timing constraints [Hal98].

A popular approach to high-level synthesis is the transformation-based approach which starts with a naive initial solution. The solution is improved by applying transformations until a solution that is close to the optimal solution and that fulfils the given constraints is found.

## 2.4 Testing and Design for Testability

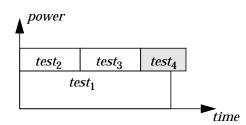

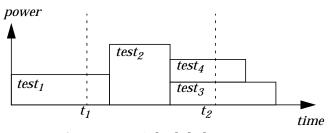

In this section testing and design for testability (DFT) are introduced. These are important for the testing of SOCs and, further, for SOCs the volume of test data (test vectors and test response) is increasing leading to high total test application time. Therefore, it is important to consider the transportation of test data and the scheduling of tests. The test application time depends on the bandwidth of the test access mechanism and how efficient the tests are ordered (scheduled).

### BACKGROUND

A test access mechanism is used for the transportation of test vectors and test responses. Test vectors have to be transported from the test sources (test generators) to the blocks under test and the test responses have to be transported from the blocks under test to the test sink (test response evaluators). The size of the access mechanism depends on the placement of test resources and the bandwidth.

An efficient test schedule orders the tests in such order that the test application time is minimized.

Faults and fault models are discussed in Section 2.4.1 followed by a discussion of test generation in Section 2.4.2. Techniques for improving the testability such as test point insertion, scan, built-in self-test and test synthesis are described in Section 2.4.3.

## 2.4.1 FAULTS AND FAULT MODELS

The cost of testing includes costs related to issues such as test pattern generation, fault simulation, generation of fault location information, cost of test equipment and the test process itself, which is the time required to detect and/or isolate a fault.

The test cost can be reduced by using some DFT technique. However, a DFT technique may result in some performance degradation and/or some area overhead. The most important consideration when applying a DFT technique is the selection of places to apply the DFT technique and the trade-off between testability and the performance/area penalty.

The selection of hard-to-test parts includes a trade-off between accuracy in finding the hard-to-test parts and computational complexity.

A produced VLSI chip may contain several types of physical defects, such as a broken or missing wire, a wire which is wrongly connected to another wire. Some of the defects are present directly after production, while others may occur after some operation time.

Logical faults are commonly used to model physical defects [Abr90]. The most commonly used fault model is the single stuck-fault (SSF) model, which assumes that the design only contains one fault. It also assumes that when a fault is present, at a point, it is either permanently connected to 1 (stuck at 1 fault) or permanently connected to 0 (stuck at 0 fault). A test detects a fault in a circuit if the output of the fault-free circuit is different from the output of the faulty one.

The main advantage of the SSF model is that it represents many different physical defects, and it is technology-independent. Experience has also shown that SSF detects many physical defects. Further, using the SSF model the number of faults is low compared with other models [Abr90]. A design with *n* lines results in  $2^*n$  faults.

The *fault coverage* or *test coverage* is used to indicate the quality of tests with a given fault model [Tsu88]. The fault coverage, *f*, is defined as:

$$f = \frac{n}{N} \tag{2.1}$$

where n is the number of faults detected by the given test set [Abr90]. N is the total number of faults defined by the given fault model.

## 2.4.2 TEST GENERATION

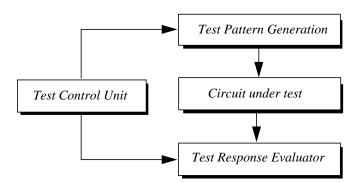

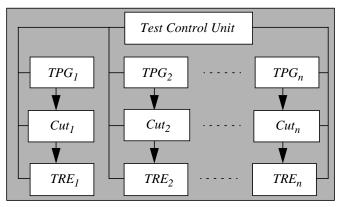

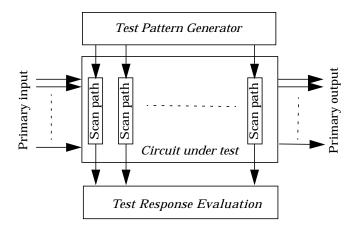

A system is tested by applying a set of test pattern (vectors/stimuli) on its primary inputs and then compare the test response on its primary outputs with know good vectors. An illustration in Figure 2.5 shows a *test control unit* which controls the *test pattern generator* and the *test response evaluator*.

Traditionally the test patterns are supplied from an external tester. However, due to the increasing capacity of the integrated circuit technology, a complete system consisting of several complex blocks can be integrated on a single chip. One of the advantages of this integration is that the performance can increase

### BACKGROUND

Figure 2.5: General view of a circuit under test.

mainly because there is no chip-to-chip connection which used to be a major performance bottle-neck. Due to the increasing performance of systems and the limitation of bandwidth when using external testers, there is a trend in moving the main functions of the external tester onto the chip. This would mean that all blocks in Figure 2.5 are placed on chip.

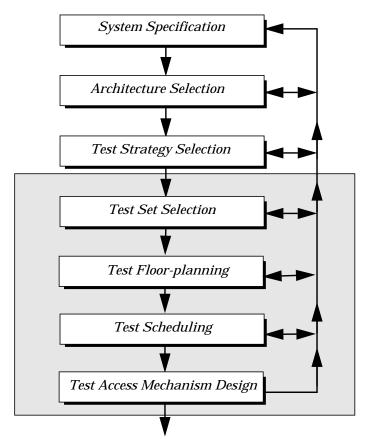

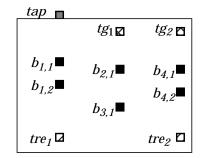

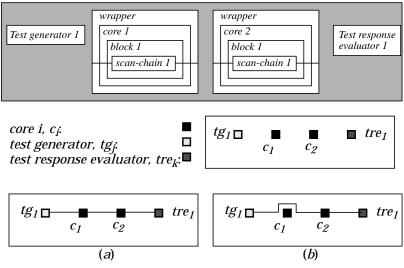

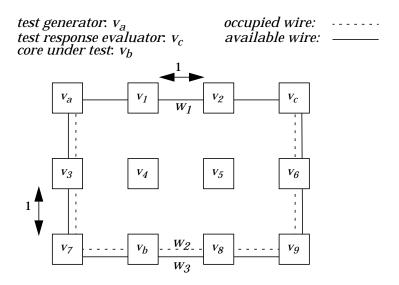

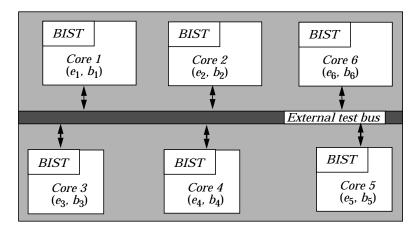

Furthermore, for large systems, it is not feasible to have only one test pattern generator and one test response evaluator as in Figure 2.5. An example of a system with several test pattern generators and test response evaluator is given in Figure 2.6.

The test generators are often of different types with their own advantages and disadvantages. For instance,  $TPG_1$  and  $TPG_2$ can be of different types in order to fit respectively circuit-undertest. One approach to minimizing test application time while keeping test quality high (fault coverage) is to allow a flexibility where each circuit under test is to be tested by several test sets from different test generators.

## 2.4.3 TESTABILITY IMPROVEMENT TECHNIQUES

Several techniques are used to improve the testability of a digital circuit. In this section we will present several of them, including test point insertion, scan technique, built-in self-test (BIST), and high-level test synthesis.

Figure 2.6: General view of a circuit under test.

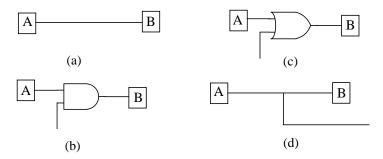

## Test Point Insertion

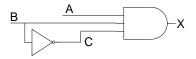

Test point insertion is a simple and straightforward approach to increasing the controllability and/or observability of a design. In Figure 2.7(a) a line (wire) between two components is shown. The ability to set the value of the line (wire) to 0 is enhanced by adding a 0-controllability test point. That is, an extra primary input and an AND-gate are added, see Figure 2.7(b). The 1-controllability, the ability to set a line to 1, is enhanced by adding an extra primary input and an OR-gate, Figure 2.7(c). To increase the observability of the line an extra primary output is added, Figure 2.7(d).

The main advantage of test point insertion is that the technique can be applied to any line in the design. However, the drawback is the large demand for extra primary inputs and outputs. The technique also requires extra gates and extra lines which introduce additional delay.

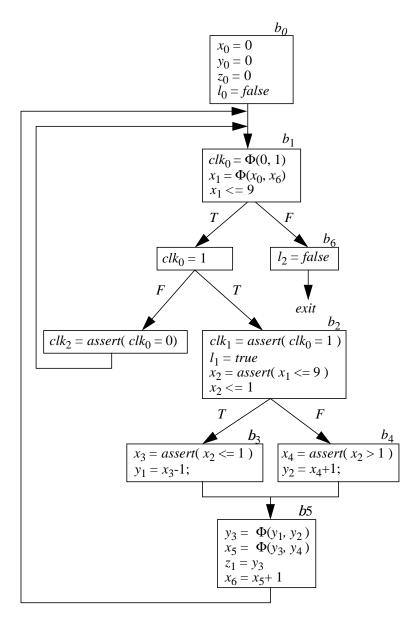

### Scan Technique

The main problem for test pattern generation is usually due to the sequential parts of the design. The scan technique is a widely used technique that turns a sequential circuit into a BACKGROUND

**Figure 2.7:** Test points for control and observation enhancement.

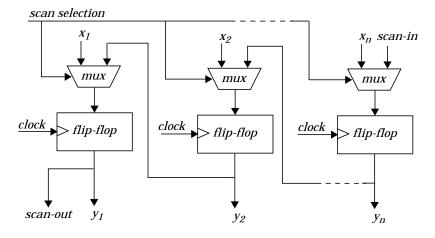

purely combinational one for which it is easier to generate test patterns. The scan technique enhances controllability and observability by only introducing two extra primary inputs (one for test data input and one for test enable), and one extra primary output used for test data output. In the test mode the flipflops in the design are connected to form a shift register. When the design is in the test mode, data is shifted into the design by one of the extra inputs. The circuit then runs for one clock cycle and the data captured at the flip-flops are shifted out on the added primary output.

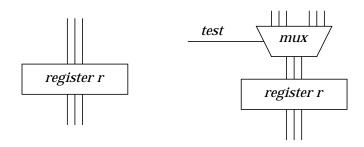

The basic idea behind the scan technique is illustrated in Figure 2.8. Using the signal *scan selection* the register can be controlled in two modes, the normal mode or the test mode. In the test mode the scan-in is active and the contents of the flip-flops are easily set. The value stored in the flip-flop is also easily observed on the scan-out line. When all flip-flops are connected to form one or more scan chains it is called full scan. In such cases all flip-flops are *scan controllable* and *scan observable*, which turns them into *pseudo-primary inputs* and *pseudo-primary outputs*, respectively [Ste00]. The advantage is that combinational logic and the register cells in the scan chain can be completely tested. Full scan converts the problem of testing a sequential circuit into that of testing a combinational circuit.

Figure 2.8: The basic idea for scan technique.

The testing of a combinational circuit is easier than the testing of a sequential one mainly since in the latter case test patterns must be applied at different states and changing from one state may require several intermediate steps. Furthermore, if a global reset is not available, an initialization sequence or state identification process is required making the problem even harder.

The overhead introduced by using the scan technique includes routing of new lines, more complex flip-flops, and three additional I/O pins. The overall clock speed may have to be reduced due to the additional logic in the flip-flops [Abr93]. The test application time may increase since a long scan chain requires many clock cycles to scan in the test vectors and scan out the test response. This can be solved by a faster scan clock or by dividing the scan chain into several shorter chains, which is called parallelization. However, these two solutions entail certain penalties. The fast scan clock needs extra area and the division of the scan chain leads to extra primary inputs and primary outputs.

The overhead introduced by using the full scan technique may be too high. Partial scan is a technique where only a subset of the flip-flops in the design are connected in the scan chain. This is done in order to have a good trade-off between the testability of the circuit and the overhead induced by scan design.

### Built-In Self-Test

When the scan technique is used, the test vectors are typically applied from the outside of the chip under test by a tester, see Figure 2.9. However, the Built-In Self-Test (BIST) technique does not require any external test equipment. Instead the test pattern generator, response analyser and test controller are integrated into the design. This may be achieved as shown in Figure 2.9 by integrating the test resources into the system which allow tests to be performed at any time since the test resources are built into the system. Another advantage of BIST is that the technique does not suffer from the bandwidth limitations which exist for external testers.

In order to further minimize test application time, the scan chains may be replaced and all registers are turned into test generations and/or test analysers. In such an approach, a new test may be applied in each clock cycle, *test-per-clock*. Compare with the scan approach where each test vector has to be scanned in, *test-per-scan*. The test pattern generator can be implemented as a *linear feed-back shift register* (LFSR) and the response analyser as a *multiple input signature register* (MISR). A built-in logic block observer (BILBO) is a register which can operate both as a test pattern generator and a signature analyser. However, the disadvantage of using BILBOs is the large area and delay penalty [Wag96].

An advantage of using the BIST technique is that tests are performed at speed. The technique also has a lower test application time compared to the scan technique.

Since the BIST technique does not require any special test equipment, it can be used not only for production test, but also for field test, to diagnose faults in field-replaceable units.

Figure 2.9: Testers for Scan Paths.

In order to minimize overhead, the BIST technique usually uses compaction of test response. This also leads to a loss of information. A disadvantage is that the ability to evaluate the test efficiency is rather limited. Usually BIST using Pseudo-random generated test vectors only produces a signal indicating error or no error [Tsu88].

## Test Synthesis

The above DFT approaches mean usually that additional testrelated hardware is added to an existing design. In test synthesis the primary goal is to perform the synthesis task in such way that the produced output achieves good testability while keeping area and performance overhead under a given constraint. The high-level synthesis tasks, scheduling, allocation and binding, are performed to achieve a testable design. However, due to the increasing complexity of digital designs, the size of the design space increases. Therefore, it is important to define efficient testability analysis algorithms which are used to guide the test synthesis. Based on the results from testability analysis the high-level synthesis can be guided to generate testable designs.

# Test Scheduling and Test Access Mechanism Design

# PART I

# Chapter 3 Introduction and Related Work

THE SYSTEM-ON-CHIP TECHNIQUE makes it possible to integrate a complex system on a single chip. The technique introduces new possibilities but also challenges, where one major challenge is the testing of such complex system. This chapter gives an overview of research and techniques for system-on-chip testing.

# 3.1 Introduction

The development of microelectronic technology has lead to the implementation of system-on-chip (SOC), where a complete system is integrated on a single chip. Such a system is usually made more testable by the introduction of some design for testability (DFT) mechanisms.

Several DFT techniques such as test point insertion, scan and different types of built-in self-test (BIST) have been used for SOC testing. For complex SOC design several test techniques may have to be used at the same time since they all have their

respective advantages and disadvantages. Furthermore, when IP-blocks are used, they may already contain a test mechanism which is different from the rest of the design and it has to be incorporated in the overall test strategy of the whole system.

There are many similarities in testing PCBs (printed circuit board) and SOCs. The major difference is however twofold. For PCB, testing of each individual component can often be carried out before mounting on the board and the components can be accessed for test via probing. Neither of these is possible when testing SOCs. This means that testing the completed system, in the context of SOC, becomes even more crucial and difficult.

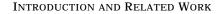

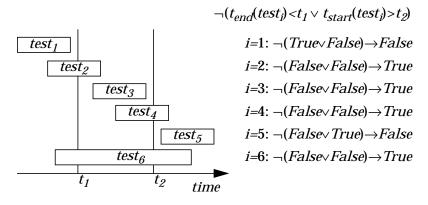

One main problem of testing SOCs is the long test application time due to the complex design and the need for large amount of test patterns. In order to keep test application time to a minimum, it is desirable to apply as many tests as possible concurrently. However, there are a number of factors that constrain concurrent application of several tests, which include:

- Power consumption,

- Test set selection,

- Test resource limitations,

- Test resource floor-planning,

- Test access mechanism, and

- Conflicts among tests.

In the rest of this chapter, we will analyze the implication of these factors.

#### 3.1.1 POWER CONSUMPTION

The power consumption during test is usually higher than during the normal operation mode of a circuit due to the increased number of switches per node which is desirable in order to detect as many faults as possible in the minimum of time [Her98]. However, the high power consumption may damage the system, because it generates extensive heat. The power dissipation in a CMOS circuit consists of a static and a dynamic part. The static power dissipation is derived from leakage current or other current drawn continuously from the power supply, and the dynamic power dissipation is due to switching transient current and charging and discharging of load capacitances [Wes92].

The static power dissipation and the dissipation due to switching transient current are negligible compared to the dissipation due to loading and unloading of capacitances, which is given by [Wes92]:

$$P_{dyn} = \frac{1}{2} \times V^2 \times C \times f \times a \tag{3.1}$$

where *V* is the voltage, *C* is the capacitance, *f* is the clock frequency and *a* is the switching activity.

All parameters but the switching activity in formula (3.1) can be estimated using a design library. The switching activity depends on the input data and there are two main approaches to estimating it, based on simulation or probability. During testing the input to the design consists of the test vectors and it is possible to make use of the test vectors generated by an ATPG tool to estimate the switch activity for a circuit under test. An approach where the test vectors are ordered based on Hamming distance has been proposed by Girard *et al.* [Gir98].

Zorian and Chou *et al.* use an additive model for estimating the power consumption [Zor93] [Cho97]. The power dissipation for a test session  $s_i$  is defined as:

$$P(s_j) = \sum_{t_i \in s_j} P(t_i)$$

(3.2)

where  $t_i$  is a test scheduled in test session  $s_i$ .

The power dissipation is usually considered to originate from gates. However, power may dissipate not only from blocks but also from large buses. For instance, for a wire of length 10 mm the capacitance will be about 7 pF [Eri00]. In calculation of power consumption, the average capacitance should be used,

which is close to half of the worst-case capacitance [Eri00]. Assume a system running at 100 Mhz where the average switch activity (frequency) is 25 MHz for random input data. At 2 volts the power consumption is calculated by using formula 3.1:

$$P = \frac{1}{2} \times C \times V^{2} \times f \times \alpha = \frac{1}{2} \times 3.5 \times 10^{-12} \times 2^{2} \times 25 \times 10^{6} = 0.175 \, mW$$

In a realistic example the width of the data bus from the memory is 512 bits which results in a power dissipation of 90 mW ( $512 \times 0.175=89.6$ ).

## 3.1.2 TEST RESOURCES

The test control unit controls the test resources which are either generators (sources) or analysers (sinks). The test stimuli (vectors/patterns) is created or stored at a test source and the test response is evaluated at a test sink. The test stimuli set is basically generated using the following four approaches namely:

- exhaustive,

- random,

- pseudo-random, and

- deterministic.

The basic ideas behind them and their advantages and disadvantages are outlined below.

## Exhaustive-based test generation

An exhaustive test set includes all possible patterns. This is easily implemented using a counter. The area-overhead and design complexity is low and it is feasible to place such a generator onchip. However, the approach is often not feasible since the number of possible patterns is too high: for a *n*-bit input design  $2^n$  patterns are generated which results in extremely long test application time.

#### INTRODUCTION AND RELATED WORK

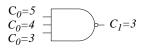

Figure 3.1: A 4-input AND-gate.

## Random-based test generation

Another approach is to use the random-based techniques. The draw-back with randomly generated test patterns is that some patterns are hard to achieve. For instance, generating a test pattern that creates a one on the output of an AND gate is only achieved when all inputs are one; the probability is  $1/2^n$ . For a 4-bit AND-gate the probability is only 0.0625 ( $1/2^4$ ), Figure 3.1. This means that a large set of test vectors has to be generated in order to achieve high fault coverage, which leads to long test application time.

## Pseudo-random-based test generation

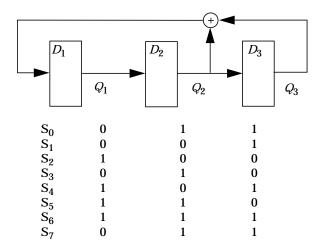

A pseudo-random test pattern set can be achieved using a *linear feedback shift register* (LFSR). An advantage is their reasonable design complexity and low area overhead which allow on-chip implementation. An example of an LFSR is shown in Figure 3.2 where one module-2 adder and three flip-flops are used. The sequence can be tuned by defining the feedback function to suit the block under test.

## Deterministic test generation

A deterministic test vector set is created using an *automatic test pattern generator* (ATPG) tool where the structure of the circuit under test is analysed and based on this analysis, test vectors are created. The size of the test vector set is relatively small compared to other techniques, which reduces test application time. However, the generated test vector set has to be applied to

Figure 3.2: Example of 3-stage linear feedback shift register based on  $x^3+x+1$  and generated sequence where  $S_0$  is the initial state.

the circuit using an external tester since it is inefficient to store the test vector set in a memory on the chip. The external testers have the following limitations [Het99]:

- Scan usually operates at a maximum frequency of 50 MHz,

- Tester memory is usually very limited, and

- It can support a maximum of 8 scan chains, resulting in long test application time for large designs.

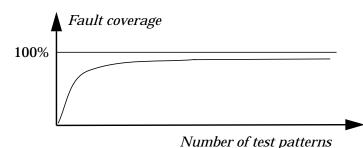

A graph with the fault coverage as a function of the number of test patterns is shown in Figure 3.3. Initially the fault coverage increases rapidly due to that faults easy to detect are detected. However, in the end few faults are detected due to the fact that the remaining faults, the random-resistant faults, are hard for an LSFT to detect. This curve applies in general to all test generation techniques. However, the faults that are hard to detect may be different for different techniques. Therefore, approaches where several test sets are generated for a block with different

**Figure 3.3:** Fault coverage function of test patterns.

test resources (different techniques) in order to detect all faults in a minimum of test application time have been developed. For example, Jervan *et al.* propose a Hybrid BIST [Jer00].

## **3.1.3 TEST CONFLICTS**

Tests may not be scheduled concurrently due to several types of conflicts. For instance, assume that the core in a wrapper is tested by two tests where one uses the external test source and test sink while the other uses the on-chip test source and test sink. These two test can not be scheduled concurrently since they both target the same logic.

# 3.2 Test Access Mechanism Design

A test infrastructure consists of two parts. One part for the transportation of test data and another part which controls the transportation.

In a fully BISTed system where each block in the system has its own dedicated test resources, no test data is needed to be transported. Only an infrastructure controlling the tests is required. Zorian proposes a technique for such systems [Zor93]. Håkegård's approach can also be used to synthesize a test controller for this purpose [Håk98].

Figure 3.4: Test sources and sinks.

The test data transportation mechanism transports test data to and from the cores in the system (Figure 3.4). Due to the increasing complexity of systems, the amount of test data to be transported is becoming substantial. Research has focused on test infrastructure optimization in order to minimize the total test application time.

The test application time for *multiplexed*, *daisychain* and *distributed* scan chain architectures are investigated by Aertes *et al.* [Aer98].

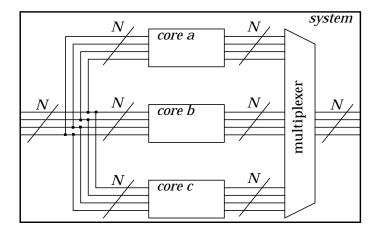

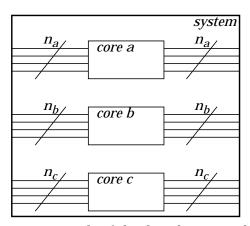

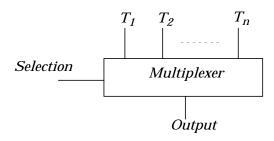

In a *multiplexed architecture*, see Figure 3.5, all cores are assigned to all available scan bandwidth, *i.e.* all cores are connected to all scan inputs and all scan outputs of the system. At any moment, only one core can use the outputs due to multiplexing. The result is that the cores have to be tested in sequence.

For the discussion on multiplexed, daisychain and distributed architecture the following is assumed to be given for each core *i* in the system:

*f;* the number of scannable flip-flops,

$p_i$ : the number of test patterns, and

*N*: the scan bandwidth for the system, maximal number of scan-chains.

Figure 3.5: Example of the multiplexer architecture.

In scan-based systems it is common to use a pipelined approach where the test response from one pattern is scanned out, the next pattern is scanned in simultaneously. The test application time  $t_i$  for a core i is given by:

$$t_i = \left\lceil \frac{f_i}{n_i} \right\rceil \cdot (p_i + 1) + p_i$$

(3.3)

In the muliplexed architecture  $n_i = N$ . The term +1 in Equation (3.3) is added due to the fact that the pipelining can not be used for scanning out the last pattern.

The pipelining approach can be used when several cores are tested in a sequence. While the first pattern is scanned in for a core, the test response from last pattern can be scanned out for the previous core under test. The test application time using the multiplexed architecture is given by:

$$T = \sum_{i \in C} \left( p_i \cdot \left[ \frac{f_i}{N} \right] + p_i \right) + max_{i \in C} \left[ \frac{f_i}{N} \right]$$

(3.4)

where the maximum results from filling the largest core.

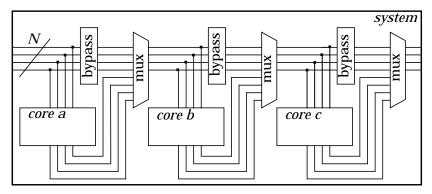

In the *daisychain architecture*, Figure 3.6, a bypass structure is added to shorten the access path for individual cores. The

Figure 3.6: Example of the daisychain architecture.

bypass register and 2-to-1 multiplexer allow flexible access to individual cores which can be accessed using the internal scan chain of the cores and/or by using the bypass structure.

The bypass offers an optional way to access cores and a bypass selection strategy is proposed by Aertes *et al.* [Aer98], where all cores are tested simultaneously by rearranging the test vectors. The approach starts by not using any of the bypass structures and all cores are tested simultaneously. At the time when the test of a core is completed, its bypass is used for the rest of the tests. Due to the delay of the bypass registers, this approach is more efficient compared to testing all cores in sequence.

Assume the system in Figure 3.6 where  $p_a=10$ ,  $p_b=20$ ,  $p_c=30$  and  $f_a=f_b=f_c=10$ . When the cores are tested in a sequence the test time of the system is 720  $(10\cdot(10+1+1)+(20\cdot(10+1+1)+(30\cdot(10+1+1))))$ . Note that the terms +1+1 are due to the bypass registers. However, using the approach proposed by Aertes *et al.*, the test time for the system is reduced to 630  $(10\cdot30+10\cdot(20+1)+10\cdot(10+1+1))$ .

The test application using this scheme is given by:

$$T = \sum_{i=1}^{|C|} \left( (p_i - p_{i-1}) \cdot \left( i - 1 + \sum_{j=i}^{|C|} \left\lceil \frac{f_j}{N} \right\rceil \right) \right) + p_{|C|}$$

(3.5)

where  $p_0 = -1$ .

#### INTRODUCTION AND RELATED WORK

Figure 3.7: Example of the distribution architecture.

Note that the indices in Equation (3.5) are rearranged into a non-decreasing number of patterns.

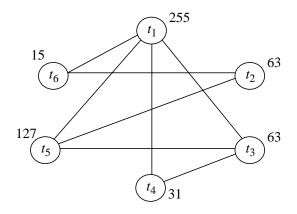

In the distributed architecture each core is given a number of scan chains, Figure 3.7. The problem is to assign scan chains to each core *i* in order to minimize the test time, *i.e.* assign values to  $n_i$  where  $0 < n \leq N$ .

The test application time for a core i in the distribution architect is given by Equation (3.3) and the total test time for the system is given by:

$$T = max_{i \in C}(t_i) \tag{3.6}$$

An algorithm is proposed to assign the bandwidth  $n_i$  for each core *i*, Figure 3.8., where the goal is to find a distribution of scan chains such that the test time of the system is minimized while all cores are accessed, expressed as:

$$min_{\bar{n} \in N^{|C|}}(max_{i \in C}(t_i)), \sum_{i \in C} n_i \le N \land \forall i \in C\{n_i > 0\}$$

$$(3.7)$$

The algorithm presented in Figure 3.8 works as follows. Each core is assigned to one scan-chain which is required to test the system. In each iteration of the loop, the core with the highest test time is selected and another scan chain is distributed to the

Figure 3.8: Algorithm for scan chain distribution.

core which reduces its test time. The iterations are terminated when no more scan chains can be distributed.

Given an SOC and the maximum total test bus width, the distribution of test bus width to the cores in the system is investigated by Chakrabarty [Ch00a].

# 3.3 Test Isolation and Test Access

For SOC testing, a test access mechanism or a test infrastructure is usually added to the chip in order to facilitate test access and test isolation. Its purpose is to feed the SOC with test data. Furthermore, its design is important due to the fact that it may influence the possibility of executing test concurrently in order to minimize test application time. A test access mechanism is also needed for testing printed circuit boards (PCB).

For PCB designs the Boundary-scan test (IEEE 1149.1) standard has been defined and for SOC designs Boundary-scan (IEEE 1149.1), TestShell and P1500 may be applicable. In this section the Boundary-scan is described briefly and an overview of the TestShell approach and the P1500 proposal is given.

#### 3.3.1 THE BOUNDARY-SCAN STANDARDS

The main objective of PCB testing is to ensure a proper mounting of components and correct interconnections between components. One way to achieve this objective is to add shift registers next to each input/output (I/O) pin of the component to ease test access.

The IEEE 1149.1 standard for the Standard Test Access Port and Boundary-scan Architecture deals primarily with the use of an on-board test bus and the protocol associated with it. It includes elements for controlling the bus, I/O ports for connecting the chip with the bus and some on-chip control logic to interface the test bus with the DFT hardware of the chip [Abr90]. In addition, the IEEE 1149.1 standard requires Boundary-scan registers on the chip.

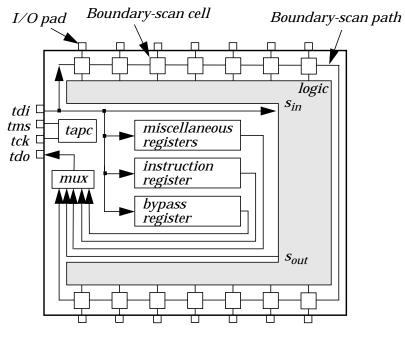

A general form of a chip with support for 1149.1 is shown in Figure 3.9 with the basic hardware elements: *test access port* (TAP), *TAP controller, instruction register* (IR), and a group of *test data registers* (TDRs) [Ble93].

The TAP provides access to many of the test support functions built into a component and it consists of four inputs of which one is optional and a single output: the *test clock input* (TCK) which allows the Boundary-scan part of the component to operate synchronously and independently of the built-in system clock; the *test mode select input* (TMS) is interpreted by the TAP Controller to control the test operations; *the test data input* (TDI) feeds the instruction register or the test data registers serially with data depending on the TAP controller; *the test reset input* (TRST) is an optional input which is used to force the controller logic to the reset state independently of TCK and TMS signals; and the *test data output* (TDO). Depending on the state of the TAP controller, the contents of either the instruction register or a data register is serially shifted out on TDO.

Figure 3.9: An example of chip architecture for IEEE 1149.1.

The TAP controller, named *tapc* in Figure 3.9, is a synchronous finite-state machine which generates clock and control signals for the instruction register and the test data registers.

The test instructions can be shifted into the instruction register and a set of mandatory and optional instructions are defined by the IEEE 1149.1 standard. Furthermore design-specific instructions may be added when the component is designed.

The Boundary-scan Architecture contains at a minimum two test data registers: the Bypass Register and the Boundary-scan Register. The advantage of the mandatory bypass register, implemented as a single stage shift-register, is to shorten the serial path for shifting test data from the component's TDI to its TDO [Ble93]. The Boundary-scan register of a component consists of series of Boundary-scan cells arranged to form a scan path around the core, see Figure 3.9. [Ble93].

#### INTRODUCTION AND RELATED WORK

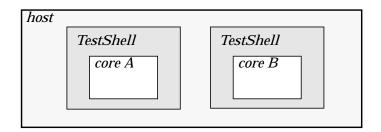

Figure 3.10: Three hierachy layers: core, Test-Shell and host.

## 3.3.2 THE TESTSHELL AND P1500 APPROACH

The TestShell is an approach to reducing the test access and test isolation problem for system-on-chip designs proposed by Marinissen *et al.* [Mar98]. Since a component to be used in a PCB is tested before mounting, while in SOC a core is to be tested after the complete chip is manufactured, a test access and test isolation method for SOC, in addition to support the test applicable by Boundary-scan, must efficiently solve the problem of testing the core themselves. It would be possible to perform component testing using Boundary-scan and the technique can be transferred to SOC. However, due to the serial access used in Boundary-scan it would lead to an excessively long test time for systems with numerous cores.

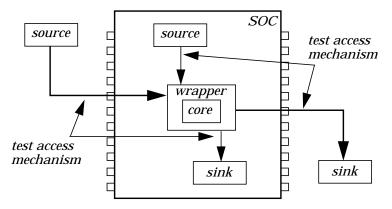

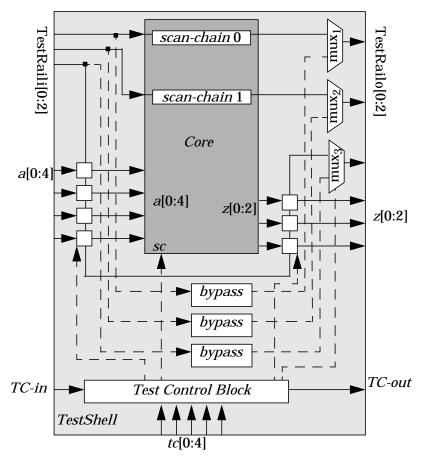

The TestShell approach consists of three layers of hierarchy, see Figure 3.10, namely:

- the *core* or the *IP module*,

- the *TestShell*, and

- the *host*.

The *core* or the *IP module* is the object to be tested and it is designed to include some DFT mechanism. No particular DFT technique is assumed by the TestShell. The *host* is the environment where the core is embedded. It can be a complete IC, or a

Figure 3.11: Host-TestShell interface.

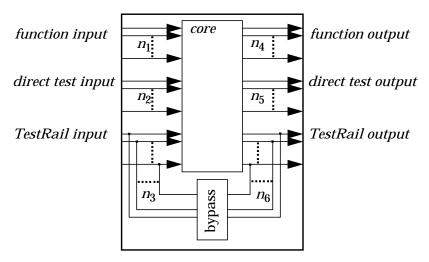

design module which will be an IP module itself. Finally, the *TestShell* is the interface between the core and the host and it contains three types of input/output terminals, see Figure 3.11:

- *Function* input/output corresponds one-to-one to the normal inputs and outputs of the core.

- *TestRail* input/outputs are the test access mechanism for the TestShell with variable width and an optional bypass.

- *Direct* test input/outputs are used for signals which can not be provided through the TestRail due to their non-synchronous or non-digital nature.

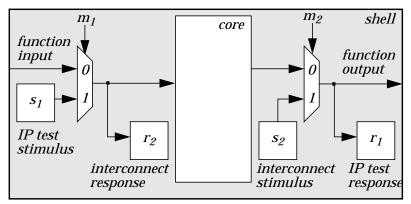

The conceptual view of a TestCell is illustrated in Figure 3.12 and it has four mandatory modes:

- *Function* mode, where the TestShell is transparent and the core is in normal mode, *i.e.* not tested. It is achieved by setting the multiplexers  $m_1=0$  and  $m_2=0$ .

- *IP Test* mode, where the core within a TestShell is tested. In this case the multiplexers should be set as:  $m_1=1$  and  $m_2=0$

Figure 3.12: Conceptual view of the Test Cell.

where test stimulus comes from  $s_1$  and test response is captured in  $r_1$ .

- *Interconnect Test* mode, where the interconnections between cores are tested. The multiplexers are set to  $m_1=0$  and  $m_2=1$  where  $r_2$  captures the response from a function input and  $s_2$  holds the test stimulus for a function output.

- *Bypass* mode, where test data is transported through the core regardless if the core has transparent modes. It may be used when several cores are connected serially into one TestRail, to shorten an access path to the core-under-test, see Bypass using Boundary-scan in Section 3.3.1. It is not shown in Figure 3.12. The bypass is implemented as a clocked register.

Figure 3.13 illustrates the TestShell approach where a Test Cell is attached to each functional core terminal (primary input and primary output).

# TestRail

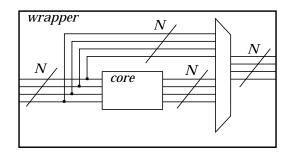

Every TestShell has a TestRail which is the test data transport mechanism used to transport test patterns and responses for synchronous digital tests.

Figure 3.13: The TestShell approach.

The width n ( $n \ge 0$ ) of the TestRail is a trade-off between the following parameters:

- *Host pins* available for test form an important limiting factor with respect to the maximal TestRail width.

- *Test time* is dependent on the test data bandwidth.

- *Silicon area* required for wiring the TestRail increases with the width of the TestRail.

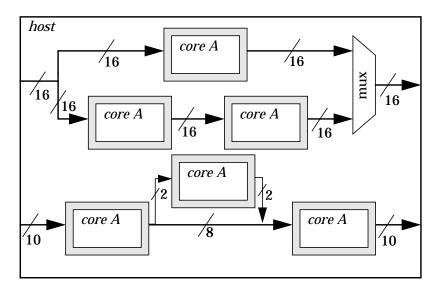

Figure 3.14: Example of possible host-level TestRail connections.

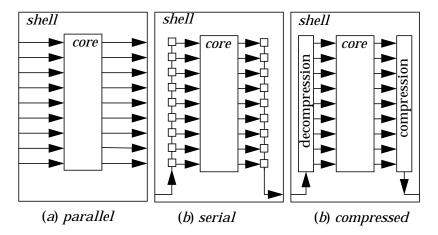

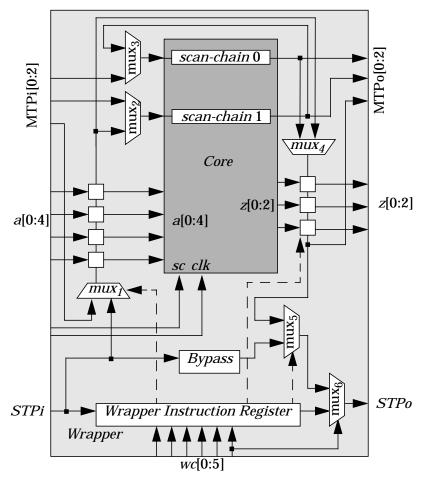

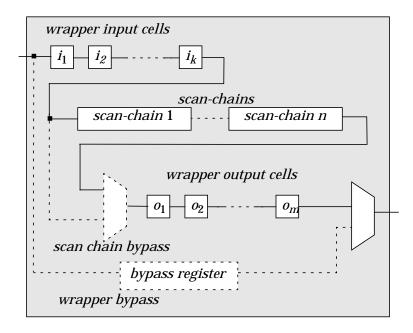

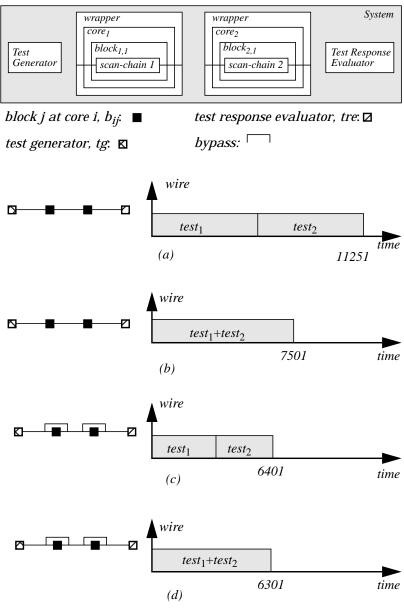

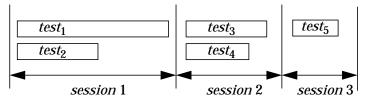

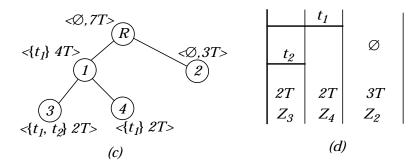

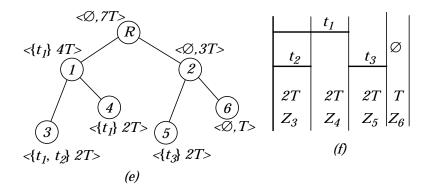

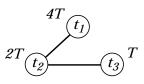

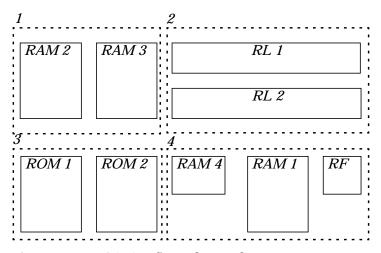

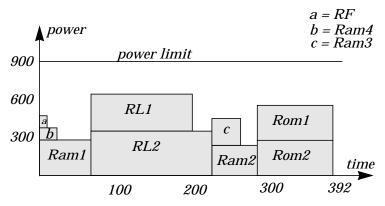

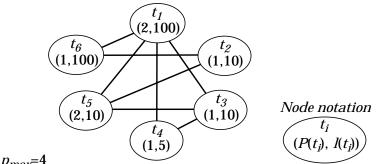

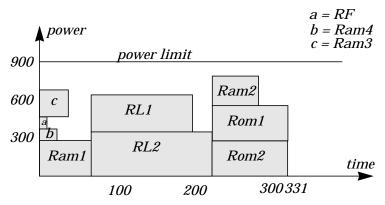

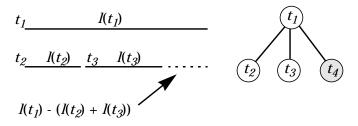

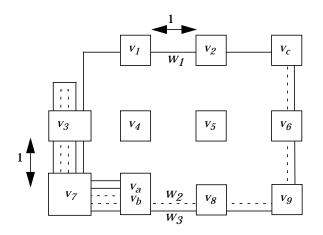

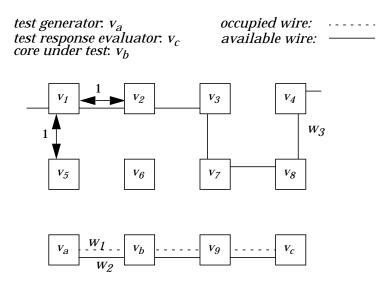

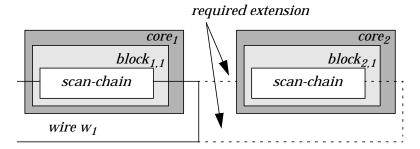

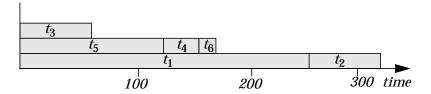

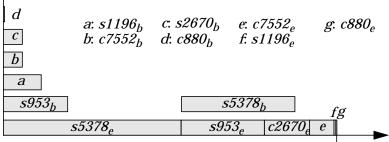

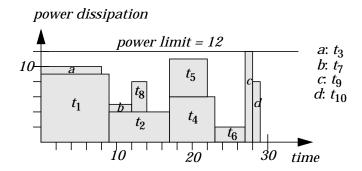

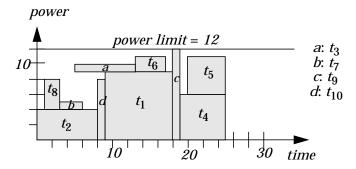

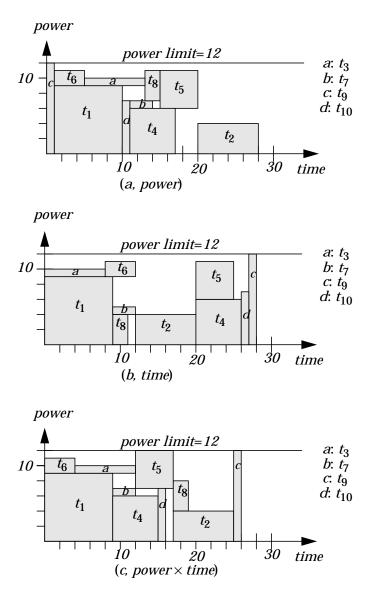

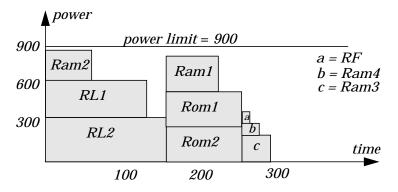

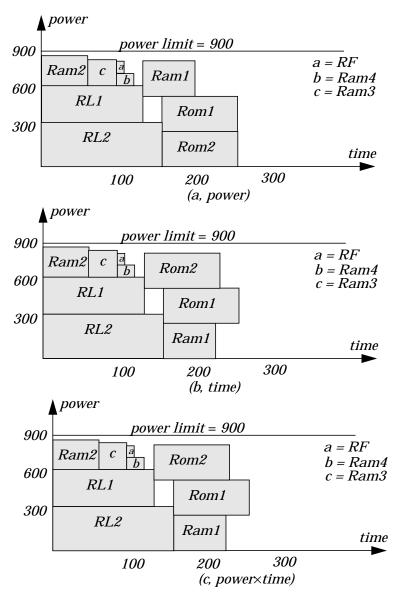

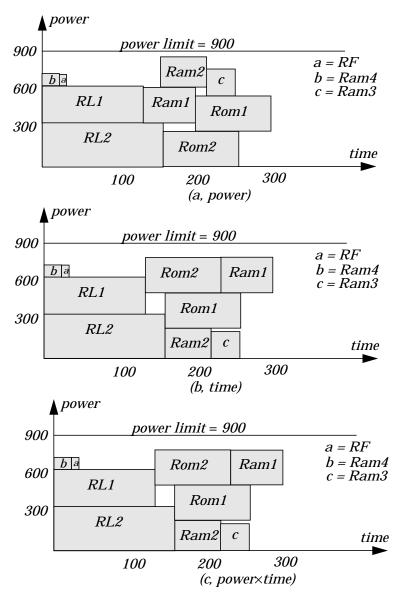

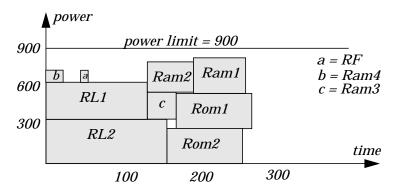

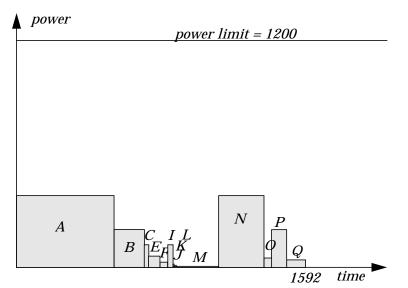

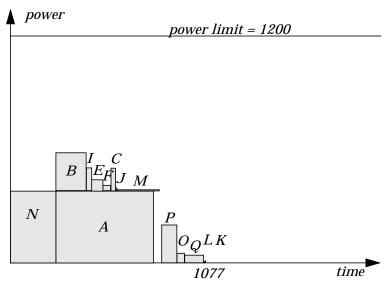

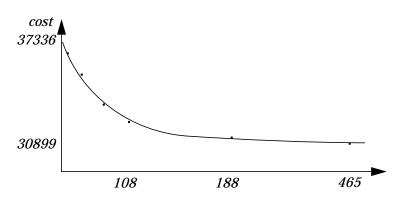

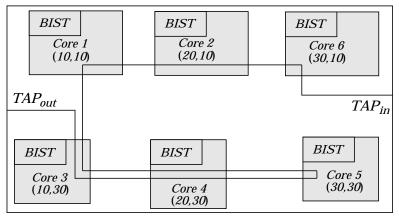

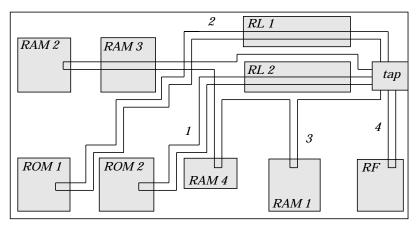

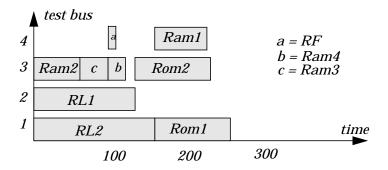

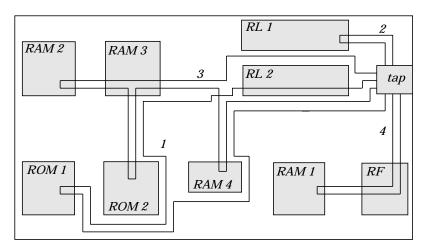

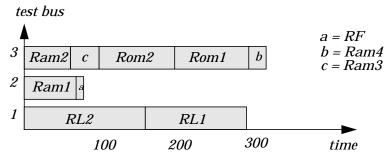

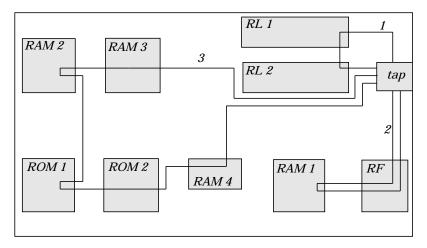

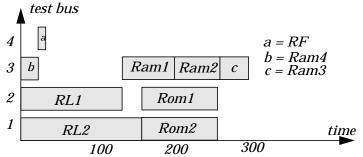

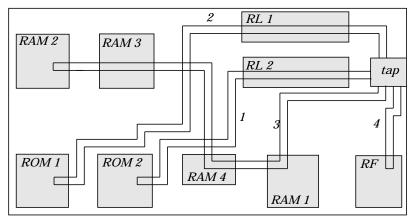

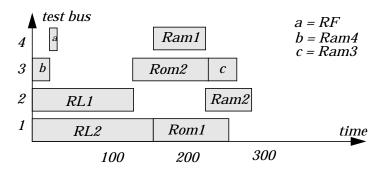

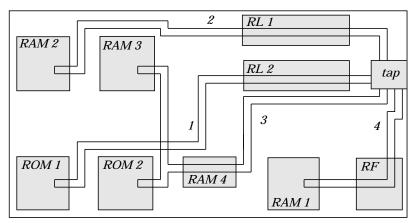

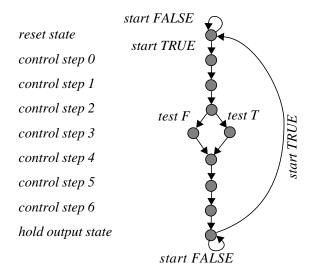

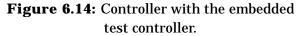

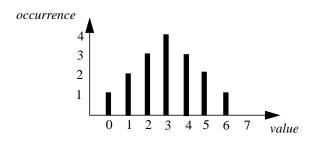

The TestRail is designed to allow flexibility; see Figure 3.14, where an example is shown to illustrate some possible connections. Within the TestShell the connections may vary. The three basic forms of connection are as follows, see Figure 3.15: