# Iterative Schedule Optimisation for Voltage Scalable Distributed Embedded Systems

MARCUS T. SCHMITZ and BASHIR M. AL-HASHIMI University of Southampton and PETRU ELES Linköping University

We present an iterative schedule optimisation for multi-rate system specifications, mapped onto heterogeneous distributed architectures containing dynamic voltage scalable processing elements (DVS-PEs). To achieve a high degree of energy reduction, we formulate a generalised DVS problem, taking into account the power variations among the executing tasks. An efficient heuristic is presented that identifies optimised supply voltages by not only "simply" exploiting slack time, but under the additional consideration of the power profiles. Thereby, this algorithm minimises the energy dissipation of heterogeneous architectures, including power managed processing elements, effectively. Further, we address the simultaneous schedule optimisation towards timing behaviour and DVS utilisation by integrating the proposed DVS heuristic into a genetic list scheduling approach. We investigate and analyse the possible energy reduction at both steps of the co-synthesis (voltage scaling and scheduling), including the power variations effects. Extensive experiments indicate that the presented work produces solutions with high quality.

Categories and Subject Descriptors: C.3 [Special-purpose and application-based systems]: Real-time and embedded systems; J.6 [Computer-aided engineering]: Computer-aided design

General Terms: Algorithms, Design, Optimization

Additional Key Words and Phrases: Dynamic voltage scaling, Embedded systems, Energy minimisation, Scheduling, System synthesis, Heterogeneous distributed systems

#### 1. INTRODUCTION AND RELATED WORK

The dramatically growing market segment for embedded computing systems is driven by the ever increasing demand for new application specific devices, which can be generally found in almost every application domain, such as consumer electronics, home appliances, automotive, and avionic devices. To help balancing the production costs with development time and cost, these embedded systems are commonly composed of several heterogeneous processing elements (PEs), which are interconnected by communication links (CLs) [Wolf 1994]. For example, very

Authors' addresses: M. T. Schmitz and B. M. Hashimi, Department of Electronics and Computer Science, University of Southampton, SO17 1BJ Southampton, UK, email: {ms99r, bmah}@ecs.soton.ac.uk; P. Eles, Department of Computer and Information Science, Linköping University, S-581 83 Linköping, Sweden, email: petel@ida.liu.se.

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

© 2003 ACM 0000-0000/2003/0000-0001 \$5.00

often the combination of less powerful and cheap PEs leads to a more cost efficient design implementation than the usage of a powerful single processor system. Typically, such embedded systems have to concurrently perform a multitude of complex tasks under a strict timing behaviour, given in the system specification.

System-level co-design is a methodology aiming to aid the system designers at solving the difficult problem of finding the "best" suitable implementation for a system specification. The traditional co-design flow for distributed systems involves solving three subproblems, namely:

- (1) Allocation: determining the numbers and types of PEs and CLs used to compose the system architecture,

- (2) Mapping: assignment of computational tasks to PEs and of data transfers between different PEs to CLs,

- (3) Scheduling: determining the execution order (sequencing) of tasks mapped to a PE and communications mapped to a CL.

These problems (allocation/mapping and scheduling) are well-known to be NPcomplete [Garey and Johnson 1979], and therefore an optimal co-design of distributed systems is intractable. This justifies the usage of heuristic optimisation algorithms of different types, e.g., simulated annealing [Henkel et al. 1993; Eles et al. 1997], tabu-search [Eles et al. 1997], genetic algorithm [Dick and Jha 1998; Teich et al. 1997, or constructive techniques [Wolf 1997], to tackle the computational complexity.

In the last decade power dissipation has become a mandatory issue of concern in the design of embedded systems because of: (a) The popularity of mobile applications powered by batteries with limited capacity, (b) the operational costs and environmental reasons affected by the high electrical power consumption of large computing systems, and (c) the reliability and feasibility problems caused by extensive heat production exceeding the physical substrate limitations, especially when implementing systems on a single chip (SoCs). Several useful techniques have been proposed to reduce the power dissipation of integrated circuits, targeted at different levels of abstraction [Devadas and Malik 1995; Pedram 1996]. One approach aiming to reduce the power dissipation at the system-level is recently receiving a lot of attention from the research community and industry, namely, dynamic voltage scaling (DVS) [Weiser et al. 1994; Gutnik and Chandrakasan 1997; Hong et al. 1999; Ishihara and Yasuura 1998; Okuma et al. 1999; Quan and Hu 2001; Shin and Choi 1999; Shin et al. 2000; Simunic et al. 2001]. The main idea behind DVS is to conjointly scale the supply voltage  $V_{dd}$  and operational frequency f dynamically during run-time in accordance to the temporal performance requirements of the application. In this way the dynamic power dissipation  $P_{dyn}$  (disregarding shortcircuit power) is reduced in a near cubic manner, since it depends quadratically on the supply voltage and linearly on the operational frequence. The exact relation is expressed by the following two equations,

$$P_{dyn} = C_L \cdot N_{0 \to 1} \cdot f \cdot V_{dd}^2 \tag{1}$$

$$f = k \cdot \frac{(V_{dd} - V_t)^2}{V_{dd}} \tag{2}$$

where  $C_L$  denotes the load capacitance of the digital circuit,  $N_{0\rightarrow 1}$  represents the zero to one switching activity, k is a circuit dependent constant, and  $V_t$  is the threshold voltage. DVS is thereby able to exploit the idle and slack times (time intervals where system components do not carry out any computations), given in the system schedule, in order to lower the power dissipation. The occurrence of idle and slack times has three reasons: (a) It is often the case for a given application to show various degrees of parallelism, i.e., not all PEs will be utilised constantly during run-time, (b) the performance of the allocated architecture cannot be adapted perfectly to the application needs, since the allocation of "performance" is not given as continuous range, but is rather quantised, and (c) schedules for hard realtime systems are constructed by considering worst case execution times (WCETs), however, actual execution times of tasks during operation are, for most of their activations, smaller than their WCETs. Several state-of-the-art implementations of DVS enabled processors [Burd et al. 2000; Gutnik and Chandrakasan 1997; Klaiber 2000 have successfully shown that power consumption can be reduced significantly (by up to 10 times compared to fixed voltage approaches) when running real world applications. In order to achieve such a high level of power and energy efficiency, it is essential to identify optimised scaling voltages for the task executions [Okuma et al. 2001 to exploit the available idle and slack times efficiently. Such voltage scheduling algorithms can be divided in two broad categories: on-line (dynamic) [Lee and Sakurai 2000; Quan and Hu 2001; Shin and Choi 1999] and off-line (static) approaches [Bambha et al. 2001; Gruian and Kuchcinski 2001; Ishihara and Yasuura 1998. The first class dynamically re-calculates the priorities and scaling voltages of tasks at run-time, i.e., the voltage schedule is changed during the execution of the application. Obviously, such approaches consume additional power and time during execution. On the other hand, they are able to make use of the dynamic slack introduced by execution times smaller than the WCET. In the second class, a static voltage schedule is calculated once before the application is executed, i.e., the voltage schedule is maintained unchanged during run-time. Hence, power and time overheads are avoided. The technique proposed in this paper falls into the class of static voltage schedulers.

Voltage selection is already a complex problem when only single DVS processor systems, executing *independent* tasks, are considered [Hong et al. 1999]. The problem is further complicated in the presence of distributed systems specified by *dependent* tasks where the allocation, mapping, and scheduling influence the possibility to exploit DVS [Bambha et al. 2001; Gruian 2000; Luo and Jha 2000; Schmitz and Al-Hashimi 2001]. Most previous DVS approaches [Hong et al. 1999; Lee and Sakurai 2000; Quan and Hu 2001; 2002; Shin and Choi 1999] concentrate on single processor systems executing *independent* task sets and, hence, are not directly applicable to the problem addressed here. Nevertheless, we need to consider DVS at all these optimisation steps during co-synthesis, in order to find high quality system implementations. In this paper, we will concentrate on the scheduling and voltage scaling aspects of such systems. Further details concerning the mapping and allocation steps can be found in [Schmitz et al. 2002; Schmitz 2003].

Previous research in system-level co-synthesis is extensive but has mainly focused on traditional architectures *excluding* issues related to power consumption [Ernst

et al. 1993; Henkel and Ernst 2001; Micheli and Gupta 1997; Prakash and Parker 1992; Wolf 1997; Xie and Wolf 2001] or considering energy optimisation with components that are *not* DVS enabled [Dick and Jha 1998; Kirovski and Potkonjak 1997]. A system-level scheduling technique for power-aware systems in mission-critical applications was presented in [Liu et al. 2001]. This approach satisfies min/max timing constraints as well as max power constraints taking into account not only processor power consumption but additionally the power dissipated by peripheral system components. All this research provides a valuable basis for the work presented here. However, three research groups recently proposed approaches for the voltage scaling problem in distributed systems that have close relationship to the problems we address in this paper. Bambha [Bambha et al. 2001] presented a hybrid search strategy based on simulated heating. This method uses a global genetic algorithm to find appropriate parameter settings for a local search algorithm. The local search algorithms are based on hill climbing and Monte Carlo techniques.

In [Luo and Jha 2000], a power conscious joint scheduling of aperiodic and periodic tasks is introduced, which reserves execution slots for aperiodically arriving tasks within a static schedule of a task graph. Their algorithm aims for energy minimisation through DVS by distributing the available deadline slack evenly among all tasks. They further extend their approach towards a battery-aware scheduling with the aim to improve the battery discharge profile [Luo and Jha 2001]. Gruian and Kuchcinski [Gruian and Kuchcinski 2001] extend a dynamic list based scheduling heuristic to support DVS by making the priority function energy aware. In each scheduling step the energy sensitive task priorities are re-calculated. If a scheduling attempt fails (exceeded hard deadline), the priority function is adjusted and the application is re-scheduled. Despite their power reduction efficiency, all these DVS approaches [Bambha et al. 2001; Gruian and Kuchcinski 2001; Luo and Jha 2000 do not consider and target heterogenous distributed architectures containing power managed DVS-PEs in which the dissipated power for each task execution might vary. It was shown in [Ishihara and Yasuura 1998] and [Manzak and Chakrabarti 2000 that the variations in the average switching activity (equivalent to variations in power) influence the optimal voltage schedule and hence need to be considered during the voltage selection. However, both approaches do not target distributed systems with multiple PEs executing tasks with dependencies. Thus, new system-level co-synthesis approaches for DVS-enabled architectures, which take into account that power varies among the executed tasks, are needed. Recently, an approach to solve this problem has been presented in [Zhang et al. 2002]. The scheduling optimisation towards DVS utilisation in this approach is based on a constructive technique, as opposed to our iterative scheduling optimisation which allows a thorough search to find schedules of high quality.

In this paper, we formulate a generalised DVS problem that considers power variation effects and is based on an iterative scheduling optimisation. We assume that typical embedded architecture employ gate level power reduction techniques, such as gated clocks, to switch off un-utilised blocks in the circuit [Devadas and Malik 1995; Tiwari et al. 1994]. It is therefore necessary to take into account that power varies considerably among the tasks carried out by the system. This holds also for DVS-PEs [Burd 2001]. For example, in the case of a general purpose

processor (GPP) including an integer and a floating point unit, it is not desirable to keep the floating point unit active if only integer instructions are executed. Thereby, different tasks (different use of instructions) dissipate different amounts of power on the same PE. In the case of an ARM7TDMI processor the current varies between 5.7 and 18.3mA, depending on the functionality which is carried out [Brandolese et al. 2000]. Taking this into account, the assumptions to Lemma 1 and Lemma 2 in [Ishihara and Yasuura 1998], stating that energy consumption is independent from the type of operations and input data and depends only on the supply voltage, have to be rejected. In addition to this, our problem formulation also takes into consideration the different power dissipations among different processing elements. This is important since high power consuming PEs are likely to have a greater impact on the energy saving (when scaled to lower performance) than low power consuming PEs.

The aim of this paper is twofold: Firstly, we are formulating and examining a generalised DVS problem which allows power variations, in the following also called PV-DVS problem. We introduce a new, generalised DVS heuristic for distributed systems containing heterogenous and power managed PEs. Secondly, we illustrate the incorporation of this scaling technique into a genetic list scheduling approach, which optimises the system schedule simultaneously towards timing feasibility and DVS exploitability. This incorporation necessitates a careful adaption of the employed list scheduler to ensure its suitability for both optimisation goals. We provide a detailed analysis of the DVS and scheduling approach revealing how scheduling influences the DVS utilisation. This analysis is carried out on several benchmark examples from literature [Bambha et al. 2001; Gruian and Kuchcinski 2001] and generated for experimental purposes, as well as on an optical flow detection real-life examples.

The remainder of the paper is organised in the following way. In Section 2, we formulate the system-level synthesis problem and give a general and brief overview of genetic algorithms, since they are used for the schedule optimisation. Section 3 describes in detail our approach to the system-level scheduling problem for architectures including DVS components. In Section 4 numerous benchmark examples are evaluated and compared with approaches that neglect power profile information. Finally, in Section 5 we give some conclusions drawn from the presented work.

#### 2. PROBLEM FORMULATION AND PRELIMINARIES

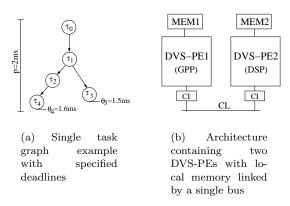

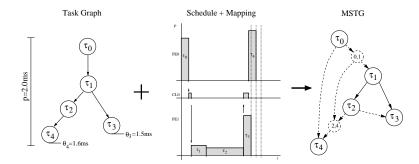

In this work, we consider that a multi-rate application is specified as a set of communicating tasks, represented by a task graph  $G_S(\mathcal{T},\mathcal{C})$ . This (hyper) task graph might be the combination of several smaller task graphs, capturing all task activations for the hyper-period (LCM of all graph periods). Figure 1(a) shows a task graph example. Each node  $\tau \in \mathcal{T}$  in these acyclic directed graphs represents a task, an atomic unit of functionality to be executed without preemption. Further, each task might inherit a specific hard deadline  $\theta$ . These deadlines must be met to fulfil the feasibility requirements of the specified application. In addition, the task graph inherits a period p which specifies the maximal allowed time between two successive invocations of the initial task. The edges  $\gamma \in \mathcal{C}$ , in the task graph, denote precedence constraints and data dependencies between tasks. If two tasks,

6

Fig. 1. Specification and Architectural Models

$\tau_i$  and  $\tau_j$ , are connected by an edge then the execution of task  $\tau_i$  must be finished before task  $\tau_j$  can be started. Data dependencies inherit a data value, reflecting the quantity of information to be exchanged by two tasks. A feasible implementation of an application must respect all timing constraints and precedence requirements when executed on an underlying architecture. This type of specification model is most suitable for data flow intensive application with a repetitive behaviour, as they can be found in systems for image, speech, and video processing.

The architectures we consider here consist of heterogeneous PEs, like general purpose processors (GPPs), ASIPs, FPGAs, and ASICs. These components include state-of-the-art DVS-PEs. An infrastructure of communication links, like buses and point-to-point connections, interconnects these PEs. Processors are capable to execute software tasks, which are accommodated in local memory, in a sequential manner, while tasks implemented on FPGAs or ASICs can be performed in parallel and occupy silicon area. Figure 1(b) shows an example architecture built out of two DVS-PEs connected by a single bus. Such architectures can be found in application domains which target multimedia and telecommunication systems. The architecture is captured using a directed graph  $G_A(\mathcal{P}, \mathcal{L})$  where nodes  $\pi \in \mathcal{P}$  represent processing elements and edges  $\lambda \in \mathcal{L}$  denote communication links.

Each task of the system specification might have multiple implementation alternatives and can therefore be potentially mapped to several PEs able to execute this task. If two communicating tasks are accommodated on different PEs,  $\pi_n$  and  $\pi_m$  with  $n \neq m$ , then the communication takes place over a CL, involving a communication time overhead. For each possible task mapping certain implementation properties, like e.g. execution time, dynamic power dissipation, memory, and area requirements, are given in a technology library. These values are either based on previous design experience or on estimation and measurement techniques [Brandolese et al. 2000; Fornaciari et al. 1999; Li et al. 1995; Tiwari et al. 1994; Muresan and Gebotys 2001]. The technology library further includes information about the available PEs and CLs, such as price, DVS enable flag, etc.

The overall co-synthesis process includes three traditional co-design problems, namely, *allocation*, *mapping*, and *scheduling*. These optimisation steps determine ACM Journal Name, Vol. V, No. N, May 2003.

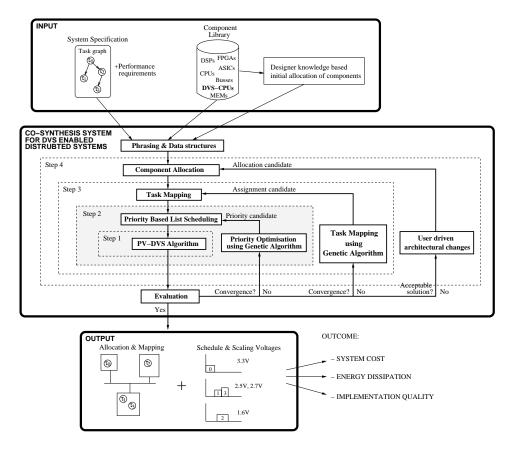

Fig. 2. Design flow of our generalised PV-DVS co-synthesis methodology for heterogeneous and power managed processing elements

an architecture, a possible mapping of the functionality over the components of that architecture, and a feasible schedule, such that certain design objectives are either minimised or maximised. However, the problem, as presented here, involves an additional *voltage scaling* step, which identifies scaling voltages for the tasks mapped to DVS-PEs, in order to minimise the energy dissipation. Obviously, due to their interrelations these design decisions cannot be made independently of each other. In this paper, we will particularly focus on the scheduling and voltage scaling problem in such DVS enabled architectures.

#### 3. SYSTEM SYNTHESIS APPROACH INCLUDING POWER MANAGED PES

In this section, we give an overview of the co-synthesis flow for distributed architectures containing heterogeneous, power managed processing elements. The presented approach is based on a generalised power model, which allows to capture power variation effects among the tasks (the power profiles). The whole design flow is illustrated in Figure 2. As mentioned earlier, this paper concentrates on the DVS algorithm and the scheduling technique, indicated as Steps 1 and 2. However, we give a brief overview of our system-level synthesis approach. The input

information consists of two main parts, a system specification and a component library. The system specification is captured using the directed acyclic graph, as outlined in Section 2, and includes the performance requirements. The properties of processing elements and communication links (price, idle power dissipation, etc.) are collected in the component library, which additionally includes estimated information (i.e. execution time, dynamic power dissipation, etc.) about each task/PE and communication/CL combination. The input to our co-design approach further involves a knowledge-based pre-allocation of system components. Using the presented synthesis approach the designer evaluates the suitability of this allocation. If an architecture proves to be unsuitable or of low quality the designer modifies the allocation and re-evaluates the design. The presented co-synthesis system takes this input information and establishes the necessary data structures. This is followed by the allocation step (Step 4 in Figure 2) that determines the type and quantity of PEs and CLs used to compose the architecture. An appropriate allocation minimises system cost while providing sufficient computational performance. In Step 3, the task mapping is carried out. This step determines the mapping of tasks to PEs and uses a GA-based iterative improvement technique. Task mapping optimises the distribution of tasks towards energy savings, but additionally aims to satisfy imposed area constraints on hardware components. After a mapping is established, the next step involves the scheduling (Step 2) of the tasks and communications in order to meet the hard time constraints of the application and to further minimise the energy dissipation in the presence of DVS-PEs. This optimisation is based on a list scheduling heuristic using a GA for the determination of priorities. At the core of this co-synthesis approach, as shown in Figure 2, is the PV-DVS algorithm (Step 1). In this step the algorithm identifies scaling voltages for the task executions on DVS-PEs under the consideration of power variations in order to efficiently reduce the energy dissipation of the distributed system. The output of the proposed codesign flow consists of three results: (a) an allocated architecture, (b) a mapping of tasks and communications onto that architecture, and (c) a feasible schedule for the task executions and the communication activities, such that no time constraints are violated. In addition to these traditional aspects, the proposed technique further outputs scaling voltages for the tasks executed by DVS-PEs. Note that the architecture, the mapping, and the schedule are optimised for the exploitation of DVS and therefore differ from the results obtained by traditional co-design approaches [Dick and Jha 1998; Ernst et al. 1993; Kirovski and Potkonjak 1997; Micheli and Gupta 1997; Prakash and Parker 1992; Wolf 1997]. The outcome, which is of relevance to the designer/architect, consists of the system cost (system price), the total system energy dissipation, and the implementation quality (e.g. performance related to soft deadlines). Using these values, the designer is able to judge the overall quality of the implementation and can operate certain changes if necessary.

# 3.1 Generalised DVS Approach for Distributed Systems containing Power Managed PEs

In this section, which is concerned with the identification of scaling voltages, we first motivate the consideration of power variation effects using an illustrative example. This is followed (Subsection 3.1.1) by the formulation of a generalised DVS problem for distributed systems. In Subsection 3.1.2, we introduce an heuristic algorithm

to solve the formulated problem.

The aim of the generalised DVS approach is to identify scaling voltages under the consideration of power variation effect. This is done for the scheduled and mapped system specification such that the total dynamic energy dissipation is minimised. The presented approach assumes that no restrictions are placed on the scaling voltages, i.e., our technique targets variable-voltage systems (nearly continuous range of possible supply voltages) rather than multi-voltage systems (small and limited number of potential supply voltages). However, we will explain in Section 3.1.2 how the obtained scaling voltages can be easily adapted to suit multi-voltage systems. The term *generalised DVS* refers to the key observation that the power dissipation varies considerably upon the PE types and the instructions executed by the PEs. This is not new and well known [Burd and Brodersen 1996; Tiwari et al. 1994]. However, unlike previous approach to DVS for distributed systems [Bambha et al. 2001; Gruian and Kuchcinski 2001; Luo and Jha 2000, the presented technique takes these power variation effects into account and is sufficiently fast to be used in the inner optimisation loop of a co-synthesis tool. The following example is used to motivate the necessity of considering power variations during the voltage selection, in order to minimise the dynamic energy dissipated by the system. Before we start with the example, it is necessary to define the term energy difference, which will be used throughout this section.

Definition 1. We define an energy difference  $\Delta E_{\tau}$  as the difference between the energy dissipation of task  $\tau$  with the execution time t and the reduced energy dissipation (due to voltage and clock scaling) of the same task when extended by a time quantum  $\Delta t$ . Formally:

$$\Delta E_{\tau} = E_{\tau}(t) - E_{\tau}(t + \Delta t) \tag{3}$$

where

$$E_{\tau}(t)$$

and  $E_{\tau}(t + \Delta t)$  are calculated using Equations (1) and (2).

# Motivational Example 1: Considering Power Variations during Voltage Scaling

The intention with this illustrative example is to motivate the consideration of power variation effects during the voltage scaling of heterogeneous distributed systems. This is done by using two different models during the voltage scaling: (a) a fixed power model which does not allow power variations and (b) a variable power model which takes power variation into account (as used in the proposed approach).

The starting point for the DVS technique is a system specification scheduled (at nominal voltage) and mapped onto an allocated architecture which includes power managed DVS components. In this simple example, we consider an architecture composed of two hypothetical, heterogeneous DVS-PEs connected through a single bus as illustrated in Figure 1(b). The system is specified by the task graph shown in Figure 1(a).

Nominal supply voltage  $V_{max}$  and threshold voltage  $V_t$  for the two PEs are given in Table II(a). This table further shows the nominal execution times and dynamic power dissipations of tasks, according to their mapping. Furthermore, the transfer times and power dissipations of the communication activities are shown in Table II(b), reflecting the inter PE communications through the bus. Communications between tasks on the same PE are assumed to be instantaneous, and their

|                    | $\mathbf{PE0}$ $(V_{max})$ | $v_t = 5V, V_t = 1.2V$ | <b>PE1</b> $(V_{max} = 3.3V, V_t = 0.8V)$ |            |  |  |

|--------------------|----------------------------|------------------------|-------------------------------------------|------------|--|--|

| task               | exe. time                  | power dis.             | exe. time                                 | power dis. |  |  |

|                    | (ms)                       | (mW)                   | (ms)                                      | (mW)       |  |  |

| $\overline{	au_0}$ | 0.15                       | 85                     | 0.70                                      | 30         |  |  |

| $\overline{	au_1}$ | 0.40                       | 90                     | 0.30                                      | 20         |  |  |

| $	au_2$            | 0.10                       | 75                     | 0.75                                      | 15         |  |  |

| $	au_3$            | 0.10                       | 50                     | 0.15                                      | 80         |  |  |

| $\tau_4$           | 0.15                       | 100                    | 0.20                                      | 60         |  |  |

Table I. Execution times and power dissipations for the motivational example

(a) Task execution times and power dissipations at nominal supply voltage

| comm.                     | $time (\mu s)$ | power $dis. (mW)$ |

|---------------------------|----------------|-------------------|

| $\gamma_{0\rightarrow 1}$ | 0.05           | 5                 |

| $\gamma_{1 	o 2}$         | 0.05           | 5                 |

| $\gamma_{1\rightarrow 3}$ | 0.15           | 5                 |

| $\gamma_{2\rightarrow4}$  | 0.10           | 5                 |

(b) Communication times and power dissipations of communication activities mapped to the bus

power dissipation is neglected, as in most co-synthesis approaches.

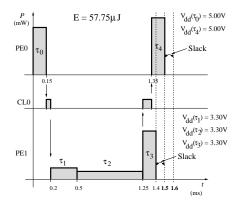

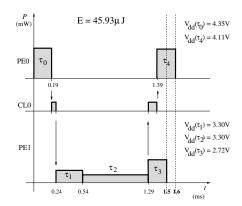

A possible mapping and scheduling of the system tasks onto the underlying architecture is shown in Figure 3, which describes the power dissipation over time, hence, the power profile of PEs and CLs. It can be observed that PE0 accommodates tasks  $\tau_0$  and  $\tau_4$ , while the remaining tasks are mapped to PE1. The communication link, connecting both PEs, shows two communications,  $\gamma_{0\to 1} = (\tau_0, \tau_1)$ and  $\gamma_{2\rightarrow 4}=(\tau_2,\tau_4)$ . The dynamic system energy dissipation of this configuration at nominal supply voltage can be calculated as  $57.75\mu J$ , using the dynamic power values and execution times given in Tables II(a) and II(b). Obviously, since the execution of task  $\tau_3$  finishes at 1.4ms and the task deadline is at 1.5ms, a slack of 0.1ms is available, as indicated in Figure 3. The same holds for task  $\tau_4$ , which finishes its execution after 1.5ms, leaving a slack of 0.1ms until the deadline is reached. These slacks can be used to extend the task execution times. Thus, the DVS-PEs can be slowed down by scaling the supply voltage and accordingly the clock frequency, following the relation given in Equation (2). Let us consider two cases for the identification of scaling voltages: (a) When a fixed power model is used (power variations are neglected), i.e., all tasks mapped to the same PE are assumed to consume the same constant amount of power, and (b) a more generalised and more realistic power model allowing for power variations among the tasks (as proposed in this work).

One approach to optimise the energy dissipation, which neglects the power pro-ACM Journal Name, Vol. V, No. N, May 2003.

Fig. 3. Power profile of a possible mapping and schedule at nominal supply voltage (no DVS is applied)

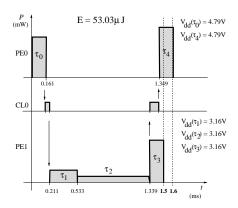

file, is to distribute the slack time evenly among the tasks. This is illustrated in Figure 4(a) where each task execution is extended using a factor of e = 1.45/1.35 = 1.074, since the total computation time (not including communications) accounts for 1.35ms and the available time (given the slack of 0.1ms) is 1.45ms. Thereby, the extended task executions can be calculated as the following:  $t_0 = 0.161ms$ ,  $t_1 = 0.322ms$ ,  $t_2 = 0.856ms$ ,  $t_3 = 0.161ms$ , and  $t_4 = 0.161ms$ . This allows to lower the supply voltages of PE0 and PE1 to 4.79V and 3.16V, respectively, according to following equation (derived from Equation (2)).

$$V_{dd} = V_t + \frac{V_0}{2d^*} + \sqrt{\left(V_t + \frac{V_0}{2d^*}\right)^2 - V_t^2}$$

(4)

where  $d^*$  denotes the normalised delay, which, in this example, is equal to the extension factor e. The constant  $V_0$  is given by:

$$V_0 = \frac{(V_{max} - V_t)^2}{V_{max}} \tag{5}$$

Thus, the reduced voltages of PE0 is calculated as:

$$V_{dd} = 1.2V + \frac{(5V - 1.2V)^2/5V}{2 \cdot 1.074} + \sqrt{\left(1.2V + \frac{(5V - 1.2V)^2/5V}{2 \cdot 1.074}\right)^2 - (1.2V)^2}$$

$$V_{dd} = 4.788V$$

using the nominal supply voltage  $V_{max} = 5V$  and the threshold voltage  $V_t = 1.2V$  as given in Table II(a). In the same way, the scaled supply voltage for PE1 can be calculated as  $V_{dd} = 3.161V$ , using  $V_{max} = 3.3V$  and  $V_t = 0.8V$ . Adjusting the supply voltages of the PEs to these levels, the task deadlines are still satisfied, and the power dissipations are reduced. According to Equation 1, the power dissipation of each task can be calculated using the following relation:

$$\frac{P_{V_{dd}}}{P_{V_{max}}} = \frac{\alpha \cdot C_L \cdot f_{V_{dd}} \cdot V_{dd}^2}{\alpha \cdot C_L \cdot f_{V_{max}} \cdot V_{max}^2} = \frac{1}{e} \cdot \frac{V_{dd}^2}{V_{max}^2} = \frac{1}{d^*} \cdot \frac{V_{dd}^2}{V_{max}^2}$$

(6)

- (a) DVS neglecting the power profile (traditional approach for voltage scaling of dependent tasks); reducing energy dissipation by 8.2%

- (b) DVS using a generalised power model (allowing for variations and the proposed energy difference approach; reducing energy dissipation by 20.5%%

Fig. 4. Power profiles of the schedules when DVS is applied, resulting in reduced energy dissipations

considering that  $\alpha \cdot C_L$  is constant for a given task and that relation between reduced operational frequency  $f_{V_{dd}}$  and maximal operational frequency  $f_{V_{max}}$  is equivalent to the inverse of the extension factor  $1/e = f_{V_{dd}}/f_{V_{max}}$ . Thereby, the power dissipations are reduced to  $P_0 = 72.57mW$ ,  $P_1 = 17.08mW$ ,  $P_2 = 12.81mW$ ,  $P_3 = 68.33mW$ , and  $P_4 = 85.38mW$ . This results in a total energy dissipation  $E = 53.03\mu J$ , a reduction of 8.2%.

Now consider the case when the generalised power model (allowing power variations) is employed during the identification of scaling voltages for the task executions. This optimisation is based on an energy difference as defined in Equation (3). For a simpler illustration of the method, the available deadline slack is divided into 10 time quanta with the size of 0.01ms each. Having defined the time quantum size  $\Delta t$ , we can now calculate an energy difference  $\Delta E_{\tau}$  for each task, using Equations (1), (2), and (3). For instance, the energy dissipation of task  $\tau_0$  at nominal supply voltage can be calculate as  $E_0(0.15) = 0.15ms \cdot 85mW = 12.75\mu J$ , using the values given in Table II(a). An extension of 0.01ms leads to an dissipated energy of  $E_0(0.16) = 0.16ms \cdot 73.69mW = 11.79\mu J$  and thereby results in an energy difference  $\Delta E_0 = 12.75 \mu J - 11.79 \mu J = 0.96 \mu J$ . In the same way, the energy differences can be calculated for the remaining task as  $\Delta E_1 = 0.234 \mu J$ ,  $\Delta E_2 = 0.156\mu J$ ,  $\Delta E_3 = 0.899\mu J$ , and  $\Delta E_4 = 1.130\mu J$ . Certainly, the task with the highest energy difference (task  $\tau_4$ ) will improve the energy dissipation by the highest amount when extended by  $\Delta t$ . Based on this observation, all remaining time quanta are iteratively distributed among the tasks and the energy difference of extended tasks are recalculated since the energy versus execution time function is non-linear (see Equations (1), (2) and (3)). This optimisation process is illustrated through Table II. Each line in this table corresponds to an iteration and shows

|           | Energy difference $\Delta E (\mu J)$ |         |         |         |         |  |  |

|-----------|--------------------------------------|---------|---------|---------|---------|--|--|

| iteration | $	au_0$                              | $	au_1$ | $	au_2$ | $	au_3$ | $	au_4$ |  |  |

| 1         | 0.960                                | 0.234   | 0.156   | 0.899   | 1.130   |  |  |

| 2         | 0.960                                | 0.234   | 0.156   | 0.899   | 0.965   |  |  |

| 3         | 0.960                                | 0.234   | 0.156   | 0.899   | 0.833   |  |  |

| 4         | 0.820                                | 0.234   | 0.156   | 0.899   | 0.833   |  |  |

| 5         | 0.820                                | 0.234   | 0.156   | 0.768   | 0.833   |  |  |

| 6         | 0.820                                | 0.234   | 0.156   | 0.768   | 0.725   |  |  |

| 7         | 0.708                                | 0.234   | 0.156   | 0.768   | 0.725   |  |  |

| 8         | 0.708                                | 0.234   | 0.156   | 0.663   | 0.725   |  |  |

| 9         | 0.708                                | 0.234   | 0.156   | 0.663   | 0.636   |  |  |

| 10        | 0.616                                | 0.234   | 0.156   | 0.663   | 0.636   |  |  |

| 11        | 0.616                                | 0.234   | 0.156   | 0.578   | 0.636   |  |  |

| 12        | 0.616                                | 0.234   | 0.156   | 0.578   | 0.562   |  |  |

| 13        | 0.541                                | 0.234   | 0.156   | 0.578   | 0.562   |  |  |

| 14        | 0.541                                | 0.234   | 0.156   | 0.507   | 0.562   |  |  |

| 15        | -                                    | -       | -       | 0.507   | -       |  |  |

| 16        | -                                    | -       | -       | 0.451   | -       |  |  |

| extension | 4                                    | 0       | 0       | 6       | 6       |  |  |

Table II. Energy differences during the execution of the PV-DVS algorithm

the extendable tasks and their potential energy gain. The bold numbers indicate which task is extended in each iteration, and in this simple example task  $\tau_4$  is the first task to be extended (iteration 1). Observing iteration 2, the energy difference of task  $\tau_4$  has changed to  $\Delta E_4 = 0.965 \mu J$ , however,  $\tau_4$  is still the task which will gain most from an extension. This iterative extension of tasks is repeated until no slack is left. The last row of Table II shows how many extensions are distributed to each task. Accordingly, the new execution times are as follows:  $t_0 = 0.19ms$ ,  $t_1 = 0.3ms$ ,  $t_2 = 0.75ms$ ,  $t_3 = 0.21ms$ , and  $t_4 = 0.21ms$ . These extended execution times allow to lower the supply voltages, which results in the following power dissipations:  $P_0 = 50.77mW$ ,  $P_1 = 20mW$ ,  $P_2 = 15mW$ ,  $P_3 = 38.74mW$ , and  $P_4 = 48.33mW$ . The total energy dissipation is  $E = 45.93\mu J$ . This means an energy reduction of 20.5% compared to a reduction of 8.2% obtained with a power profile neglecting approach.

3.1.1 Generalised DVS Problem Formulation. The DVS problem, including power variation effects, can be stated as follows:

Find for all DVS-PE mapped tasks  $\tau \in T_{\text{DVS}}$  of the system specification a single scaling voltage  $V_{dd}(\tau)$  (between the threshold voltage  $V_t$  and the nominal supply voltage  $V_{max}$ ) under consideration of individual power dissipations  $P_{max}(\tau)$  such that the dynamic energy dissipation  $E_{\Sigma}$  is minimised and no deadline and precedence constraints are violated.

The problem can be mathematically expressed using the following definitions, where  $\mathbb{R}_0^+ = \{x \mid x \in \mathbb{R}, \ 0 \le x < +\infty\}$  and  $\mathbb{R}^+ = \mathbb{R}_0^+ \setminus 0$ :

$-G_S(\mathcal{T},\mathcal{C})$  is the system specification graph, where  $\mathcal{T}$  is the set of tasks and  $\mathcal{C}$  is the set of communications, as defined in Section 2

- $-G_A(\mathcal{P},\mathcal{L})$  is a directed architecture graph, where  $\mathcal{P}$  is the set of PEs and  $\mathcal{L}$  is the set of CLs, as defined in Section 2

- $-\mathcal{P}_{DVS} \subseteq \mathcal{P}$  denotes the set of all DVS-enabled processing elements

- $-\mathcal{A} = \mathcal{T} \cup \mathcal{C}$  defines the set of all activities

- $-\mathcal{K} = \mathcal{P} \cup \mathcal{L}$  defines the set of all allocated components

- $-\mathcal{T}_{\text{DVS}} \subseteq \mathcal{T}$  denotes the set of all tasks mapped to DVS-PEs  $\mathcal{P}_{DVS}$

- $-P_{max}: \mathcal{T} \mapsto \mathbb{R}^+$  is a function returning the power dissipation of task  $\tau$  executed at maximal PE supply voltage  $V_{max}$

- $-t_{min}: \mathcal{T} \mapsto \mathbb{R}^+$  is a function returning the minimal execution time of task  $\tau \in \mathcal{T}$ at maximal PE supply voltage  $V_{max}$

- $-V_t: \mathcal{P} \mapsto \mathbb{R}^+$  is defined as a function which returns the threshold voltage of the PE to which task  $\tau \in \mathcal{T}$  is mapped

- $-V_{max}: \mathcal{T} \mapsto \mathbb{R}^+$  is a function returning the maximal supply voltage of the PE to which task  $\tau \in \mathcal{T}$  is mapped

- $-\mathcal{T}_d \subseteq \mathcal{T}$  denotes the set of all tasks having a hard deadline

- $-t_{exe}: \mathcal{A} \mapsto \mathbb{R}^+$  is a function defined by:

$$t_{exe} = \begin{cases} t_{min}(\epsilon) \cdot \frac{V_{dd}(\epsilon)}{(V_{dd}(\epsilon) - V_t(\epsilon))^2} \cdot \frac{(V_{max}(\epsilon) - V_t(\epsilon))^2}{V_{max}(\epsilon)} & \text{if } \epsilon \in \mathcal{T} \\ t_C & \text{if } \epsilon \in \mathcal{C} \end{cases}$$

where  $t_C$  is the communication time for the communication activity  $\gamma \in \mathcal{C}$

- $-t_d: \mathcal{T}_d \mapsto \mathbb{R}_0^+$  is a function returning the deadline of task  $\tau \in \mathcal{T}_d$

- $-\mathcal{C}^{in}: \mathcal{T} \mapsto 2^{\mathcal{C}}$  returns the set of all ingoing edges of task  $\tau \in \mathcal{T}$

- $-t_S: \mathcal{A} \mapsto \mathbb{R}_0^+$  is a function which returns the start time of an activity  $\epsilon \in \mathcal{A}$ (i.e., the time when the activity begins execution)

- $-A: \mathcal{K} \mapsto 2^A$  defines a function, returning the set of all activities mapped to a component  $\kappa \in \mathcal{K}$

- $-\mathcal{I} = [t_S(\epsilon), (t_S(\epsilon) + t_{exe}(\epsilon))]$  is the execution interval of activity  $\epsilon \in \mathcal{A}$

- $-i: \mathcal{A} \mapsto \mathbb{R}_0^+ \times \mathbb{R}_0^+$  is a function returning the execution interval of an activity

Using this definitions it is possible to formalise the problem mathematically as the minimisation of

$$E_{\Sigma} = \sum_{\tau \in T_{\text{DVS}}} P_{max}(\tau) \cdot t_{min}(\tau) \cdot \frac{V_{dd}^2(\tau)}{V_{max}^2(\tau)}$$

subject to

$$V_t(\tau) < V_{dd}(\tau) \le V_{max}(\tau), \ \forall \tau \in \mathcal{T}_{DVS}$$

$$t_S(\tau) + t_{exe}(\tau) \le t_d(\tau), \ \forall \tau \in \mathcal{T}_d$$

$$t_S(\gamma) + t_{exe}(\gamma) \le t_S(\tau), \ \forall \tau \in \mathcal{T}, \ \gamma \in \mathcal{C}^{in}(\tau)$$

$$i(\epsilon_n) \cap i(\epsilon_m) = \varnothing, \ \forall \ (\epsilon_n, \epsilon_m) \text{ so that } \epsilon_n \in A(\kappa_1), \epsilon_m \in A(\kappa_2) \Rightarrow \kappa_1 = \kappa_2$$

Please note that a single scaling voltage for each task executing on a DVS-PE has to be calculated for the statically scheduled application. However, in dynamically ACM Journal Name, Vol. V, No. N, May 2003.

```

Algorithm: PV_DVS_OPTIMISATION

Input: - task graph G_S(\mathcal{T}, \mathcal{C}), mapping, schedule, architectural information,

minimum extension time \Delta t_{min}

Output: - energy optimised voltages V_{dd}(\tau), dissipated dynamic energy E

01: Generate MSTG from G_S

02: \mathbb{Q}_E \leftarrow \emptyset

03: for all (\tau \in \mathcal{T}_d) \{\Delta t_d(\tau) := t_d(\tau) - (t_S(\tau) + t_{exe}(\tau))\}

04: for all (\tau \in \mathcal{T}) {calculate t_{\epsilon}}

05: for all (\tau \in \mathcal{T}) {if t_{\epsilon} \geq \Delta t_{min} then \mathbb{Q}_E := \mathbb{Q}_E + \tau}

06: \Delta t = \frac{\min t_{\epsilon}}{|\mathbb{Q}_{E}|}, if \Delta t < \Delta t_{min} then \Delta t = \Delta t_{min}

07: for all (\tau \in \mathbb{Q}_E) {calculate \Delta E(\tau)}

08: reorder \mathbb{Q}_E in decreasing order of \Delta E

09: while (\mathbb{Q}_E \neq \emptyset) {

10:

select first task \tau_{\Delta Emax} \in \mathbb{Q}_E

11:

t_{\tau_{\Delta E max}} := t_{\tau_{\Delta E max}} + \Delta t

update E_{\tau_{\Delta E max}} for all (\tau \in \mathcal{T}) {update t_S, t_E and t_{\epsilon}}

12:

13:

for all (\tau \in \mathbb{Q}_E) {if (t_{\epsilon}(\tau) < \Delta t_{min}) \lor (V_{dd}(\tau) \le V_t(\tau))

14:

then \mathbb{Q}_E := \mathbb{Q}_E - \tau

\Delta t = \frac{\min t_{\epsilon}}{|\mathbb{Q}_E|}, \text{ if } \Delta t < \Delta t_{min} \text{ then } \Delta t = \Delta t_{min}

15:

for all (\tau \in \mathbb{Q}_E) {update \Delta E(\tau)}

16:

reorder \mathbb{Q}_E in decreasing order of \Delta E

17:

18: }

19: delete MSTG

20: return E_{\Sigma}, and V_{dd}(\tau) for all (\tau \in \mathcal{T})

```

Fig. 5. Pseudo code of the proposed heuristic (PV-DVS) for the generalised DVS problem

scheduled systems the voltage of a single task might not be restricted to one voltage in order to dynamically adapted the system performance to the performance requirements.

3.1.2 Generalised DVS algorithm for heterogeneous distributed systems. Having formalised the problem, described the effects of power variations on the voltage selection and the necessity for their consideration in a generalised power model, we introduce next our DVS algorithm. The algorithm, summarised in Figure 5, is based on a constructive heuristic using the defined energy difference (Equation (3)). The starting point of the presented algorithm is a mapped and scheduled task graph (MSTG), i.e., it is known where and in which order the tasks are executed. Execution times and power dissipations are part of the architectural information, which also includes other necessary component properties, like the nominal supply voltage  $V_{max}$ , the threshold voltages  $V_t$ , etc. The minimal extension time  $\Delta t_{min}$  denotes the minimal time quantum to be distributed in each step of the algorithm. It is defined in order to speed up the determination of the voltage selection by preventing insignificant small extensions leading to trivial power reductions.

To allow for a fast and correct extension of task executions, which might influence other tasks and communications of the system, it is beneficial to capture the schedule and mapping information into the task graph (line 01 in Figure 5). This can be performed by generating a mapped and scheduled task graph, which is a transformed copy of the initial task graph, as shown in Figure 6. The transforma-

Fig. 6. Capturing the mapping and schedule information into the task graph by using pseudo edges and communication task

tion consists of two steps. Firstly, all communications (edges) that are mapped to communication links are replaced by the so called communication nodes and appropriate edges, thereby preserving the specified functionality. Secondly, all nodes mapped to a certain PE or CL are traversed in chronological order and linked by pseudo-edges [Chretienne et al. 1995], if an edge does not already exist. In this way, the scheduling and mapping are inherited into the task graph and the influence of a task extension can be easily propagated through the system schedule by traversing the MSTG in a breadth-first order to update the start and end times of the activities.

In order to identify all extendable tasks, the algorithm first calculates the available slack times of each hard deadline task (line 03). The algorithm then calculates the slack time  $t_{\epsilon}$  of all tasks, taken the interrelation between them into account (line 04). For this purpose an inverse breadth-first search algorithm is used to visit all nodes of the MSTG, in order to inherit the slack time of influenced tasks. If a visited task influences more than a single successor task then the smallest slack of the successor is inherited, in order to guarantee the satisfaction of deadlines. In line 05 the algorithm includes tasks with an available slack time  $t_{\epsilon}$  greater or equal than the minimal extension time  $\Delta t_{min}$  into the priority queue  $\mathbb{Q}_E$ . In this way tasks with negligible small or no extension possibility are excluded from the scaling process. The initial extension time  $\Delta t$  is calculated (line 06 of the algorithm) by dividing the smallest slack time among the extendable tasks, min  $t_{\epsilon}$ , by the number of extendable tasks  $|\mathbb{Q}_E|$ . This time, however, should not be smaller than the minimal extension time  $\Delta t_{min}$ . It is now possible to calculate the energy difference of all extendable tasks according to Equation (3), as shown in line 07. In line 08, the priority queue  $\mathbb{Q}_E$  is reordered in decreasing order of the energy differences.

The algorithm iterates the steps between line 09 and 18 until no extendable tasks are left in the priority queue. In each of these iterations the algorithm picks the first element from the priority queue, the task which leads to the highest energy reduction (line 10). This task is then extended by  $\Delta t$  and the energy dissipation value is updated (lines 11 and 12) according to Equations (1) and (2). In line 13 the extension is propagated through the MSTG, since successor tasks might have been affected by the extension in terms of start time  $t_S$ , end time  $t_E = t_s + t_{exe}$ , and available slack time  $t_{\epsilon}$ . In the next step (line 14) inextensible tasks are removed from

the extendable task queue  $\mathbb{Q}_E$ , if their available slack  $t_{\epsilon}$  is smaller than the minimal extension time  $\Delta t_{min}$ , or their scaled supply voltage  $V_{dd}$  is small or equal to the threshold voltage  $V_t$ . Taking into account the tasks in the new extendable queue, the time quantum  $\Delta t$  is recalculated (line 15) to enable a potential distribution of slack to all tasks in the queue. Based on this  $\Delta t$  value, the energy differences  $\Delta E$  are updated (line 16). The priority queue  $\mathbb{Q}_E$  is reordered according to the new energy differences (line 17). At this point, the algorithm either invokes a new iteration or ends, based on the state of the extendable task queue. If it terminates, the scaling voltages for each task execution and the total dynamic energy dissipation are returned (lines 19 and 20).

The algorithm, as described above, produces scaling voltages under the assumption that variable-voltage PEs are available that support continuous voltage scaling. However, it is possible to adapt the generated scaling voltages towards multi-voltage PEs, which are able to run at a restricted number of predefined voltages. It has been shown in [Ishihara and Yasuura 1998] that the two discrete supply voltages  $V_{d1}$  and  $V_{d2}$ ,  $V_{d1} < V_{dd} < V_{d2}$ , around the continuous selected voltage  $V_{dd}$  are the ones which minimise the energy dissipation, under the assumption that the time overhead for switching between different voltages can be neglected. Thus, our approach can be used for voltage selection on multi-voltage PEs. Given a task  $\tau$  with execution time  $t_{exe}$  at the continuous selected voltage  $V_{dd}$ , then, in order to achieve minimal energy consumption, the same task  $\tau$  will execute on the multiple voltage PE for  $t_{dis1}$  time units at the supply voltage  $V_{dis1}$  and for  $t_{dis2}$  time units at supply voltage  $V_{dis2}$ , where

$$t_{exe} = t_{dis1} + t_{dis2} \tag{7}$$

$$t_{dis1} = t_{exe} \cdot \frac{V_{dis1} \cdot (V_{dd} - V_t)^2}{(V_{dis1} - V_t)^2 \cdot V_{dd}} \cdot \frac{\frac{V_{dd}}{(V_{dd} - V_t)^2} - \frac{V_{dis2}}{(V_{dis2} - V_t)^2}}{\frac{V_{dis1}}{(V_{dis1} - V_t)^2} - \frac{V_{dis2}}{(V_{dis2} - V_t)^2}}.$$

(8)

Complexity Analysis. The complexity of the proposed PV-DVS algorithm can be calculated as follows: The WHILE loop (line 09) is executed in the worst case  $n \cdot m$ times, where n = |T| is the number of nodes in the graph, since all tasks might be extendable. However, depending on  $\Delta t_{min}$  and  $\Delta t$ , tasks might be extended more than once, and m, for the worst case, is the maximum number of such extensions. The inner part of the WHILE loop shows the following complexities: The propagation of extensions takes n+c in the worst case  $(c=|\mathcal{C}|)$  is the number of edges in the graph), since all nodes and edges might have to be visited by the breadth-first search (line 13). Removing inextensible tasks, again, might take n steps. Determination of the new extension time  $\Delta t$  is done in most n steps. And finally, updating the extendable queue takes n operations (the queue is implemented as Fibonacci heap). All other calculations inside the WHILE loop are executed in constant time. Therefore, the final time complexity of the proposed PV-DVS algorithm is given as  $\mathcal{O}(n \cdot m(4n+c))$ . Note that the extendable task queue  $\mathbb{Q}_E$  is progressively reduced from length n to zero. The reduction is not uniform since it might occur that suddenly (at the same time) many tasks become inextensible and are excluded from the queue. This, additionally, indicates that the complexity is valid for the worst case. П

Fig. 7. Second task graph example

# 3.2 DVS optimised Scheduling

This section is concerned with the scheduling problem for heterogeneous distributed systems containing power managed DVS-PEs. In Section 3.1, we have shown that our generalised DVS algorithm is able to further improve the scaling voltages for the already scheduled tasks, which are mapped to DVS-PEs. However, as mentioned in Section 2, the task scheduling greatly influences how efficiently DVS can be exploited. Simply put, the more slack is available in the schedule, the higher the achieved energy savings by exploiting DVS will be. Again, this becomes more complex and does not hold always for distributed systems under the proposed generalised power model (considering the power profiles) when compared with a fixed power model. In such a case, the available slack for high energy dissipating tasks should be considered more important than the slack of tasks consuming a minor amount of power.

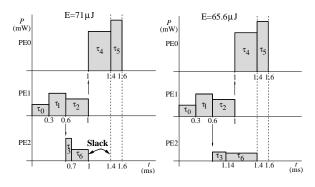

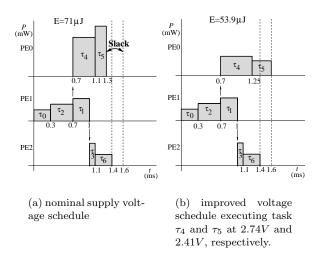

# Motivational Example 2: Energy Conscious Scheduling

The purpose of this motivational example is to illustrate the importance to take the PE power profile into account while scheduling tasks and communications in the presence of DVS-PEs. It highlights the importance to take into account the power dissipations for different DVS-PEs, in order to make DVS conscious scheduling decisions.

The specification task graph shown in Figure 7 is mapped to an architecture consisting of three heterogeneous and power managed DVS-PEs, linked through a single bus. Table IV(a) gives the execution time, power dissipation, and the mapping of each task. Additionally, the values for the nominal supply voltage  $V_{max}$  and the threshold voltage  $V_t$  of each PE are given in Table IV(b). For the sake of simplicity, in this example, the communications are considered to be instantaneous. Figure 8(a) shows a feasible schedule for the mapped tasks, executing at nominal supply voltage. This schedule results in an energy dissipation of  $71\mu J$ , according to the values given in Table IV(a). It can be observed that task  $\tau_6$  has a deadline at 1.4ms but it finishes its execution after 1.0ms, which results in an available deadline slack of 0.4ms. This slack time can be used to extend the tasks and hence reduce the supply voltage of the PE during the task execution. However,  $\tau_3$  and  $\tau_6$  are the only extendable tasks, and any other extension of the remaining tasks cannot be tolerated, since task  $\tau_5$  finishes execution just on deadline and the tasks  $\tau_0$ ,  $\tau_1$ , and  $\tau_2$  influence the start and end time of task  $\tau_5$ . Therefore, an optimal DVS schedule

$\overline{Task}$ exec. $time (\mu s)$ power dis. $\overline{(mW)}$ mapping0.30 10 PE1  $\tau_0$ 0.30 20 PE1  $\tau_1$ 0.4015 PE1 $\tau_2$ 0.1040 PE0 $\tau_3$ PE2 0.40 70  $\tau_4$ 0.20 90 PE2  $\tau_5$ PE0  $\tau_6$ 0.3020

Table III. Task and processing element information

(a) Execution times, power dissipations, and mapping for the tasks of task graph 2, when running at nominal supply voltage

| PE | Nominal supply     | Threshold     |

|----|--------------------|---------------|

|    | $voltage\ V_{max}$ | Voltage $V_t$ |

| 0  | 3.3V               | 0.8V          |

| 1  | 2.5V               | 0.6V          |

| 2  | 3.3V               | 0.8V          |

(b) Nominal supply voltage and threshold voltage of each DVS-PE

- (a) execution at nominal supply voltage

- (b) optimal voltage schedule for the given execution order

Fig. 8. A possible schedule, satisfying the given time constraints

for this configuration must only extend tasks  $\tau_3$  and  $\tau_6$ . Taking the power profile of PE2 into account the optimal supply voltages can be calculated as 2.08V and 2.34V for  $\tau_3$  and  $\tau_6$ , respectively. This results in the reduced power dissipations  $P_3 = 6.63mW$  and  $P_6 = 5.39mW$ . Using the optimised supply voltages, the total

Fig. 9. Second schedule of the same task graph, satisfying the timing constraints and optimised for PV-DVS

energy dissipation is reduced to  $65.61\mu J$ , which is a 7.6% reduction.

Now, consider the nominal supply voltage schedule given in Figure 9(a). It can be observed that the energy dissipation is again  $71\mu J$ , since task mapping and voltages are the same as in Figure 8(b). The given schedule also satisfies all timing constraints. Unlike the previous schedule, in this sequencing of tasks, it is not possible to extend tasks  $\tau_3$  and  $\tau_6$ , since task  $\tau_6$  ends its execution just on deadline. However, observing tasks  $\tau_4$  and  $\tau_5$  reveals an available slack of 0.3ms. It is important to note that this available slack is smaller than the one given in Figure 8(a), and therefore an energy optimisation neglecting the power variation among PEs and tasks would prefer the solution in Figure 8. Nevertheless, the extensions of task  $\tau_4$  and  $\tau_5$  allow to scale the PE speed down. The optimal voltages for this configuration can be calculated as 2.74V and 2.41V, for  $\tau_4$  and  $\tau_5$ , respectively. Using this supply voltages allows to reduce the power dissipations to  $P_4 = 34.93mW$  and  $P_5 = 27.29mW$ . In this way the dynamic energy dissipation is reduced to  $53.89\mu J$ , leading to a 24.1% improvement. This is a significant reduction compared to the achieved 7.6% when the power variations between PEs and tasks are neglected.  $\Box$

3.2.1 DVS Optimisation using Genetic List Scheduling. Our scheduling algorithm for the generalised DVS problem uses a genetic list scheduling approach (GLSA) to optimise the execution order of tasks towards energy reduction and timing feasibility. Unlike previous scheduling approaches that try to improve DVS utilisation using constructive heuristics, the presented algorithm is based on an iterative optimisation which enables a thorough search through the solution space.

It has been shown in [Dhodhi et al. 1995; Grajcar 1999] that the combination of genetic algorithm and list scheduling provides a powerful tool for the synthesis of multiprocessor systems. The main advantages of GLSA approaches over traditional constructive list scheduling methods are:

- —The objective, which needs to be optimised, can be based on an arbitrary complex function.

- —The enlarged search space (at most  $(|\mathcal{T}| + |\mathcal{C}|)$ ! different schedules can be produced) provides the opportunity to find solutions of potentially higher quality.

- —There is a large freedom to trade-off between acceptable synthesis time and solution quality, as opposed to constructive techniques where only one solution is produced.

- —GAs with parallel populations and migration scheme provide a powerful approach to leverage additional computational power of computer clusters, which are becoming more and more commonplace.

- —Multi-objective optimisation is an important feature which is supported by genetic algorithms. It provides the opportunity to simultaneously optimise the implementation towards competing goals and allows the system designer to choose among several suitable implementations with different properties.

A detailed functional description of genetic list scheduling approaches can be found in [Dhodhi et al. 1995; Grajcar 1999]. Nevertheless, our implementation varies in two fundamental issues from this previous research:

- —Instead of optimising the schedule solely for timing behaviour (reducing the makespan<sup>1</sup>), we consider additionally the issue of energy minimisation with respect to DVS.

- -The algorithms described in [Dhodhi et al. 1995] and [Grajcar 1999] employ a list scheduler which determines not only the execution order of tasks but also their mapping. We avoid this combination because of the greediness problems described in [Kalavade 1995] which might lead to infeasible mappings due to exceeded area constraints (memory and gates) of pre-allocated hardware components. A list scheduling, including the mapping step, serially traverses all nodes of the task graphs and maps them to allocated components based on local decisions taken in each step. This might lead to low quality solutions, as opposed to approaches in which mapping is decided in an external loop, based on iterative improvement techniques. Another problem, which occurs when determining the mapping during the list scheduling processes, is that the execution times and power dissipations of the mapped tasks are influenced by the voltage scaling. Therefore, the mapping decisions based on these values might prove to be wrong. For example, mapping a task to a low power consuming ASIC might involve an expensive development of hardware, while the mapping of the same task onto a DVS-enabled ASIP might prove satisfactory when the task execution is scaled.

List scheduling algorithms make scheduling decisions based on task priorities and determine static schedules. Unlike constructive list scheduling techniques that use a sophisticated algorithm for the priority assignment, genetic list scheduling techniques construct and evaluate many different schedules during an iterative priority optimisation process. By encoding the task priorities into a priority string, it becomes possible to utilise genetic operators (crossover and mutation) to change task

<sup>&</sup>lt;sup>1</sup>Makespan is duration from starting the first task until the last task finishes execution.

Fig. 10. Task priority encoding into a priority string

priorities and hence generate new scheduling solutions using static list scheduling. Figure 10 shows the encoding and the relations between priority string and tasks. To preserve some string locality, important for an efficient search when using GAs [Goldberg 1989], the priorities are ordered in the same way as visited by a breadthfirst search. Now we give an overview of our DVS optimised genetic list scheduling algorithm, as shown in the optimisation Step 2 of Figure 2. The solution pool (25 individuals) of the first generation is initialised half by mobility-based [Wu and Gajski 1990] and half by randomly generated priorities (with values between the lowest and highest mobility), respectively. This initial population was empirically found to be a good starting point, leading to fast convergence. The algorithm then enters the main schedule optimisation loop, which is repeated until no improvement of at least 1% (with respect to the best found feasible schedule) is made for 10 generations. Each iteration of the loop goes successively through the following steps: All new priority candidate strings in the solution pool are used by the list scheduling algorithm to generate schedules at nominal supply voltage. Our implemented list scheduler relies solely on the task priorities to make schedule decisions, i.e., no other techniques, like e.g. hole filling, are used to optimise the schedule. Although such techniques can improve the timing behaviour by eliminating idle periods in the schedule, we dissociate from them since the DVS technique exploits exactly these idle times. The algorithm proceeds by passing the built schedules to the previously presented PV-DVS algorithm (Section 3.1.2), which identifies scaling voltages that minimise the energy dissipation. Note that schedules which exceed hard deadline constraints are still scaled as much as possible and are not excluded from the optimisation, since good solutions are likely to be found as result of transformations performed on invalid configurations. However, a violation penalty is applied in such cases, as explained next. The scaled schedule is evaluated in terms of deadline violations and energy dissipation including DVS reductions. Based on this evaluation, the fitness  $F_S$  of each schedule candidate is calculated using the following equation:

$$F_{S} = \left(\underbrace{\sum_{\tau \in \mathcal{T}} P(\tau) \cdot t_{exe}(\tau)}_{\text{task energy}}\right) + \underbrace{\left(\sum_{\gamma \in \mathcal{C}} P(\gamma) \cdot t_{exe}(\gamma)\right)}_{\text{comm. energy}}\right) \cdot \underbrace{\left(1 + \frac{\sum_{\tau \in \mathcal{T}_{d}} DV_{\tau}^{2}}{T_{HP}^{2}}\right)}_{\text{Time Penalty}},$$

(9)

$$DV_{\tau} = \max \left( 0, \left( t_S(\tau) + t_{exe}(\tau) \right) - t_d(\tau) \right)$$

where P and  $t_{exe}$  denote power dissipation and execution time of task  $\tau$  or communication activity  $\gamma$ , summed to calculate the total dynamic energy dissipation which needs to be minimised. Note that the power dissipations and the execution times of the tasks depend on the found scaling voltages  $V_{dd}$ . In order to assign a deadline violation penalty, the energy value is multiplied with a penalty factor based on the sum of the squared deadline violations.  $T_{HP}$  is the hyper task graph period (least common multiplier of all task graph periods) used to normalise the deadline violation. Squaring has been applied in order to apply a higher penalty to larger violations of imposed deadlines. By guiding the optimisation with this fitness function, the search for schedules is pushed into regions where low energy and feasible schedules are likely to be found. The algorithm then checks the halting criterion as mentioned above. If the end of the optimisation has not been reached the algorithm continues, and the new priority candidates are ranked and inserted into the solution pool based on their fitness values. Low ranked individuals of the pool are replaced by new ones, which are generated through genetic crossover and mutation. We use a steady state GA, due to its performance advantage compared to generational GAs as indicated in [Rogers and Prügel-Bennett 1999], with a generation gap of 50%, i.e., half of the individuals in the solution pool survive unchanged in each generation. The crossover is carried out by means of a random two point crossover. To avoid a premature convergence towards suboptimal schedules we leverage the idea of a dynamic mutation probability [Fogarty 1989]. This approach gives the algorithm the additional capability to easily escape local minima in the beginning of the optimisation run. The mutation probability follows the equation  $1/\exp(N_S \cdot 0.05)$  and is never allowed to drop below 15%.  $N_S$  denotes the current generation during the schedule optimisation. At this point, the next iteration is invoked and so different schedules are tried out. The experimental results, given later in Section 4.2, indicate the advantages of our approach in optimising the schedule towards DVS usability when compared to conventional constructive list scheduling approaches.

#### 4. SYNTHESIS EXPERIMENTS

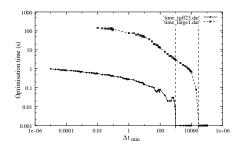

To demonstrate the efficiency and the applicability of the proposed generalised DVS synthesis technique in reducing the energy dissipation of heterogeneous distributed systems containing power managed PEs, we have carried out numerous experiments and comparisons with power neglecting approaches. The PV-DVS and scheduling algorithm as outlined in the previous section have been implemented on a Pentium-III/750MHz Linux PC with 128MB RAM. We have used 68 experimental benchmark examples, partially taken from previously published literature [Gruian 2000; Bambha et al. 2001; Hou and Wolf 1996] and generated using TGFF [Dick et al. 1998], to cover a wide spectrum of application diversity. To demonstrate the real-world applicability of the presented work, we carried out an additional set of experiments on an optical flow detection real-life example. The complexity of the used task graph examples varies between 8 to 100 tasks and 7 to 151 edges. The amount of PEs and CLs in the component libraries varies between 4 and 16. These benchmarks are grouped into five major sets:

- 24

- (1) Our TGFF generated task graphs (tgff1-tgff25) consists of 8 to 100 tasks and are mapped to heterogeneous architectures containing power managed DVS PEs and non-DVS enabled PEs. Therefore, these examples show various power characteristics and component properties. The variations in power are up to 2.6 times on the same PEs. The examples tgff4\_t and tgff4\_fixed are identical to tgff4 with slight modifications; tgff4\_t denotes a task graph alternative with a critical tight deadline, while tgff4\_fixed uses only DVS-PEs with a fixed power dissipation.

- (2) The examples of Hou et al. [Hou and Wolf 1996] are hypothetical task graphs. Hou\_clustered represents the same functionality as Hou, but the task graph is collapsed from 20 to 8 tasks. Since the initial technology library does not contain any DVS-enabled PEs, we extended the given PEs to DVS-PEs with  $V_t = 0.8V$  and  $V_{max} = 3.3V$ . These examples also show different power dissipations (power variations) among the tasks.

- (3) Gruian's and Kuchcinski's graphs [Gruian and Kuchcinski 2001], used in our experiments, represent two sets (TG1 and TG2) of 30 randomly generated communicating tasks with tight deadlines (determined by a critical path scheduling algorithm). These graphs show a high degree of parallelism and are mapped to architectures built of 3 or 10 identical DVS-PEs, assuming constant power consumption. These PEs are multi-voltage processor able to run at 3.3V, 2.5, 1.7V, and 0.9V, while the threshold voltage V<sub>t</sub> is 0.4V.

- (4) The applications used by Bambha et al. [Bambha et al. 2001] consist of two differently implemented Fast Fourier Transforms (fft1 and fft3), a Karplus-Strong music synthesis algorithm (Karp10), a quadrature mirror filter bank (qmf4), and a measurement application (meas). These benchmarks are small real-life examples and use architectures composed of 2 to 6 identical DVS-PEs, assuming constant power consumption. Supply voltages are between 0.8 and 7 volts. The throughput constraints and initial average power consumptions are calculated at a reference voltage of 5 volts.

- (5) The final benchmarks represents a real-life example, consisting of 32 tasks. It is a traffic monitoring system based on an optical flow detection (OFD) algorithm. This application is a sub-system of an autonomous model helicopter [WITAS; Gruian and Kuchcinski 2001].

In our experiments, we assume that computation and voltage scaling can be carried out concurrently, as is the case of the processor introduced in [Burd 2001]. Further, we neglected the time overhead needed by the processor to switch between two supply voltages (for real-life DVS processors this is in the range of  $10-70\mu s$  for a full transition from the highest to the lowest supply voltage and vice versa [Burd 2001]), since the used tasks are considered to be of coarse granularity (in the range of 1-100ms). Therefore, the switching overhead can be considered to be only a small fraction of the total task execution time. However, in the case of fine grained tasks this overhead might influence the voltage selection and should then be considered. All results presented here, except the deterministic ones given in Section 4.1, were obtained by running the optimisation process ten times and averaging the outcomes.

NO-DVS EVEN-DVS Presented Approach No. of ExampletasksReduc.EnergyReduc. EnergyEnergyedgesDissipDissip(%)Dissip(%) tgff1 8 / 9 26 / 43 355 193.49 45.50112.87 68.21 tgff2 26 743224722412.152.80 683954.54 tgff3 40 / 77 554779 410653.67 25.98267651.03 51.76tgff4 20 / 33 431631 402904.08 6.66 375914.03 12.91 20 / 33 412854.36 7.98 tgff4\_t 4.35 397201.93 431631 20 / 33 142986.91 29.32 tgff4\_fixed 176723 19.09 124905.61 tgff5 40 4187382 3963647.60 5.34 3767450.2510.03 tgff6 20 / 26 1419124 1401605.68 1.23 1396445.06 1.60 10.16 1951579.52tgff7 20 27 2548751 2289878.34 23.4318 / 26 tgff8 1913519 1774151.42 1668485.33 12.81 16 / 15 tgff9\* 2.25 996590 974159.01 918048.34 7.88 tgff10 16 / 21 26.08 46483.97 32.9769352 51263.60 4349627 4293736.56 4263279.98 tgff11 30 / 29 1.28 1.99 tgff12 36 / 50 2316431 2243710.55 3.14 2212111.25 4.50 16.73 19.89 tgff13 37 / 36 2912660 2425431.77 2333338.86 tgff14 24 / 33 15532 13546.62 12.7812479.41 19.65 40 / 63 tgff15 62607 62078.93 0.84 60334.62 3.63 tgff162913341.14 2518711.99 27.92 31 / 56 3494478 16.63 tgff17 29 / 56 23459 20396.41 13.06 18334.01 21.85 tgff18 12 / 15 1851688 1851687.99 0.00 1526059.97 17.59 tgff19 14 5939 4713.59 20.634395.37 25.99 19 / 25 tgff20' 77673 48334.30 37.77 40280.98 48.14 70 / 99 tgff21 2658534.22 3177705 3175497.22 0.07 16.34 5036657.40 tgff22 100 / 1355821498 13.484445545 63 23.64 tgff23' 84 / 151 11567283 10791880.89 6.70 10133912.03 12.39 tgff24 5349024.86 5238478.58 80 1112 5352217 0.06 2.13 tgff25 49 / 92 5735038 5648816.00 1.50 5502681.64 4.05Hou' 20 / 29 13712 10337.05 24.61 7474.5545.49

Table IV. Comparison of the presented PV-DVS optimisation with the EVEN-DVS approach (scheduling and mapping are fixed)

14546

# 4.1 Performance of the Generalised DVS Algorithm

8 / 7

Hou\_clust.

To demonstrate the influence of power variations on the efficiency of DVS, we compare our approach, which takes the power profile into account, with a power neglecting approach. This power neglecting approach (in the following referred to as EVEN-DVS) is based on the idea to distribute available slack time *evenly* among the processing elements, somewhat similar to the voltage scaling idea used in [Luo and Jha 2000]. However, since the mapping and scheduling approach proposed in [Luo and Jha 2000] targets also additional different objectives, a direct comparison is not valid.

11543.35

20.64

10270.32

29.39

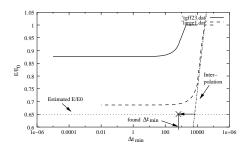

Table IV shows a comparison between the EVEN-DVS and the proposed DVS approach. In order to judge the complexity of the individual benchmark examples, the table gives the number of nodes and edges in the task graphs. The comparison between the two DVS approaches is carried out with respect to the energy dissipation when no DVS is employed (see Column NO-DVS). Consider for example benchmark tgff17, which consist of 29 tasks and 56 communications between tasks. The unscaled execution (NO-DVS) of the application dissipates an energy of 23459. Using an even distribution of slack time (EVEN-DVS) this power consumption can be reduced to 20396, a reduction of 13.1%. However, using the proposed generalised DVS algorithm the dissipated energy is further reduced to 18334, when

<sup>\*</sup>Components used for these examples consists of DVS-PEs only

| Table V. 1 V-D VB results using the benchmark set of Banibha et al. |        |         |                   |          |           |  |  |  |

|---------------------------------------------------------------------|--------|---------|-------------------|----------|-----------|--|--|--|

|                                                                     | No. of | NO-DVS  | Proposed Approach |          |           |  |  |  |

| Example                                                             | Nodes/ | Energy  | Energy            | CPU      | Reduction |  |  |  |

|                                                                     | Edges  | Dissip. | Dissip.           | time (s) | (%)       |  |  |  |

| fft1                                                                | 28/32  | 29600   | 18172             | 0.21     | 38.61     |  |  |  |

| fft3                                                                | 28/32  | 48000   | 36890             | 0.14     | 23.15     |  |  |  |

| karp10                                                              | 21/20  | 59400   | 44038             | 0.12     | 25.86     |  |  |  |

| meas                                                                | 12/12  | 28300   | 25973             | 0.11     | 8.22      |  |  |  |

| qmf4                                                                | 14/21  | 16000   | 12762             | 0.11     | 20.24     |  |  |  |

Table V. PV-DVS results using the benchmark set of Bambha et al

compared to NO-DVS a reduction of 21.8%.