Hardware/Software Codesign

Modeling - 2

## **Common Models of Computation**

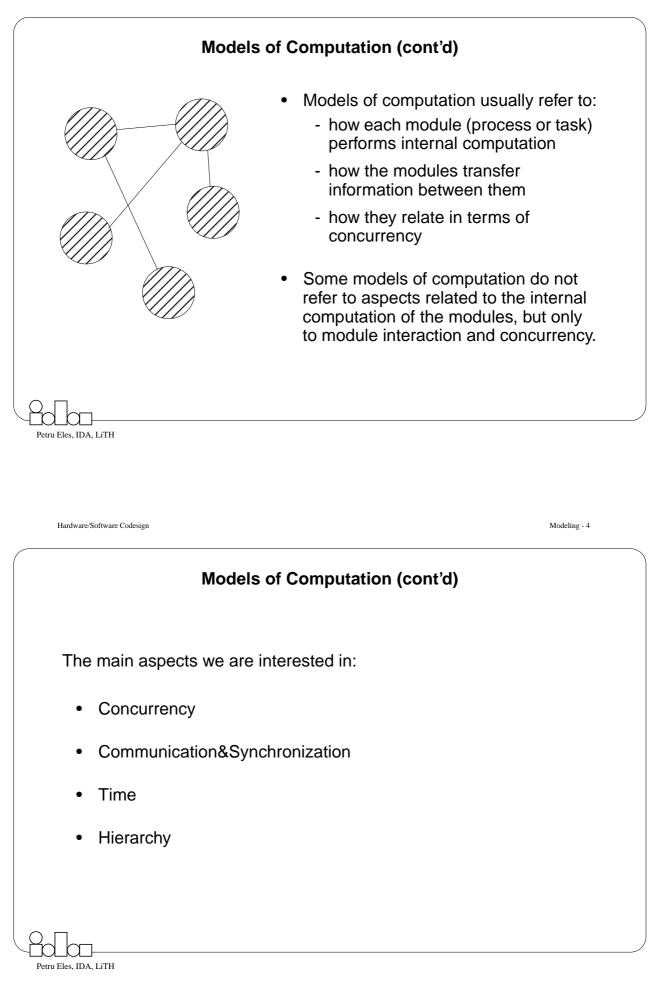

Some of the models of computation commonly used to describe embedded systems:

- (Synchronous) Finite State Machines

- GALS Models

- Dataflow Models

- Petri Nets

- Discrete Event

- Timed Automata

Petru Eles, IDA, LiTH

Hardware/Software Codesign

Modeling - 6

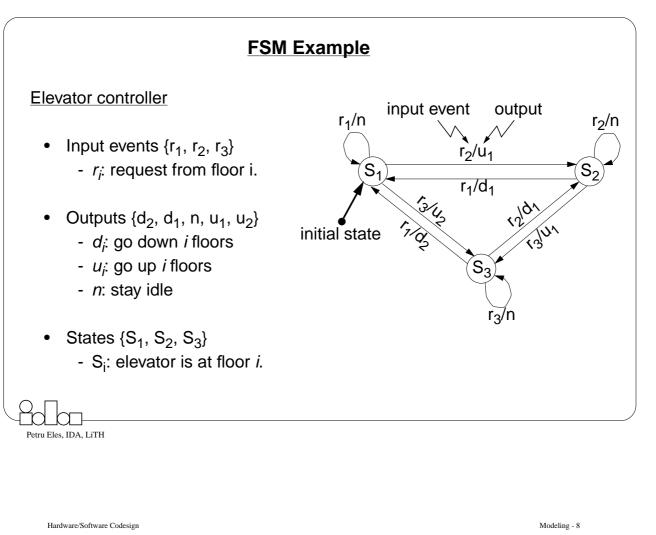

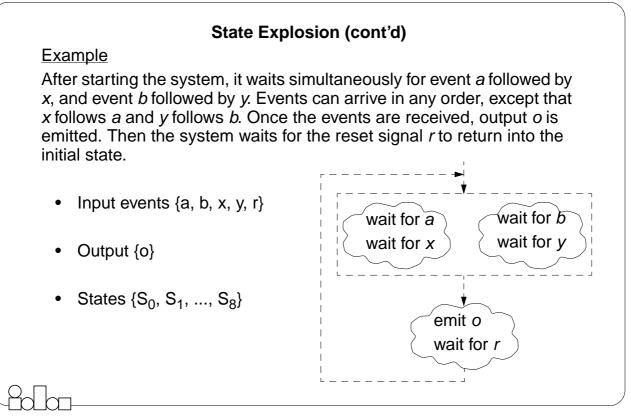

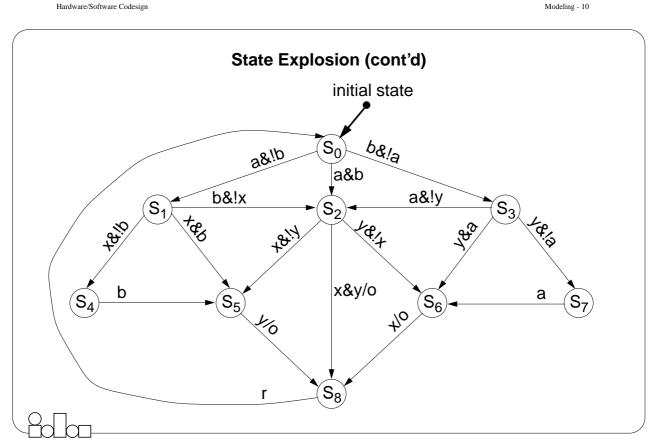

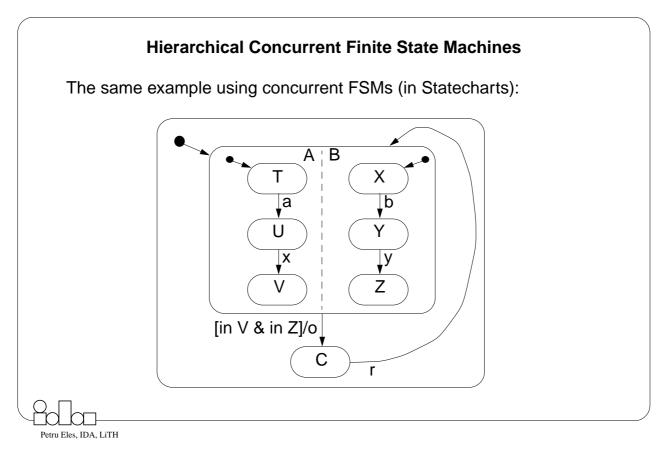

# Finite State Machines The system is characterised by *explicitly* depicting its states as well as the transitions from one state to another. One particular state is specified as the initial one States and transitions are in a finite number. Transitions are triggered by input events. Transitions generate outputs. FSMs are suitable for modeling control dominated reactive systems (react on inputs with specific outputs; not much computation)

Modeling - 12

```

Hardware/Software Codesign

```

### Hardware/Software Codesign

Modeling - 16

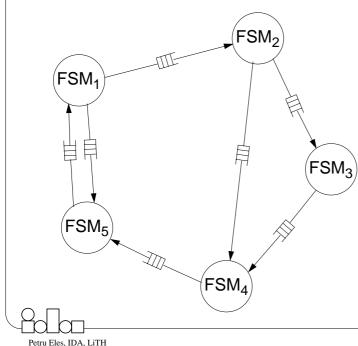

## **Globally Asynchronous Locally Synchronous Systems**

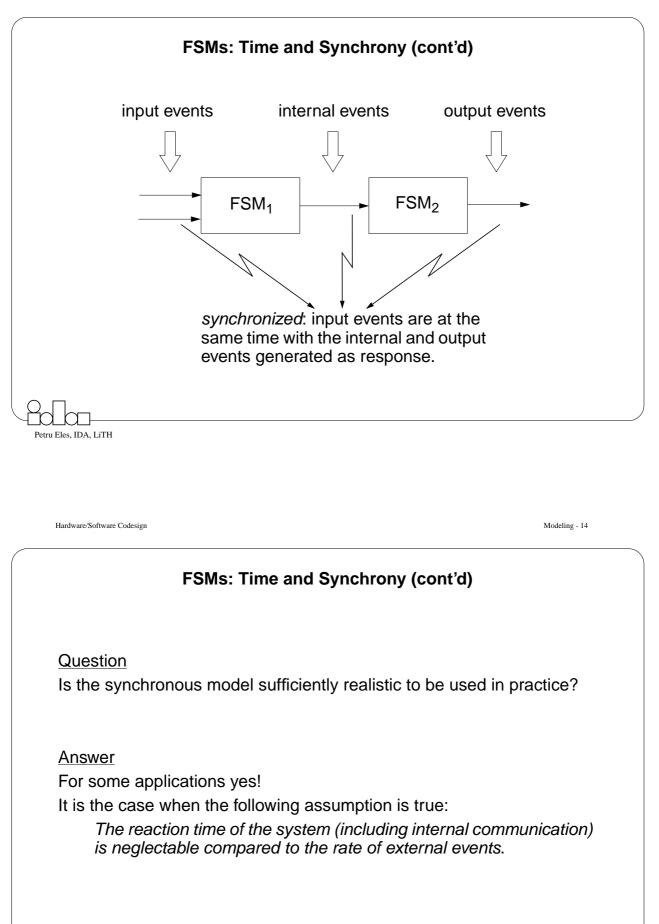

Globally asynchronous and locally synchronous (GALS) models:

- Each FSM individually behaves like a synchronous systems ⇒ reacts instantaneously on a set of available inputs and generates output.

- The global system is asynchronous ⇒ communication time is finite and non-zero; reaction time of each FSM, as viewed by other FSMs is finite and non-zero.

- With global asynchrony, buffering of signals could be needed.

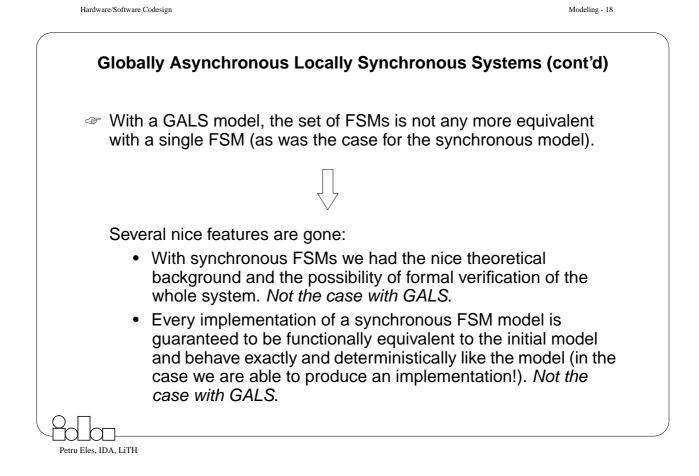

### Globally Asynchronous Locally Synchronous Systems (cont'd)

- Each individual FSM can be still verified and even formal methods can be used.

- However, individual correctness of each FSM does not guarantee the correctness of the whole system. The system behaves correctly only if, in addition, certain assumptions regarding the timing of components and of communications are satisfied.

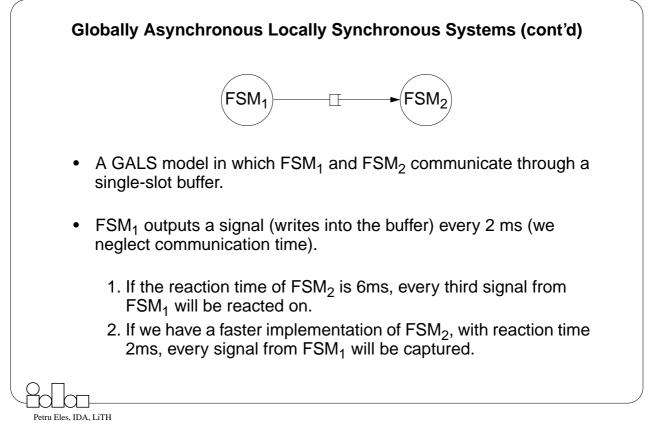

Example on previous slide:

- Each FSM can be functionally verified individually.

- The global system will be correct (no signal is lost) if FSM<sub>2</sub> has a reaction time which is smaller than the production rate of FSM<sub>1</sub>.

- Estimation and simulation can be used in order to verify that a certain implementation (like FSM<sub>1</sub> as software on a certain μprocessor, and FSM<sub>2</sub> as an ASIC) satisfies this assumption.

Petru Eles, IDA, LiTH

<text><text><list-item><list-item><list-item>

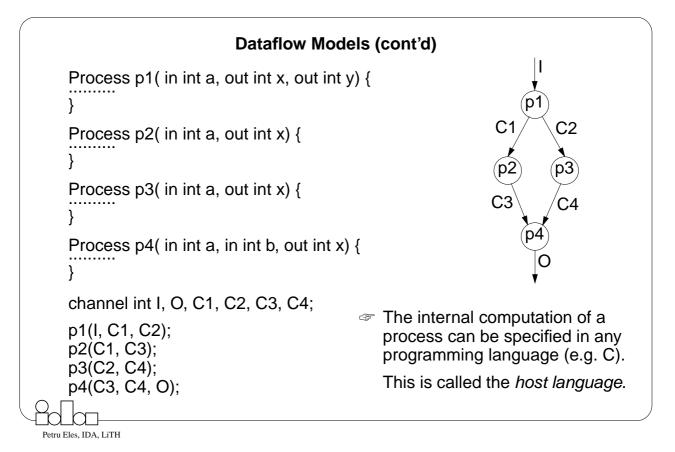

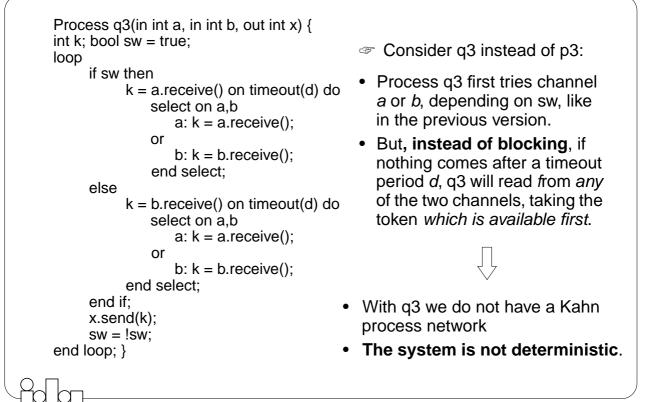

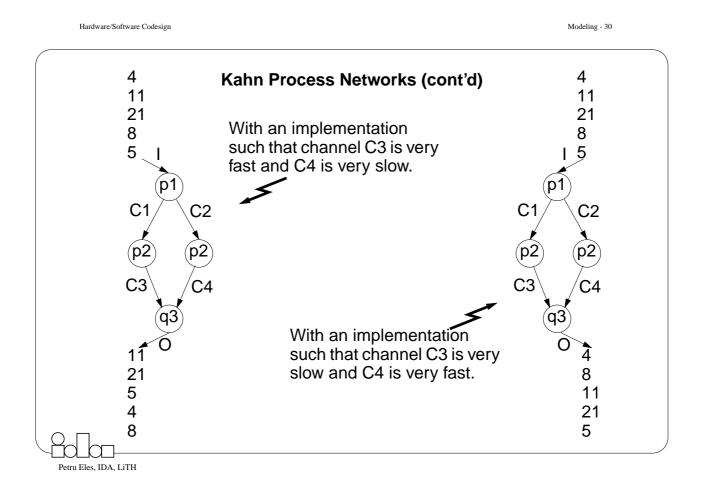

Hardware/Software Codesign Modeling - 26 Kahn Process Networks Processes communicate by passing data tokens through unidirectional FIFO channels. Writes to the channel are non-blocking. Reads are blocking: Non-blocking communication - the process is blocked until there is sufficient data in the channel A process that tries to read from an empty channel waits until data is available. It cannot DETERMINISM ask whether data is available *before* reading and, for example, if there is no data, decide not to read that channel. Petru Eles, IDA, LiTH

| Hardware/Software Codesign                                                                                                                                                                                                                            | Modeling - 28                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Kahn Process Networks (cont'd)                                                                                                                                                                                                                        |                                                          |

| <pre>Process p1( in int a, out int x, out int y) {     int k;     loop         k = a.receive();         if k mod 2 = 0 then             x.send(k);         else             y.send(k);         end if; end loop; }</pre>                              | 7<br>3<br>0<br>16<br>8<br>5<br>11<br>21<br>8             |

| Process p2( in int a, out int x) {<br>int k;<br>loop<br>k = a.receive();<br>x.send(k);<br>end loop; }                                                                                                                                                 | 5<br> I<br> P1<br>C1<br>C2                               |

| <pre>Process p3(in int a, in int b, out int x) {     int k; bool sw = true;     loop         if sw then             k = a.receive();         else             k = b.receive();         end if;         x.send(k);         sw = !sw; end loop; }</pre> | p2<br>p2<br>p2<br>p2<br>p2<br>p2<br>p2<br>p2<br>p2<br>p2 |

| channel int I, O, C1, C2, C3, C4;<br>p1(I, C1, C2);<br>p2(C1, C3);<br>p2(C2, C4);<br>p3(C3, C4, O);                                                                                                                                                   | 16<br>21<br>8<br>5<br>8                                  |

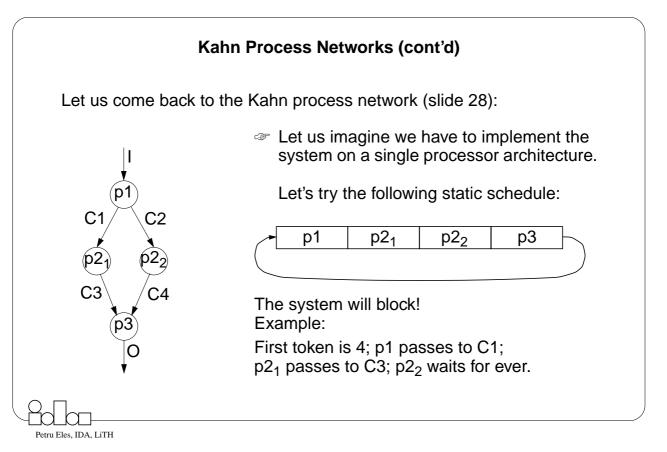

| Hardware/Software Codesign              | Modeling - 32                                                      |  |

|-----------------------------------------|--------------------------------------------------------------------|--|

| Kahn Process Networks (cont'd)          |                                                                    |  |

| Let's see some other schedules:         |                                                                    |  |

| p1 p2 <sub>2</sub> p2 <sub>1</sub> p3   | The system will block!<br>Example: first token 4.                  |  |

| p1 p2 <sub>1</sub> p3 p2 <sub>2</sub>   | The system will block!<br>Example: first token 4.                  |  |

| p1 p1 p2 <sub>1</sub> p2 <sub>2</sub> p | The system will block!<br>Example: sequence<br>starting with 4, 8. |  |

| Petru Eles, IDA, LiTH                   |                                                                    |  |

```

Another problem: memory overhead with buffers.

Potentially, it is possible that the memory need for buffers grows

unlimited (see channel C4 on slide 28).

```

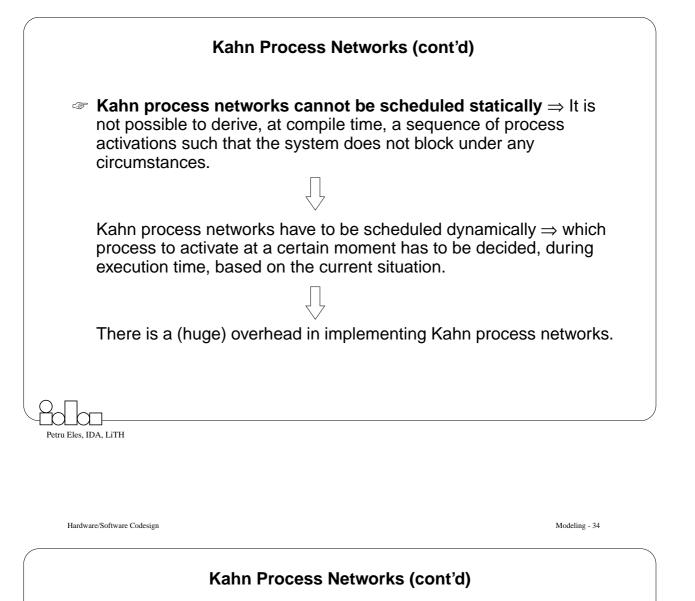

Kahn process networks are too general; they are strong in their expressive power but cannot be implemented efficiently.

Introduce limitations so that you can get efficient implementations.

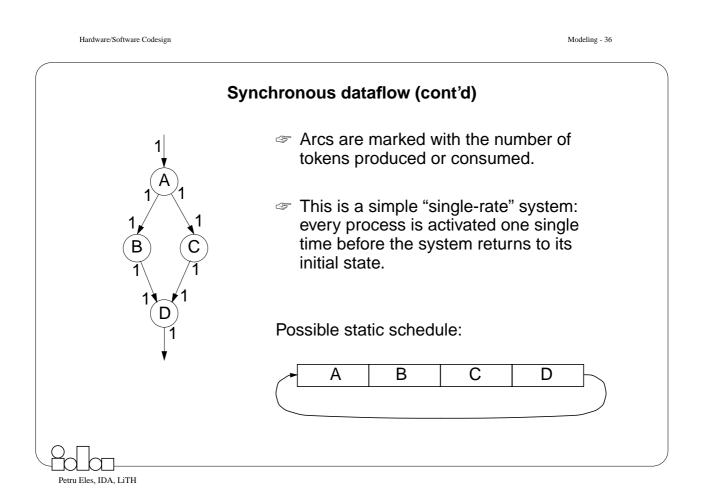

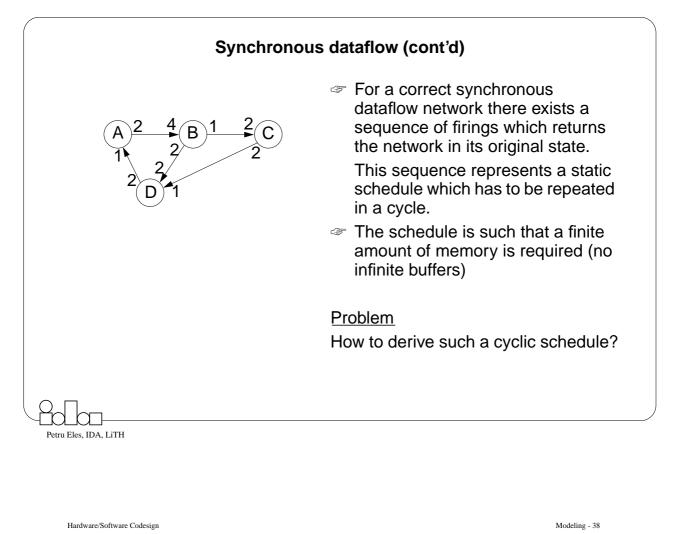

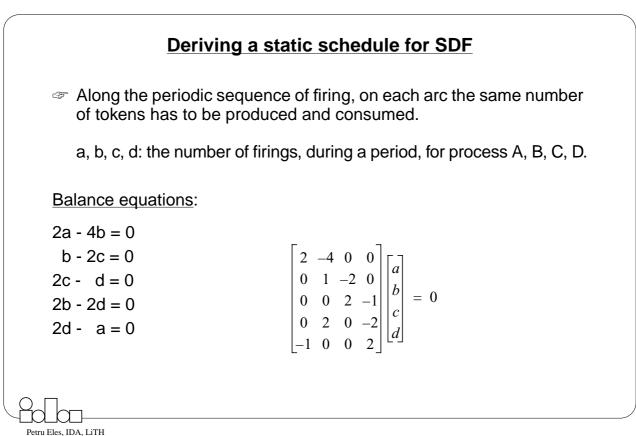

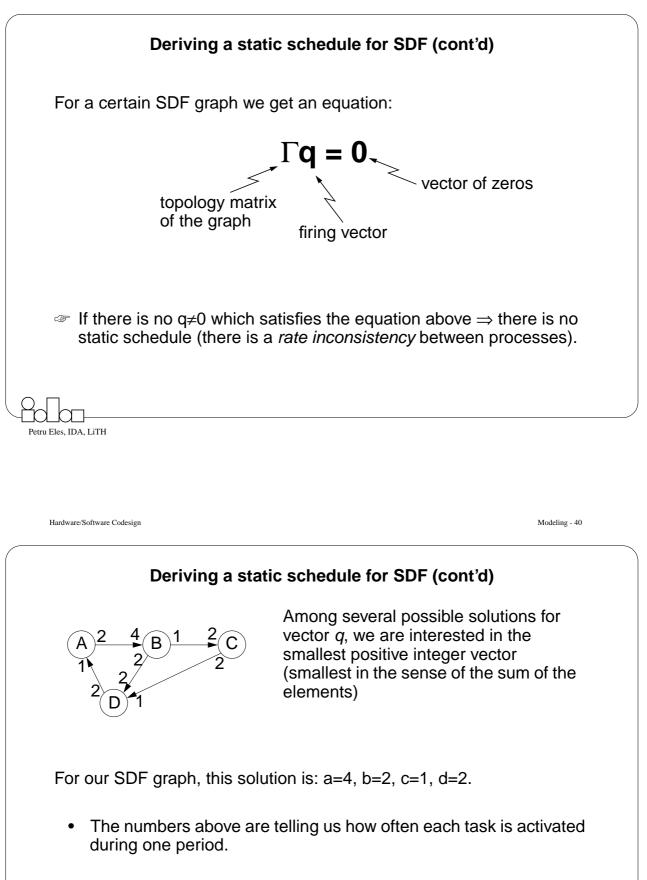

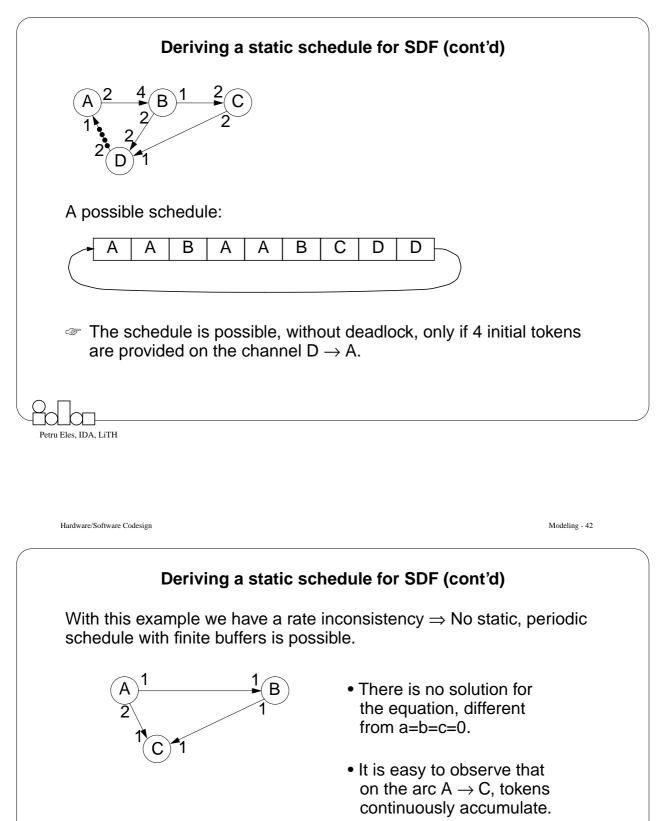

• Based on these numbers a periodic static schedule can be elaborated.

$\begin{array}{cccc} 1 & -1 & 0 \\ 0 & 1 & -1 \end{array}$

$2 \ 0 \ -1$

= 0

Hardware/Software Codesign

Modeling - 44

# Summary (cont'd) nenting synchronous systems can be done efficie

- Implementing synchronous systems can be done efficiently under certain circumstances. However, it is practically impossible for large systems and, in particular, distributed systems and, even more, hardware/software systems.

- For many systems and, in particular, larger distributed hardware/ software systems, only GALS is a realistic approach for implementation.

- Some of the nice features of synchronous FSMs are gone in this case. Formal reasoning about the global system is not possible any more.

Petru Eles, IDA, LiTH

Hardware/Software Codesign

Modeling - 46

### Summary (cont'd)

- Synchronous Dataflow Networks introduce an additional restriction: at each activation a process produces and consumes a fixed number of tokens.

- For a correct Synchronous Dataflow Networks a static schedule can be derived.

Don't use the "strongest" modeling approach! Go for exactly that expressive power you need; not more.