# System Synthesis of Digital Systems

Petru Eles, Zebo Peng

Literature:

P. Eles, K. Kuchcinski and Z. Peng "System Synthesis with VHDL" Kluwer Academic Publisher, December 1997.

# Examination:

- Term paper

- Seminar presentation

|                 | Introduction                                           |

|-----------------|--------------------------------------------------------|

|                 | 1. Digital System Synthesis                            |

|                 | 2. Lecture Topics                                      |

|                 | 3. Specification Domains and the Abstraction Hierarchy |

|                 | 4. The Y-Chart                                         |

|                 | 5. Synthesis Steps                                     |

|                 | 6. High Level Synthesis                                |

|                 |                                                        |

|                 |                                                        |

| Petru Eles, IDA | LTH March 2000                                         |

|                 |                                                        |

2

System Synthesis - Introduction

5

System Synthesis - Introduction

nbr

Petru Eles, IDA, LiTH

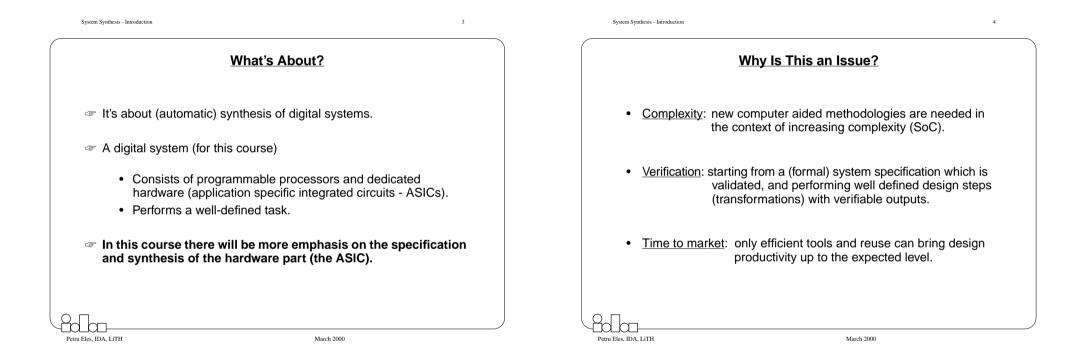

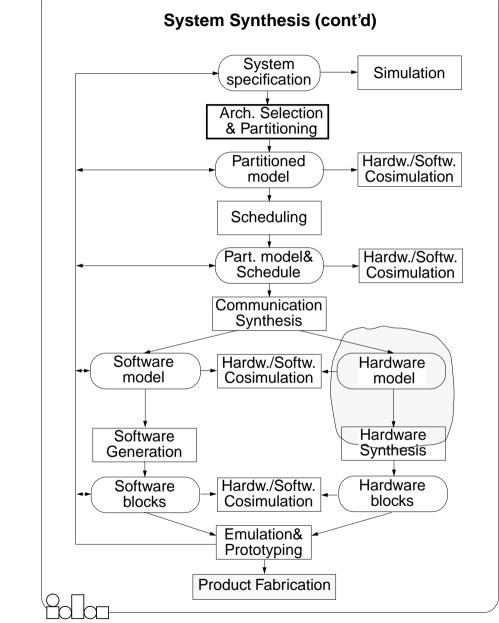

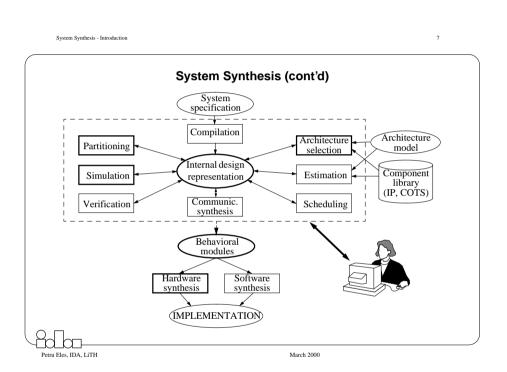

The synthesis tasks:

**System Synthesis**

Input: an implementation independent specification of the system; this

- To partition functionality over the components of the architecture;

- To generate behavioral modules corresponding to the hardware and software domain of the implementation, including in-

- The behavioral modules resulted from the previous steps are further synthesised into the actual hardware and/or software

March 2000

includes: functionality and constraints.

- To select the architecture:

- To schedule activities

terface modules.

implementation.

## Lecture Topics and Schedule

- 1. Introduction and Course Overview. System Synthesis and High-Level Synthesis.

- Thursday March 23, 10-12.

- 2. VHDL Basics and Simulation Mechanism.

- Thursday April 6, 10-12.

- 3. High-Level Synthesis.

- Thursday April 13, 10-12.

- 4. Basics of Transformational Approach.

- Thursday April 20, 10-12.

- 5. Optimization Heuristics for Synthesis.

- Thursday April 27, 10-12.

- 6. System-Level Synthesis and Hardware-Software Partitioning - I.

- Thursday May 11, 10-12.

- 7. System-Level Synthesis and Hardware-Software Partitioning - II.

- Thursday May 18, 10-12.

- 8. Synthesis of Advanced Features.

- Wednesday May 31, 10-12.

- 9. High-Level Synthesis for Testability.

- Thursday June 8, 10-12.

- 10.Presentation of Term Papers.

- Thursday June 15, 10-??.

Petru Eles, IDA, LiTH

#### System Synthesis - Introduction

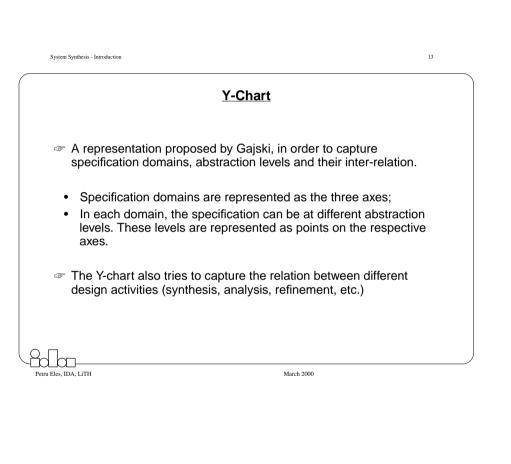

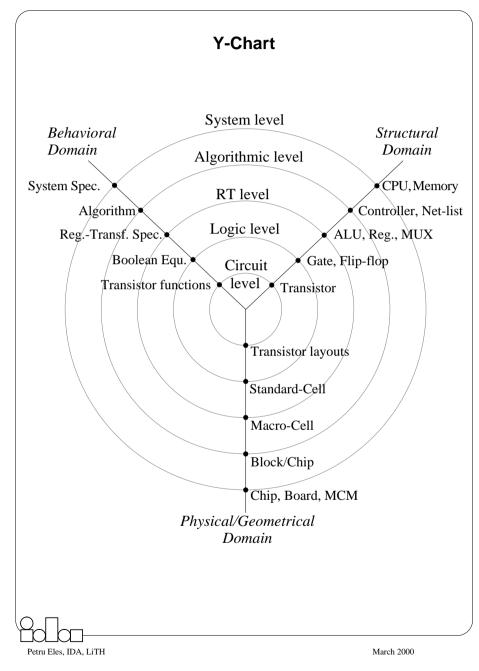

#### **Digital Systems - Specification Domains**

<u>Functional Domain</u>: emphasis is on behavior (input - output functionality), without any reference to the particular way in which this behavior is implemented.

<u>Structural Domain</u>: the specification is in terms of hierarchy of interconnected functional components.

<u>Physical/Geometrical Domain</u>: the specification is in terms of physical placement in space and physical characteristics without any elements to functionality.

nd br

Petru Eles, IDA, LiTH

March 2000

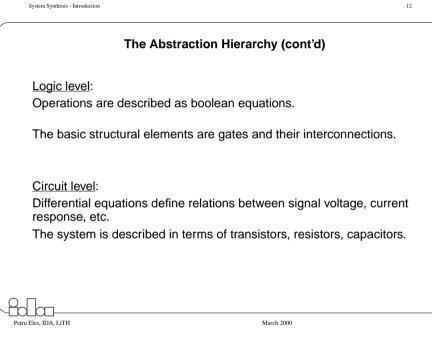

### **Digital Systems - The Abstraction Hierarchy**

#### System level:

The specification is given as a set of subsystems (modules/processes) which are loosely interacting (e.g. by exchanging messages).

The basic structural elements are processors, communication channels, ASICs, memories.

<u>Algorithmic level</u> (behavioral level):

The specification is given as an algorithm describing the functionality.

repeat

```

xl = x + dx;

ul = u - (3 * x * u * dx) - (3 * y * dx);

yl = y + u * dx;

c = xl < a;

x = xl; u = ul; y = yl;

until (c);

```

The basic structural elements are controller and net-list.

Petru Eles, IDA, LiTH

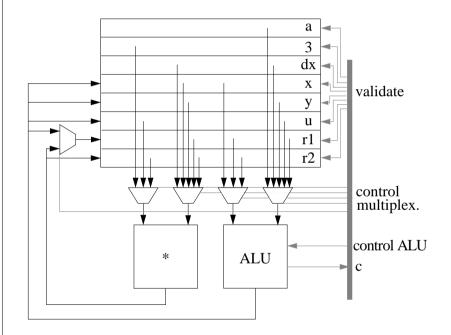

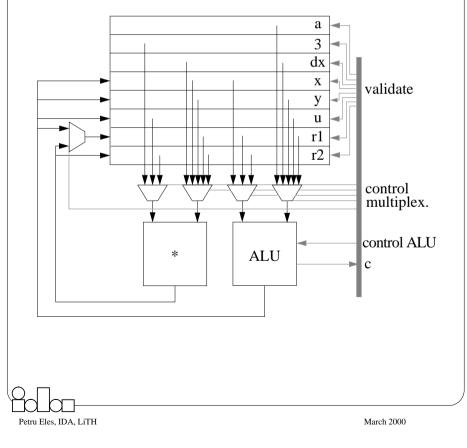

Register-transfer level:

Operations described as transfer of values between registers and functional units.

The basic structural elements are registers, ALUs, multiplexers and controller.

System Synthesis - Introduction

#### Synthesis Steps

17

Synthesis:

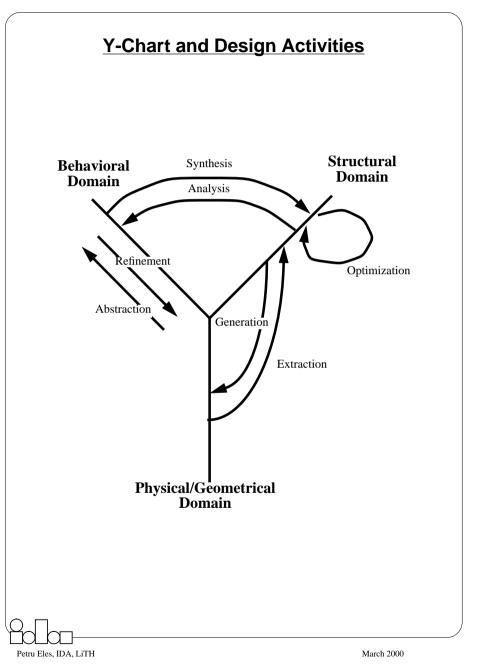

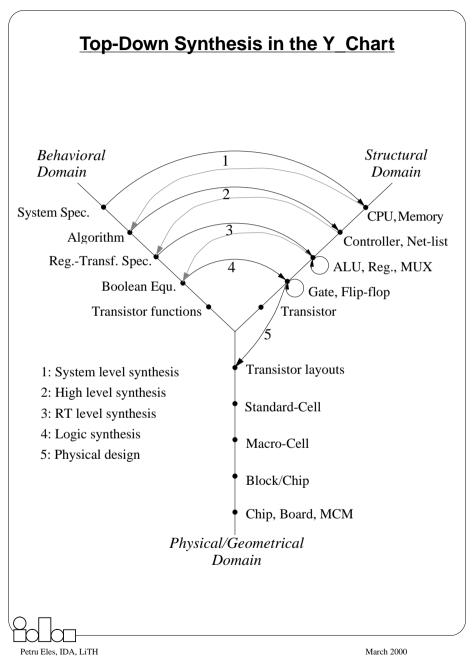

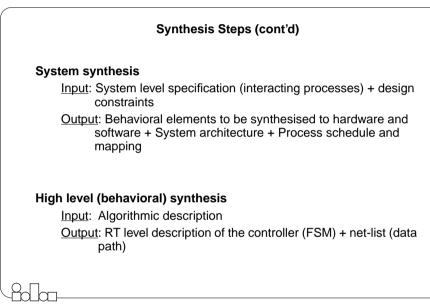

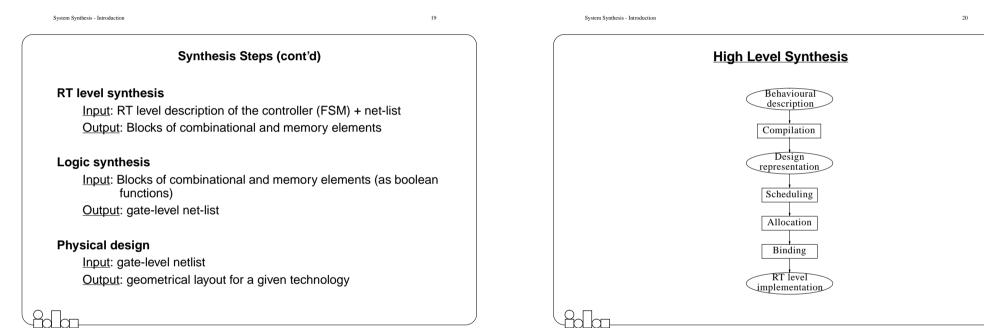

Transformation of a representation in the behavioral domain to a representation of the same design in the structural domain (at the same abstraction level).

The structural description which results after a synthesis step is formulated as an interconnection of abstract components.

Each such component is functionally specified at the following, lower abstraction level. These functional specifications are the input for the following synthesis step.

Petru Eles, IDA, LiTH

March 2000

Petru Eles, IDA, LiTH

System Synthesis - Introduction

March 2000

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

March 2000

March 2000

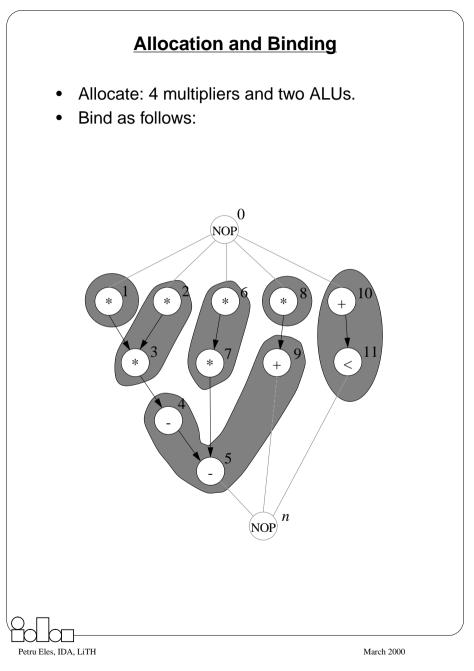

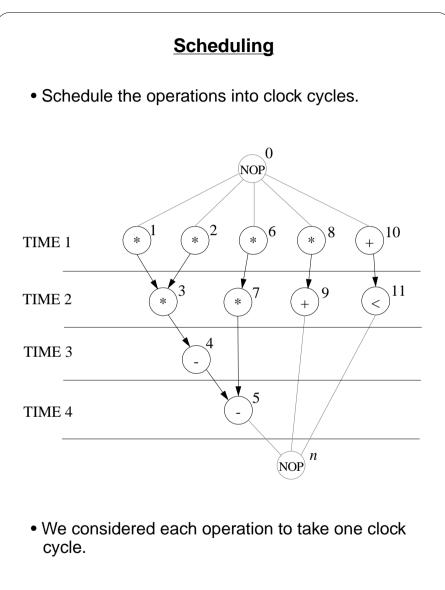

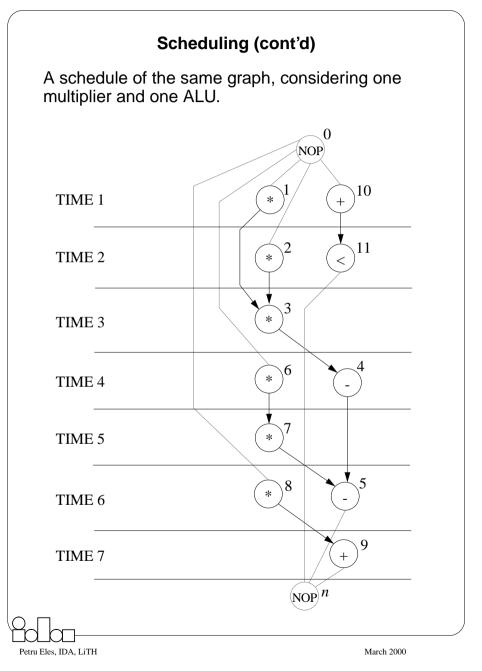

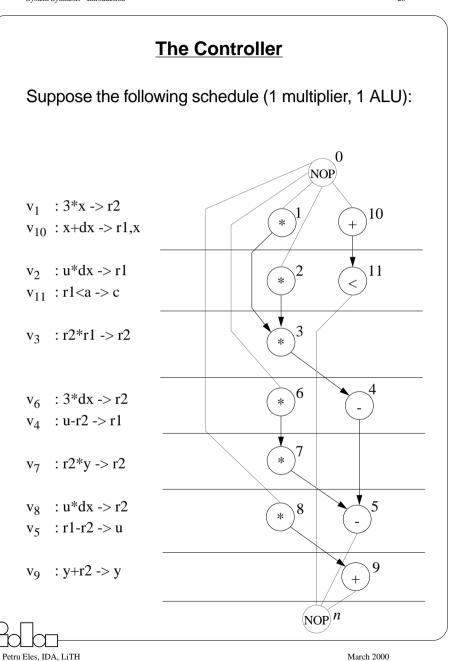

# u = u - (3 \* x \* u \* dx) - (3 \* y \* dx);x = x + dx;y = y + u \* dx;c = x < a;0 NOP u\*dx 8 $2^{y*dx}$ x+dx u\*dx 3\* 10\* \* +9 11 < п (NOP) Petru Eles, IDA, LiTH March 2000

From Algorithm to Design Representation

Petru Eles, IDA, LiTH

23

March 2000

System Synthesis - Introduction

repeat

$$xl = x + dx;$$

$$ul = u - (3 * x * u * dx) - (3 * y * dx);$$

$$yl = y + u * dx;$$

$$c = xl < a;$$

$$x = xl; u = ul; y = yl;$$

$$until (c);$$

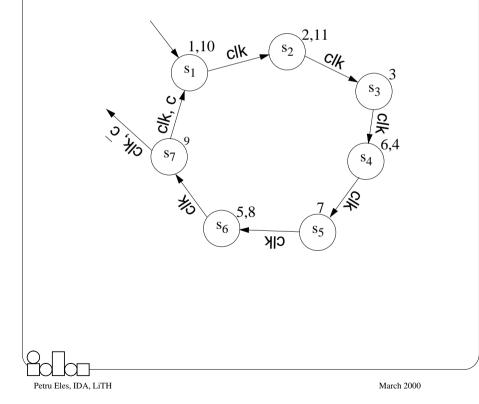

# The Controller (cont'd)

- One state for each clock cycle

- In each state the signals are generated which are needed in order to execute the operations scheduled for that cycle (see schedule).