#### **COTEST - Current Status**

#### **Zebo Peng**

Embedded Systems Lab (ESLAB)

Linköping University

### Recent Activities at LiU

- Hierarchical test generation

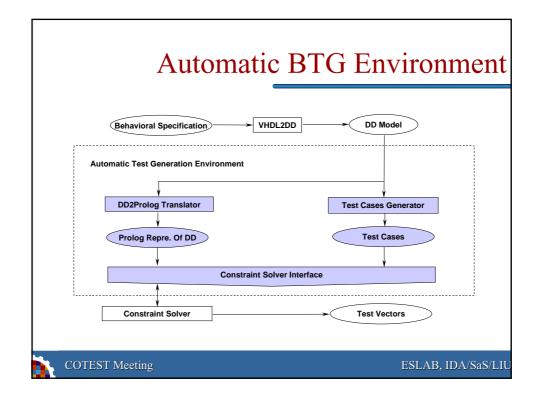

- Implementation using a constraint solver (Prolog)

- Extension to behavioral level descriptions

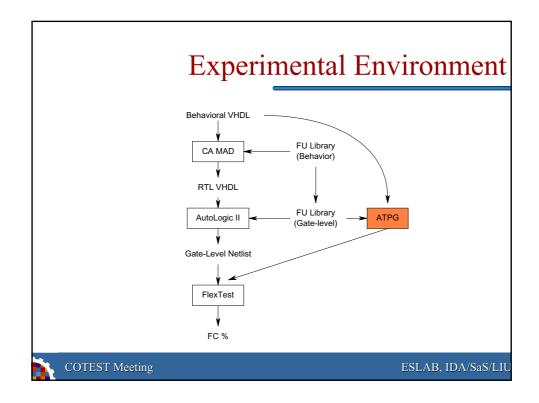

- Experimental work to demonstrate the efficiency of the proposed approach

- Insertion of testability into high-level design: Hybrid BIST

1

**COTEST Meeting**

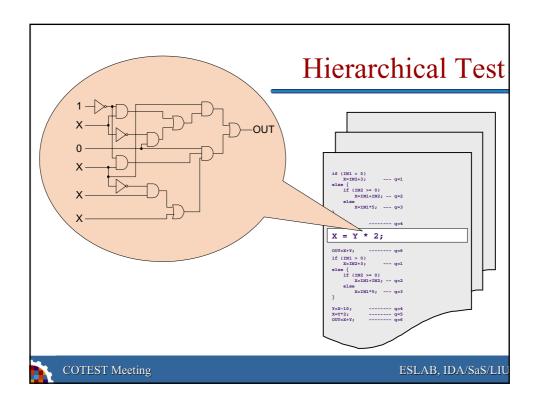

#### Hierarchical Test at Behavioral Level

- Using structural information in behavioral level test generation

- Use behavioral level for propagation and justification while tests for functional units are generated based on gate level representation

- An approach for early design space exploration to evaluate testability

- Fault coverage is measured on a structural level against stuck-at faults

N

**COTEST Meeting**

# Testing of behavior

- Introduction of control states into the specification

- Conversion of modified specification to DDs

- Test generation based on code coverage metrics

COTEST Meeting

## Testing FU-s

- Library of FU-s

- VHDL models on a behavioral/structural level

- DD models on a structural level

- PODEM algorithm for gate-level test generation

- With "intelligent" method to handle X values and constants

- Justification and propagation on a behavioral level

**COTEST Meeting**

**COTEST Meeting**

ESLAB, IDA/SaS/LIU

ESLAB, IDA/SaS/LIU

##

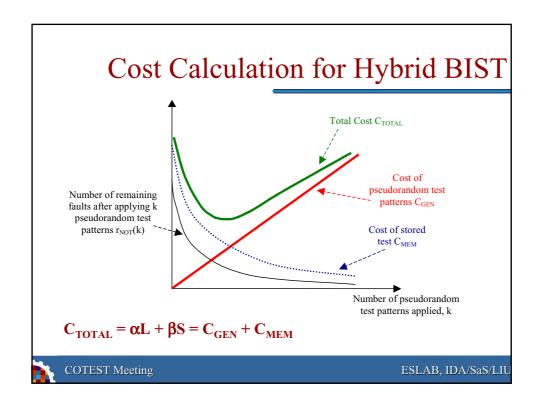

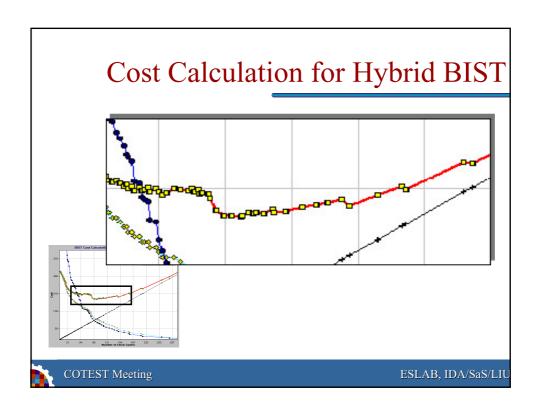

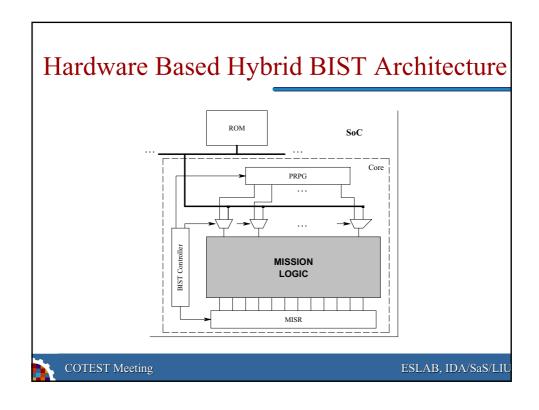

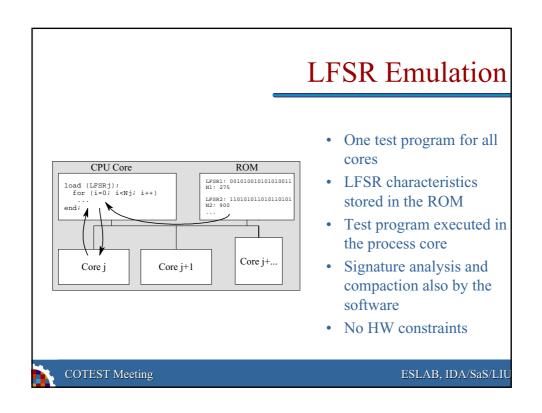

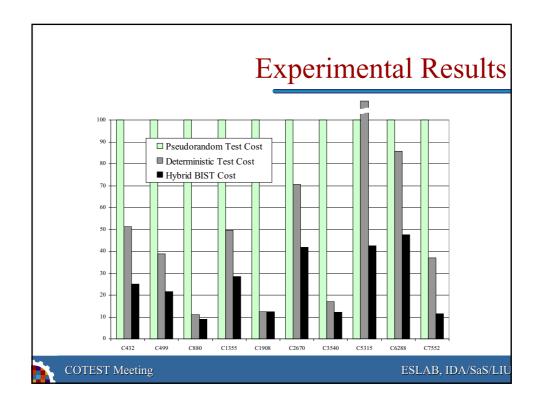

## Insertion of Hybrid BIST

- Our objective:

- Insertion of hybrid BIST structure into a design to improve its testability.

- Optimal balance between pseudorandom and deterministic test patterns in terms of time and memory without losing fault coverage

- To implement the test architecture in software to avoid area overhead, not to affect system performance and to provide possibility for test reconfiguration

COTEST Meeting

### Future Plan

- Fine tuning based on experiments with the hierarchical test generation technique.

- Integration of the two techniques together.

- Demonstration with the benchmark examples identified in the first step of COTEST.

COTEST Meeting