# **Parallelism and Compilers**

Christoph W. Keßler

## Habilitationsschrift

Fachbereich IV Universität Trier

December 13, 2000

ii

## Preface

This thesis describes some of my contributions to several aspects of the large and rapidly growing area of compiling and programming for parallel computer architectures.

It is submitted as habilitation thesis to the Fachbereich IV of the University of Trier, Germany, in partial fulfillment of the pre-requirements for the habilitation examination.

I assure that I have written this thesis myself, and that I have given proper credit to all ideas contributed by other people or taken from the literature, according to my best knowledge. Most of the results described here have been previously published in international refereed journals, conferences, workshops, and in technical reports, and part of the material presented in Chapters 4 and 5 follows my contributions to a recent textbook entitled *Practical PRAM Programming* [B1]. For this reason, this thesis will not be published in its present form. Some ideas and results are, however, new and by now unpublished. New work can be found in each of the main chapters; most of this was developed in parallel to writing this thesis. References to my own publications are marked and listed separately; the complete list of my publications can be found in Appendix D after the general bibliography. A part of the work has been done jointly with other researchers, who are explicitly mentioned in the introduction and in the acknowledgement sections at the end of each main chapter.

The introductory chapter (Chapter 1) gives a personalized view of the main topics discussed in this thesis. In particular, it gives a comprehensive survey of my scientific work and my publications of the last decade.

The main body of this thesis is structured into four main chapters: Chapters 2, 3, 4, and 5. Addressing different aspects of the common area of programming and compiling for parallel architectures, Chapters 2, 3, and 4 are self-contained and may be read independently. Chapter 5 discusses compilation aspects of the parallel programming languages introduced in Chapter 4 and thus depends partially on that chapter.

The appendices contain background material, longer proofs and longer example programs that have been shifted from the main chapters in order to not disrupt the flow of reading.

### Acknowledgments

My scientific work in the last two years, and the work on this thesis in particular, has been supported by a two-year habilitation fellowship of the *Deutsche Forschungsgemeinschaft* (DFG) in 1999 and 2000. From 1997 to 2000, the DFG also supported the SPARAMAT project, which is described in Chapter 3.

From 1995 to 2000, I worked in the group for programming languages and compiler con-

struction, led by Prof. Dr. Helmut Seidl, at the University of Trier. I thank Helmut Seidl for many constructive discussions and fruitful cooperation.

From 1995 to 1998 I was, as an assistant professor, fully involved in the teaching activities (lectures, seminars, exercises, labs) at the computer science department of the University of Trier. I also thank my colleagues and former colleagues in Trier for their friendship and a cooperative working environment. Particular thanks go to the group's secretary, Mrs. Brigitta Weiland.

A major component of my work originated from the SB-PRAM project at Prof. Dr. Wolfgang Paul's group of computer architecture and parallel computers at the computer science department of the University of Saarbrücken, where I did my diploma project in 1989–90 and my PhD project in 1991–94. I thank Wolfgang Paul and my former colleagues in his group for the constructive cooperation. In 1991–94 my PhD project was supported by a three-year PhD fellowship of the DFG in the Graduiertenkolleg Informatik at the University of Saarbrücken. In 1994 I was involved in the SB-PRAM project work and started work on the design and implementation of the PRAM programming language Fork, which I continued when I started to work in Trier in 1995.

Finally, I thank my wife Susanne, for her continuous love, support of my work, and for tolerating my commuting to Trier during the last six years. I also thank all my friends and my family, in particular my parents.

In the end of 2000, I will leave the University of Trier and join the University of Linköping, Sweden, as an associate professor in the computer science department. In this context, I see this monograph, beyond its role as habilitation thesis, as a final documentation of my scientific work of the last years, which was mostly done while I was affiliated with the University of Trier.

Trier, December 13, 2000

CHRISTOPH KESSLER

# Contents

| 1 | Intr | oductio | n and Overview                                                 | 1  |

|---|------|---------|----------------------------------------------------------------|----|

|   | 1.1  | Instruc | ction Scheduling                                               | 3  |

|   | 1.2  | Autom   | natic Program Comprehension and Automatic Parallelization      | 5  |

|   | 1.3  | Design  | n and Implementation of Parallel Programming Languages         | 7  |

| 2 | Inst | ruction | Scheduling                                                     | 13 |

|   | 2.1  | Introdu | uction                                                         | 13 |

|   |      | 2.1.1   | Processor Model                                                | 13 |

|   |      | 2.1.2   | Instruction Selection                                          | 15 |

|   |      | 2.1.3   | Instruction Scheduling                                         | 16 |

|   |      | 2.1.4   | Register Allocation                                            | 19 |

|   |      | 2.1.5   | The Phase-Ordering Problem                                     | 20 |

|   |      | 2.1.6   | Overview of the Chapter                                        | 21 |

|   | 2.2  | Basic   | Definitions                                                    | 22 |

|   |      | 2.2.1   | DAGs and Schedules                                             | 22 |

|   |      | 2.2.2   | Register Allocation for Basic Block Schedules                  | 23 |

|   |      | 2.2.3   | Optimal Register Allocation for a Given Schedule               | 24 |

|   | 2.3  | Contig  | guous Schedules                                                | 26 |

|   |      | 2.3.1   | Computing Space-Optimal Schedules for Trees                    | 27 |

|   |      | 2.3.2   | Enumerating Contiguous Schedules for DAGs                      | 27 |

|   |      | 2.3.3   | Further Reducing the Number of Schedules                       | 32 |

|   |      | 2.3.4   | Splitting the DAG into Subtrees                                | 34 |

|   |      | 2.3.5   | Evaluating Trees with Import and Export Nodes                  | 35 |

|   |      | 2.3.6   | Experimental Results                                           | 37 |

|   |      | 2.3.7   | Summary of the Algorithms for Contiguous Schedules             | 39 |

|   |      | 2.3.8   | Weaknesses of Contiguous Schedules                             | 39 |

|   | 2.4  | Comp    | uting Optimal Schedules                                        | 40 |

|   |      | 2.4.1   | Enumerating Schedules                                          | 40 |

|   |      | 2.4.2   | Improvement                                                    | 46 |

|   |      | 2.4.3   | Parallelization                                                | 47 |

|   |      | 2.4.4   | Experimental Results                                           | 48 |

|   |      | 2.4.5   | Simultaneous Optimization of Register Space and Execution Time | 49 |

|   |      | 2.4.6   | Time–Space Profiles                                            | 55 |

|   |      | 2.4.7   | A Randomized Heuristic                                         | 57 |

## CONTENTS

|   |      | 2.4.8         | Heuristic Pruning of the Selection DAG                     | 9 |

|---|------|---------------|------------------------------------------------------------|---|

|   | 2.5  | Extens        | ion for Optimal Scheduling of Spill Code                   | 3 |

|   | 2.6  | Extens        | ion for Partial Recomputations                             | 6 |

|   |      | 2.6.1         | Recomputing Single DAG Nodes                               | 6 |

|   |      | 2.6.2         |                                                            | 6 |

|   | 2.7  | Related       |                                                            | 7 |

|   |      | 2.7.1         |                                                            | 7 |

|   |      | 2.7.2         |                                                            | 9 |

|   | 2.8  | Summa         | ary $\ldots$ $\ldots$ $7$                                  | 1 |

| 3 | Auto | omatic (      | Comprehension and Parallelization of Sparse Matrix Codes 7 | 5 |

|   | 3.1  |               |                                                            | 5 |

|   |      | 3.1.1         |                                                            | 6 |

|   |      | 3.1.2         |                                                            | 7 |

|   |      | 3.1.3         | • • • •                                                    | 7 |

|   |      | 3.1.4         |                                                            | 8 |

|   | 3.2  | Vectors       | 1                                                          | 8 |

|   |      | 3.2.1         |                                                            | 8 |

|   |      | 3.2.2         |                                                            | 9 |

|   | 3.3  | Concep        | -                                                          | 4 |

|   |      | 3.3.1         | -                                                          | 6 |

|   |      | 3.3.2         | Exception Slots                                            | 0 |

|   | 3.4  | Specul        | ative Concept Recognition                                  | 1 |

|   |      | 3.4.1         |                                                            | 1 |

|   |      | 3.4.2         |                                                            | 3 |

|   |      | 3.4.3         | Speculative Loop Distribution                              | 5 |

|   |      | 3.4.4         | Preservation and Propagation of Format Properties          | 6 |

|   |      | 3.4.5         | Placing Runtime Tests                                      | 6 |

|   |      | 3.4.6         | A Parallel Algorithm for the Monotonicity Tests            | 0 |

|   |      | 3.4.7         | A Parallel Algorithm for the Injectivity Tests             | 0 |

|   | 3.5  | <b>SPAR</b> A | AMAT Implementation                                        | 1 |

|   |      | 3.5.1         | Static Concept Matching                                    | 2 |

|   |      | 3.5.2         | Delayed Format Resolution                                  | 3 |

|   |      | 3.5.3         | Descriptors                                                | 3 |

|   | 3.6  | The Co        | oncept Specification Language CSL                          | 5 |

|   |      | 3.6.1         | Header Specification                                       | 6 |

|   |      | 3.6.2         | Concept Instance Lists                                     | 7 |

|   |      | 3.6.3         | Selector Expressions                                       | 7 |

|   |      | 3.6.4         | Specification of Templates for Vertical Matching 10        | 9 |

|   |      | 3.6.5         | Specification of Templates for Horizontal Matching         | 0 |

|   |      | 3.6.6         | Further Features of CSL                                    | 3 |

|   | 3.7  | Related       | d work                                                     | 6 |

|   | 3.8  | Future        | Work                                                       | 7 |

|   |      | 3.8.1         | More Concepts, Templates, Example Programs                 | 7 |

|   |      | 3.8.2    | Interactive Program Comprehension                         |   | 117 |

|---|------|----------|-----------------------------------------------------------|---|-----|

|   |      | 3.8.3    | Application to Automatic Parallelization                  |   | 117 |

|   |      | 3.8.4    | Applicability to Other Problem Domains                    |   | 117 |

|   | 3.9  | Summa    | ary                                                       | • | 118 |

| 4 | Desi | gn of Pa | arallel Programming Languages                             |   | 119 |

|   | 4.1  | The SP   | PMD Processor Group Concept                               |   | 120 |

|   | 4.2  | Fork L   | anguage Design                                            |   | 122 |

|   |      | 4.2.1    | The PRAM model                                            |   | 122 |

|   |      | 4.2.2    | Fork Language Design Principles                           |   | 124 |

|   |      | 4.2.3    | Shared and Private Variables                              |   | 127 |

|   |      | 4.2.4    | Expressions                                               |   | 129 |

|   |      | 4.2.5    | Synchronous and Asynchronous Regions                      |   | 131 |

|   |      | 4.2.6    | Synchronous Execution and the Group Concept               |   |     |

|   |      | 4.2.7    | Pointers and Heaps                                        |   | 143 |

|   |      | 4.2.8    | Exploring the Asynchronous Mode                           |   | 146 |

|   |      | 4.2.9    | The join Statement                                        |   | 155 |

|   |      | 4.2.10   | Programming Style and Caveats                             |   | 162 |

|   |      | 4.2.11   | Graphical Trace File Visualization                        |   | 167 |

|   |      | 4.2.12   | The History of Fork                                       |   |     |

|   |      | 4.2.13   | The Future of <b>Fork</b>                                 |   | 177 |

|   | 4.3  | A Plea   | for Structured Parallel Programming in Fork               |   | 178 |

|   |      | 4.3.1    | Data Parallelism                                          |   | 180 |

|   |      | 4.3.2    | Nestable Skeleton Functions                               |   | 182 |

|   |      | 4.3.3    | Reductions                                                |   | 184 |

|   |      | 4.3.4    | Composing Skeleton Functions                              |   | 188 |

|   | 4.4  | ForkLi   | ght Language Design                                       |   | 189 |

|   |      | 4.4.1    | SPMD Execution                                            |   | 191 |

|   |      | 4.4.2    | Variables and Expressions                                 |   | 191 |

|   |      | 4.4.3    | Control-Synchronous and Asynchronous Program Regions      |   | 192 |

|   |      | 4.4.4    | Groups and Control Synchronicity in ForkLight             | • | 193 |

|   |      | 4.4.5    | Pointers and Heaps                                        |   |     |

|   |      | 4.4.6    | Standard Atomic Operations                                |   |     |

|   |      | 4.4.7    | Discussion: Support of Strict Synchronicity in ForkLight? |   | 197 |

|   |      | 4.4.8    | Example: Parallel Mergesort                               |   | 200 |

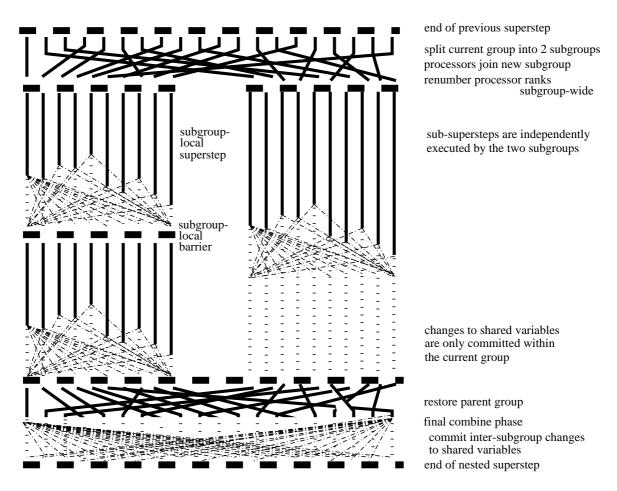

|   | 4.5  | NestS    | tep Language Design                                       |   | 201 |

|   |      | 4.5.1    | The BSP Model                                             |   | 201 |

|   |      | 4.5.2    | NestStep Language Design Principles                       |   | 203 |

|   |      | 4.5.3    | Supersteps and Nested Supersteps                          |   | 204 |

|   |      | 4.5.4    | Supersteps and Control Flow                               | • | 206 |

|   |      | 4.5.5    | Sharing Variables, Arrays, and Objects                    |   | 209 |

|   |      | 4.5.6    | Distributed Shared Arrays                                 |   | 214 |

|   |      | 4.5.7    | Pointers                                                  | • | 218 |

|   | 4.6  | Other I  | Parallel Programming Languages                            |   | 220 |

|   |     | 4.6.1   | MIMD Message Passing Environments                       | 221 |

|---|-----|---------|---------------------------------------------------------|-----|

|   |     | 4.6.2   | MIMD Asynchronous Shared Memory Environments            |     |

|   |     | 4.6.3   | Fork-Join-Style Shared Memory MIMD Languages            |     |

|   |     | 4.6.4   | SPMD-Style Asynchronous Shared Memory MIMD Languages    |     |

|   |     | 4.6.5   | SIMD and Dataparallel Programming Languages             |     |

|   |     | 4.6.6   | PRAM Languages                                          |     |

|   |     | 4.6.7   | BSP Languages                                           |     |

|   |     | 4.6.8   | Integration of Task Parallelism and Data Parallelism    |     |

|   |     | 4.6.9   | Skeleton Languages                                      |     |

|   | 4.7 | Summa   | ary                                                     |     |

| 5 | Imp | lementa | tion of Parallel Programming Languages                  | 231 |

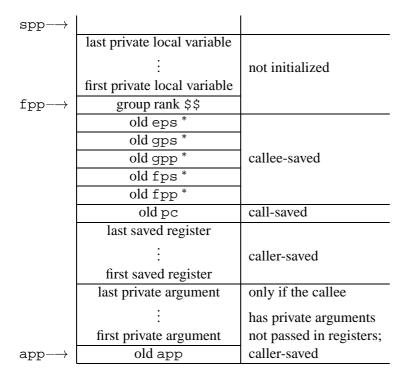

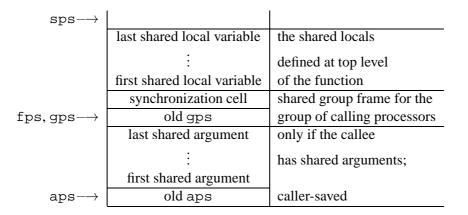

|   | 5.1 |         | ling Fork for the SB-PRAM                               | 231 |

|   |     | 5.1.1   | Extensions to the C Compiler Phases and Data Structures |     |

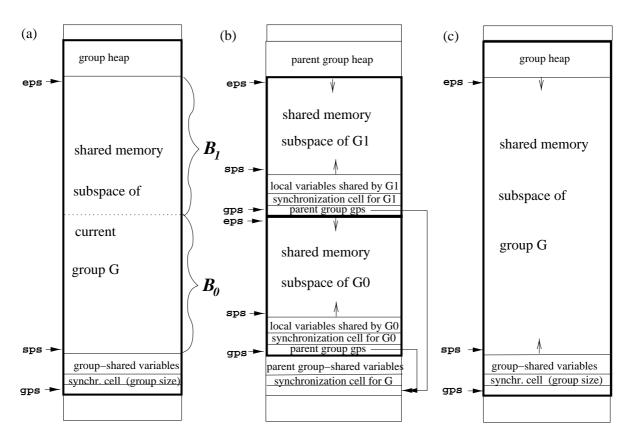

|   |     | 5.1.2   | Shared Memory Organization and Frame Layout             |     |

|   |     | 5.1.3   | Translation of start and join                           |     |

|   |     | 5.1.4   | Translation of the Private if Statement                 |     |

|   |     | 5.1.5   | Groups and Control Flow                                 |     |

|   |     | 5.1.6   | Accessing Shared Local Variables                        |     |

|   |     | 5.1.7   | Runtime Overheads and Optimizations                     |     |

|   |     | 5.1.8   | Implementation of Barrier Synchronization               | 241 |

|   |     | 5.1.9   | Implementation of the Simple Lock                       | 242 |

|   |     | 5.1.10  | Implementation of the Fair Lock                         | 242 |

|   |     | 5.1.11  | Implementation of the Reader–Writer Lock                |     |

|   |     | 5.1.12  | Implementation of the Reader–Writer–Deletor Lock        | 246 |

|   |     | 5.1.13  | Implementation of the trv Trace Visualization Tool      | 247 |

|   | 5.2 | Compi   | ling Fork for Other Parallel Architectures              | 250 |

|   |     | 5.2.1   | Emulating Additional PRAM Processors in Software        |     |

|   |     | 5.2.2   | Compiling for Asynchronous Shared Memory Architectures  | 259 |

|   |     | 5.2.3   | Compiling for Distributed Memory Architectures          | 263 |

|   | 5.3 | Compi   | ling ForkLight for an Asynchronous PRAM                 | 264 |

|   |     | 5.3.1   | Translation of a Function Call                          |     |

|   |     | 5.3.2   | Translation of the fork Statement                       | 266 |

|   |     | 5.3.3   | Accessing Local Shared Variables                        | 267 |

|   |     | 5.3.4   | Optimization of Barriers                                | 267 |

|   |     | 5.3.5   | Virtual Processing                                      | 268 |

|   |     | 5.3.6   | Translation to OpenMP                                   | 268 |

|   |     | 5.3.7   | Performance Results                                     | 269 |

|   | 5.4 | Compi   | ling NestStep to a Distributed Memory System            | 271 |

|   |     | 5.4.1   | Group Objects and Group Splitting                       | 271 |

|   |     | 5.4.2   | Naming Schemes for Addressing Shared Variables          | 272 |

|   |     | 5.4.3   | Values and Array Objects                                | 273 |

|   |     | 5.4.4   | Shared Variables                                        | 273 |

|   |     | 5.4.5   | Combine Items                                           | 274 |

### CONTENTS

|      | 5.4.6                                            | Serialization of Combine Lists                                                                                                                              | . 274                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

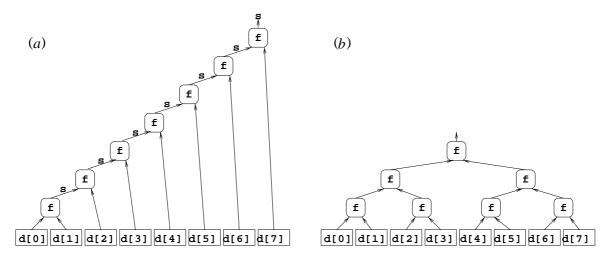

|      | 5.4.7                                            | Combine Trees                                                                                                                                               | . 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 5.4.8                                            | Combining                                                                                                                                                   | . 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 5.4.9                                            | Bulk Mirroring and Updating of Distributed Arrays                                                                                                           | . 279                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 5.4.10                                           | Optimizations                                                                                                                                               | . 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 5.4.11                                           | Prototype Implementation                                                                                                                                    | 281                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.5  | Summa                                            | ary                                                                                                                                                         | . 283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Supp | olement                                          | ary Material to Chapter 2                                                                                                                                   | 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A.1  | Proof o                                          | of the optimality of <i>labelfs2</i>                                                                                                                        | . 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Sup  | olement                                          | ary Material to Chapter 3                                                                                                                                   | 289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B.1  | An Exa                                           | imple for SPARAMAT Analysis                                                                                                                                 | . 289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B.2  | Examp                                            | le for the STRIP Concept                                                                                                                                    | . 290                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Supp | olement                                          | ary Material to Chapters 4 and 5                                                                                                                            | 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                  | V I                                                                                                                                                         | . 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| List | of Publi                                         | ications                                                                                                                                                    | 315                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | Supp<br>A.1<br>Supp<br>B.1<br>B.2<br>Supp<br>C.1 | 5.4.7<br>5.4.8<br>5.4.9<br>5.4.10<br>5.4.11<br>5.5 Summa<br>Supplement<br>A.1 Proof of<br>Supplement<br>B.1 An Exa<br>B.2 Examp<br>Supplement<br>C.1 NestSi | <ul> <li>5.4.7 Combine Trees</li> <li>5.4.8 Combining</li> <li>5.4.8 Combining and Updating of Distributed Arrays</li> <li>5.4.9 Bulk Mirroring and Updating of Distributed Arrays</li> <li>5.4.10 Optimizations</li> <li>5.4.11 Prototype Implementation</li> <li>5.5 Summary</li> <li>5.5 Summary</li> <li>5.5 Supplementary Material to Chapter 2</li> <li>A.1 Proof of the optimality of <i>labelfs2</i></li> <li>Supplementary Material to Chapter 3</li> <li>B.1 An Example for SPARAMAT Analysis</li> <li>B.2 Example for the STRIP Concept</li> <li>Supplementary Material to Chapters 4 and 5</li> </ul> |

### CONTENTS

# Chapter 1

## **Introduction and Overview**

Today's computer architectures increasingly rely on parallel execution to keep pace with the demand for computational power. For instance, for further improvements in single-processor speed it becomes more and more critical to exploit instruction-level parallelism because the "automatic" improvements due to higher integration in chip technology will soon approach their physical limits. At the upper end of the performance scale, the supercomputer industry has recognized that self-designing sophisticated special purpose hardware is too time-consuming, while using off-the-shelf components reduces development costs and allows to participate in the advances of microprocessor performance. Hence, most modern supercomputers consist of hundreds or thousands of standard processors that are connected by an interconnection network to allow for synchronizing and exchanging data. In the middle of the spectrum, today's advanced workstations and servers usually have multiple processors as well, which are connected by a shared memory. Hence, the opportunities to speed up computations by exploiting parallelism become ubiquitous.

On the other hand, the problem of writing efficient code for parallel computers or compiling for such architectures is notoriously difficult, such that there emerged the so-called "parallel software crisis". Modern microprocessor technology has even decided to solve part of this problem in hardware by analyzing data and control dependencies at run time and dispatching instructions to pipelined and parallel functional units on-line, although this automatic reordering at run time is only applicable within the limited scope of a small window containing a few subsequent instructions in the code. Nevertheless, the compiler has a much larger insight into the program and can, by an off-line algorithm for suitably ordering the instructions in the generated machine program, relax the limited scope problem of the runtime scheduler, such that it can issue more instructions in the same cycle and use registers economically. Hence, the main task of exploiting parallelism remains with the programmer and the compiler.

Parallelism can be exploited by compilers at several different levels. In some cases, the task of determining opportunities for concurrent execution can be partially automatized.

For instance, when compiling for modern superscalar processors, the code generation phase of the compiler should be aware of the existence of multiple functional units when determining the order of instructions in the target program, such that independent instructions may be executed concurrently. This allows to exploit fine-grain parallelism at the instruction level. Loops in the source program often exhibit a large potential for parallel execution. Furthermore their simple control structure allows for a condensed analysis of parallelizability. There exists a well-known theory of analyzing data dependences among the iterations of a loop nest, for transforming loop nests, for detecting parallelizable loops, and for scheduling their iterations for execution on different processors of a parallel computer. Nevertheless, the automatic parallelization technology for loops is bound to the sequential control structure of the source program. On the other hand, sophisticated parallel algorithms have been devised for various parallel architectures and for many problems. In general, these can not be derived from corresponding sequential algorithms and programs just by applying simple program transformations. For the user of a parallel computer, there remain thus two possibilities to exploit this rich potential of parallel algorithms.

The first approach is to make automatic parallelization more intelligent. Although the general problem of automatically understanding the meaning of a program is undecidable, it is, given sufficient application-domain-specific information, possible to identify computations on a local level and replace them by a parallel algorithm with the same semantics. This allows to go beyond the sequential program's control structure, but assumes a certain homogeneity of the application domain, which is necessary to avoid a combinatorial explosion of the different program concepts to be recognized and replaced. This condition is fulfilled e.g. in the domain of numerical matrix computations, while it is hardly met in the area of nonnumerical or highly irregular computations.

The second approach imposes the task of specifying the parallelism to be exploited on the programmer—albeit at a higher level than that offered by the default programming interface to the parallel hardware. For this purpose, explicitly parallel programming languages are required. Such a language should offer more means for expressing parallelism than just a parallel loop construct, because there are, especially in nonnumerical and irregular problems, many flavours of parallelism that cannot be expressed easily using parallel loops. Nevertheless, the compiler is still responsible for efficiently mapping the parallel activities specified by the programmer to the parallel target machine by exploiting the features of the parallel architecture.

In the last years I have done research in all of these facets of compiling for parallel architectures. The main part of my scientific work can thus be subdivided into three main subjects:

- 1. *Instruction scheduling* for RISC, superscalar, and vector processors, with the goal of minimizing the execution time and / or the number of registers used.

- 2. *Automatic Program Comprehension*: Identifying computation and data structure concepts in numerical codes (idiom recognition, tree pattern matching) with the goal of replacing them by suitable parallel equivalents.

- 3. Design, Implementation, and Application of Parallel Programming Languages, providing practical programming environments for the—up to now—mainly theoreticallybased machine models PRAM, Asynchronous PRAM, and BSP.

The remainder of this chapter gives an informal introduction to these issues and provides a summary of my own contributions to the topics discussed in this thesis. A more formal and detailed presentation of selected work follows in the subsequent chapters of this book.

#### 1.1. Instruction Scheduling

In the following, citations like [J6] (refereed journal paper), [C18] (refereed conference paper), [I7] (invited conference / workshop paper), [D1] (thesis) and [M11] (other publication like technical reports) refer to the list of my own publications at the end of this book, starting with page 315. All other citations refer to the bibliography.

## 1.1 Instruction Scheduling

Since 1989, when I started with research for my diploma thesis [D1], I worked on problems in code generation for RISC, superscalar, and vector processors.

Instruction scheduling is one of the core problems to be solved in the code generation phase of a compiler The goal is to minimize the number of registers used and / or the number of machine cycles taken by the execution of the schedule on the target machine. Usually, the instructions are not generic any more, i.e. they are already specific to the target processor, but they still operate on symbolic registers.

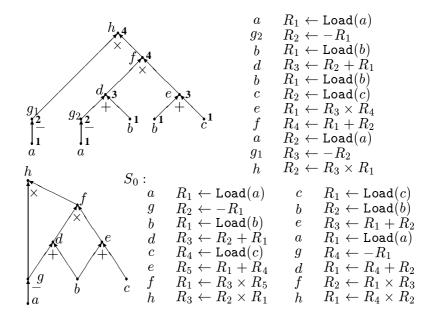

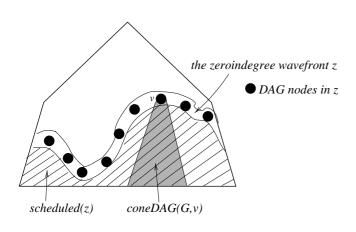

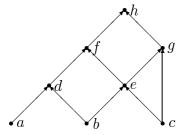

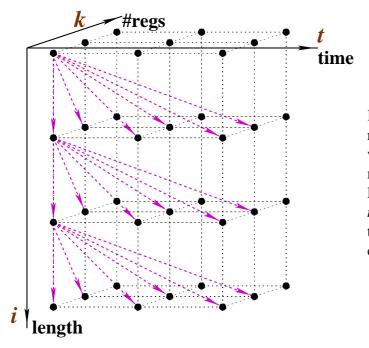

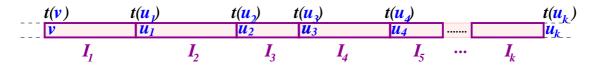

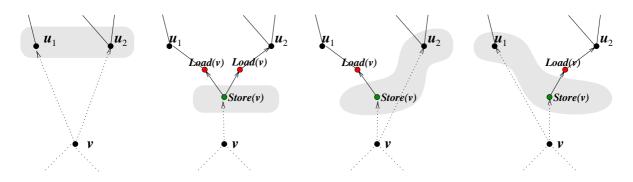

We consider the problem of local instruction scheduling, that is, the scope of optimization is a basic block<sup>1</sup> The data dependences of a basic block form a directed acyclic graph (DAG), where the nodes represent the instructions and the values computed by them, and the edges imply precedence relations among the instructions. Most edges are due to value flow dependences, that is, the value generated by the source instruction is used as an operand by the target instruction. A (*list*) schedule of the basic block resp. DAG is a total order of the instructions that does not conflict with the partial order given by the DAG edges. By adding the time and space constraints of the target processor (e.g., delayed instructions or a limited number of available registers), the list schedule usually determines a fixed, unique execution scenario for the instructions of the DAG. We will discuss some exceptions later.

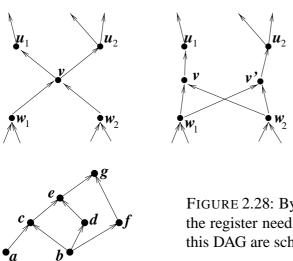

A *register allocation* for a given (list) schedule is a mapping of the DAG nodes to the available processor registers, such that each value computed by an instruction into a register remains in that register and is not overwritten till its last use by a parent instruction. The total number of registers used is the *register need* of the allocation. A register allocation is called *optimal* for the given schedule if there is no other register allocation for that schedule that needs fewer registers. An optimal register allocation can be computed in a greedy manner in linear time.

A *time slot allocation* (or *time schedule*) for a given (list) schedule is a mapping of the instructions to time slots 1,2,... that indicate the point in time where the execution of the corresponding instruction will start on the target processor. An instruction must not start unless all its direct predecessor instructions in the DAG have completed their computation and have written their result values into registers. The *execution time* of a schedule is the time slot where all instructions in that schedule have completed their execution. A time slot allocation is *optimal* for the given list schedule if there is no other time slot allocation that has a smaller execution time. An optimal time slot allocation for the given list schedule can be computed in a greedy manner in linear time, even for superscalar processors with out-of-order execution if the runtime scheduling strategy of the target processor's dispatcher is known at compile time.

<sup>&</sup>lt;sup>1</sup>A basic block is a sequence of instructions that contains no branch and no join of control flow.

A list schedule of a DAG is called *space-optimal* if there is no other list schedule for the same DAG that yields an optimal register allocation needing less registers than this schedule.

A list schedule of a DAG is called *time-optimal* if there is no other list schedule for the same DAG that yields an optimal time slot allocation needing less machine cycles than this schedule.

If the DAG has a special structure and the target processor meets certain conditions, several scheduling problems can be solved in polynomial time. For instance, if the DAG is a *tree*, a space-optimal list schedule for a single-issue RISC processor can be computed in linear time by the labeling algorithm of Sethi and Ullman [SU70], which is summarized in Section 2.3.1. For a general DAG the problem of computing a space-optimal schedule is NP-complete [Set75]. In the same way, computing a time-optimal schedule for a DAG and a processor with delayed instructions or parallel functional units is NP-complete. A thorough overview of the relevant literature on instruction scheduling will be given in Chapter 2, especially in Section 2.7.

When I started working on computing space-optimal schedules, I first developed a randomized linear-time heuristic for computing a schedule with low register need [C1], which is described in Section 2.3.2. By experiments with many randomly generated DAGs I showed that, compared to a single randomly generated schedule, the register need can be reduced by 30% on the average by this heuristic. However, no guarantee is given how far away is the register need of the reported solution from the actual optimum. Moreover, no method was known at this time to compute the optimum at all.

The heuristic [C1] was implemented in a Vector–Pascal compiler [FOP<sup>+</sup>92] for the vector processor SPARK2 [FOP<sup>+</sup>92] built at the institute for parallel computer architecture of Prof. Dr. W.J. Paul at the University of Saarbrücken. The SPARK2 has a vector register file of 4096 words that can be partitioned by the programmer into vector registers of arbitrary size, which are addressed by pointer arithmetics. For vector basic blocks derived from Vector-Pascal programs, I developed a method [C2] that determines, for the computed schedule, the optimal vector register length (which implies the number of available vector registers) and, if necessary, decides about spilling some register contents to the main memory, such that the total execution time on the SPARK2 is minimized.

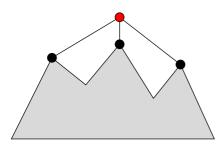

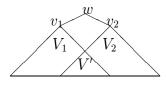

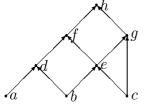

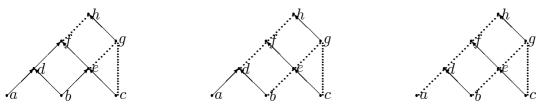

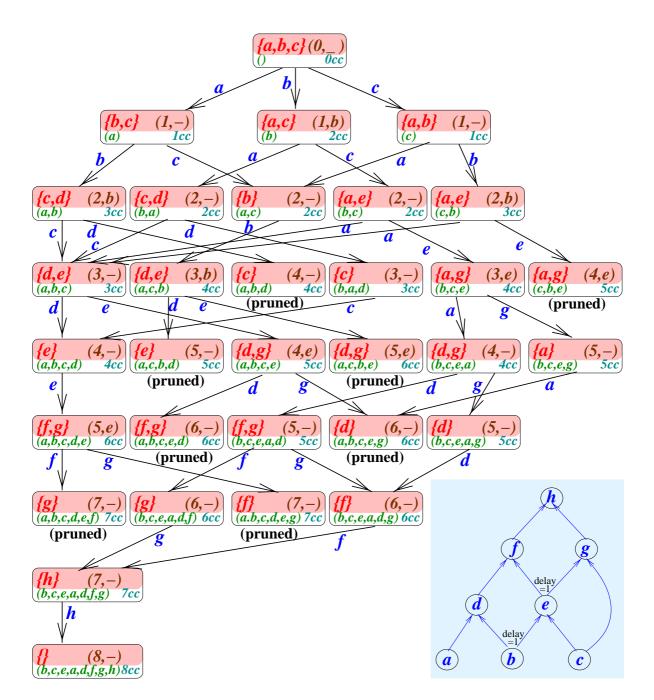

As discussed above, computing space-optimal schedules for DAGs is hard. Trying to avoid the complexity of the general problem, I restricted the scope of optimization to the so-called *contiguous* schedules. A contiguous schedule is a schedule that can be obtained by a postorder traversal of the DAG. Hence, the number of contiguous schedules for a DAG with n nodes is bound by  $O(2^n)$ , while the number of (all) schedules is bound by O(n!). Together with Prof. Dr. Thomas Rauber I developed an algorithm [C3,C7,J1] that computes space-optimal contiguous schedules for DAGs. The algorithm (see Section 2.3.2) enumerates the search space of different postorder traversals of the DAG and applies sophisticated pruning techniques that avoid the generation of duplicate or symmetric schedules and exploit tree structures of the remaining DAG nodes not yet traversed, which are handled by a modification of the Sethi–Ullman labeling algorithm. On the average, this algorithm reduces the complexity of the problem to about  $O(2^{n/2})$ . In practice, this is good enough to handle basic blocks with up to 80 instructions within acceptable time. Note that nearly all basic blocks that occur in real programs are much smaller.

#### 1.2. Automatic Program Comprehension and Automatic Parallelization

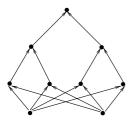

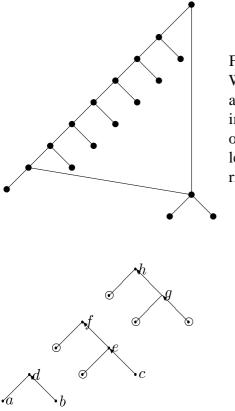

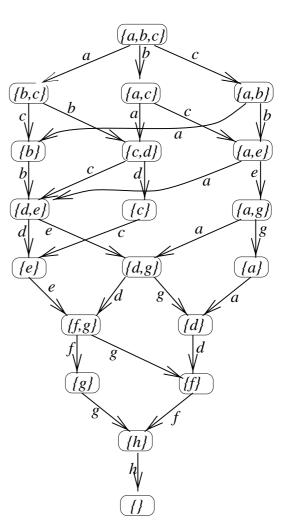

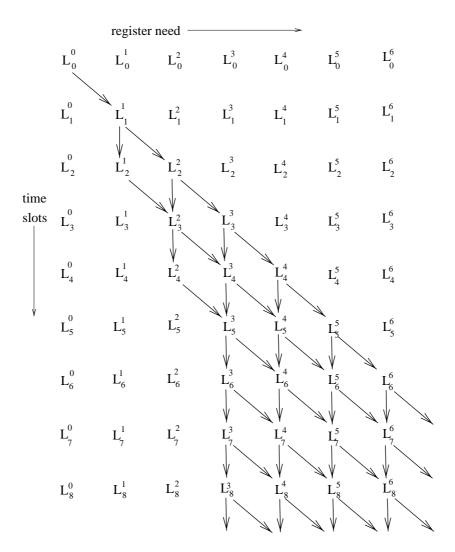

The restriction to contiguous schedules means nevertheless that the described algorithm could find only suboptimal solutions, namely if no contiguous schedule is an optimal schedule. In order to be able to determine an optimal solution, I developed an algorithm [C12,J4] that solves the problem of determining a space-optimal schedule. As described in Section 2.4, the algorithm traverses the solution space by generating (conceptually) all topological orderings of the nodes of the DAG bottom-up by a dynamic-programming method. The algorithm exploits the fact that prefixes of schedules that contain the same subset of DAG nodes can be handled uniformly with respect to time and register constraints, and hence can be summarized as a single subsolution for which only one optimal subschedule needs to be stored. By classifying the subsolutions according to schedule length, register need, and execution time, the space of subsolutions can be traversed in a way that is most suitable for the intended primary optimization goal. The user can thus select either space or time optimization as the primary and the other one as the secondary optimization direction. It is also possible to specify a combined optimization criterion. In this way, the subspace implied by the most promising subsolutions can be explored first, and hence the algorithm defers the combinatorial explosion of the enumeration process to a later point of time that is, ideally, never reached because an optimum solution has been found meanwhile. Furthermore, the algorithm allows to exploit massive parallelism. The implementation showed that the algorithm is practical for basic blocks with up to 40 instructions, a class that contains nearly all basic blocks occurring in application programs. Hence, this method could be used in highly optimizing compilers. It should be noted that, for correctness only, any schedule is acceptable for code generation, and hence these expensive optimizations need only be applied in the final, optimizing compilation of the application.

Beyond describing these previously published results, Chapter 2 contains some by now unpublished material. For a faster optimization of large basic blocks I present and evaluate two heuristics. Then, I discuss how the performance of the dynamic programming method for time and time-space optimizations can be further improved by the novel concept of time-space profiles. Moreover, I discuss the extensibility of my enumeration algorithm for situations where spilling of some register contents to main memory or recomputations of some DAG nodes are permitted. I conclude with an extensive survey of related work.

This work will be continued in the near future in a new research project that is funded by the Ceniit programme of the University of Linköping.

## **1.2** Automatic Program Comprehension and Automatic Parallelization

*Program comprehension* is the process of discovering abstract concepts in the source code, e.g. the identification of data structures and (sub-)algorithms used. In its generality, this problem is undecidable, but, given some knowledge of the program's application domain, automatic understanding of programs is possible at least on a local level. In this case, understanding becomes a recognition process: it can be sketched as matching a given source program against a set of known programming concepts.

A number of problems have to be dealt with when facing automated recognition of al-

gorithmic concepts [Wil90]: The most important ones are *syntactic variation*, *algorithmic variation* (a concept can be implemented in many different ways), *delocalization* (the implementation of a concept may be spread throughout the code), and *overlapping implementations* (portions of a program may be part of more than one concept instance).

Automatic program comprehension systems, working without user interaction, are mainly used for two purposes: to support software maintenance [RW90, HN90, KNS92, KNE93], e.g. for the automatic documentation of code, and to support automatically parallelizing compilers. Several methods for both areas have been proposed within the last years, and some (mostly experimental) systems have been built. Here we focus on the second issue.

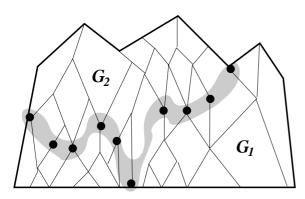

Automated program recognition can play an important role in enhancing the capabilities of existing parallelizing compilers [BS87, Bos88, Cal91, PP91, RF93, SW93, PP94, PE95], in particular for target machines with a distributed memory [J2]. For instance, replacement of recognized sequential code by suitable parallel algorithms represents an aggressive code transformation which is not bound to the sequential program's control structure. Moreover, the acquired knowledge enables automatic selection of sequences of optimizing transformations, supports automatic array alignment and distribution, and improves accuracy and speed of performance prediction.

The application domain considered mainly consists of numerical computations, in particular linear algebra and PDE codes. Domain analysis done in my PhD thesis [D2] for the area of regular numerical computations on vectors and dense matrices has shown that the size of the set of concepts typically occurring in such codes remains reasonably small. But also in non-numerical or irregular numerical fields, recognition of algorithmic concepts in the code can drive the selection of suitable parallelization strategies ([DI94], [C15]).

When starting to do research for my PhD project, I discovered that concept recognition techniques may be well suited for numerical codes operating on dense matrices, because these exhibit a certain homegeneity of data structures (vectors, matrices) and algorithms and programming idioms used in Fortran source codes. In fact, I found by analyzing a representative set of Fortran77 programs that a rather small set of 150 concepts with only a few recognition rules per concept is sufficient to cover large parts of these programs, in particular for the time-consuming inner loops that are important to be parallelized.

Next, I developed and implemented an algorithm similar to bottom-up tree pattern matching for the automatic identification of these concepts [D2,I1,I2,C4,C5,J2]. Recognized code parts, represented as a subtree in the treelike intermediate representation of the program, are replaced by a summary node (concept instance) that contains all information about the identified concept occurrence, i.e. the function computed by this code part, together with a list of program objects that occur as parameters of this function. Nevertheless the summary node abstracts from all the details *how* this function is computed in the source program. Finally, it is more or less straightforward to generate calls to parallel library functions from the summary nodes. The integration of the concept recognizer in a large automatic parallelization system for distributed memory target machines, called PARAMAT, is described in [D2,C6,J2]. A front end and the concept recognizer of PARAMAT have been implemented; an implementation of the overall PARAMAT system was not possible because I was assigned other work after finishing my PhD thesis, and a corresponding project proposal was not accepted by DFG. Nevertheless, a simple back end [I2] exists for the shared-memory parallel computer SB-PRAM built at the institute of parallel computer architecture of the University of Saarbrücken.

There is only few related work on automatic program comprehension for automatic parallelization that has actually been implemented. One promising approach, although more targeted to interactive parallelization instead of code replacement, has been presented by Prof. Dr. Beniamino di Martino [DI94]. In a joint work [C9,M9,J6] we analyzed the fundamental differences and similarities of our approaches and proposed a method to combine them.

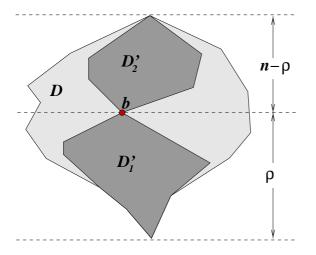

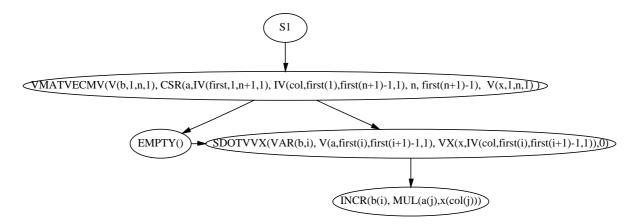

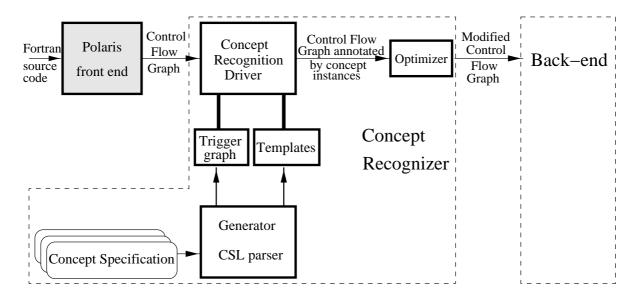

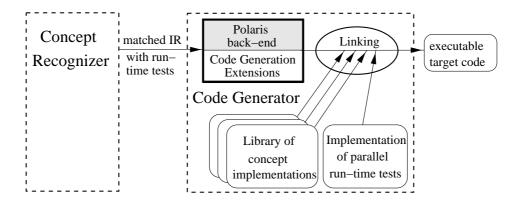

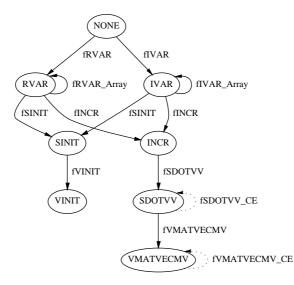

For a project proposal in 1996 I started to investigate the applicability of the PARAMAT approach to computations on sparse matrices. Sparse matrix codes lead to irregular numerical programs that are hard to parallelize automatically by today's parallelizing compiler technology, because part of the data dependency information required for parallelization is not known until run time. In a feasibility study [I5,C15] I discussed the potential and the challenges of a *speculative concept recognition* where a part of the identification of a concept may be deferred to run time tests. The placement of the run time tests can be optimized by a data flow framework. Out of these ideas grew the SPARAMAT project at the University of Trier, which was funded by the DFG from 1997 to 2000. SPARAMAT defines a special concept specification language CSL [C17,M11]. A generator parses a set of CSL specifications and constructs from these a hierarchically working concept recognizer (a C++ program), which is then able to process sequential source programs (Fortran77 in our implementation).

The foundations and the implementation of the SPARAMAT system are described in Section 3.

## **1.3 Design and Implementation of Parallel Programming** Languages

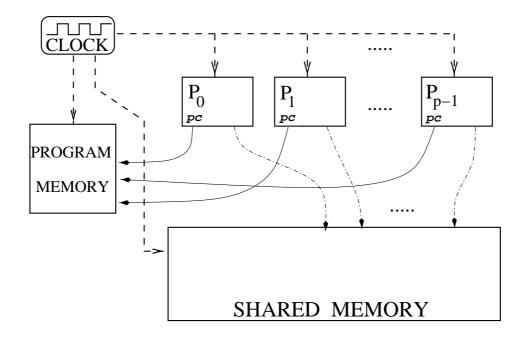

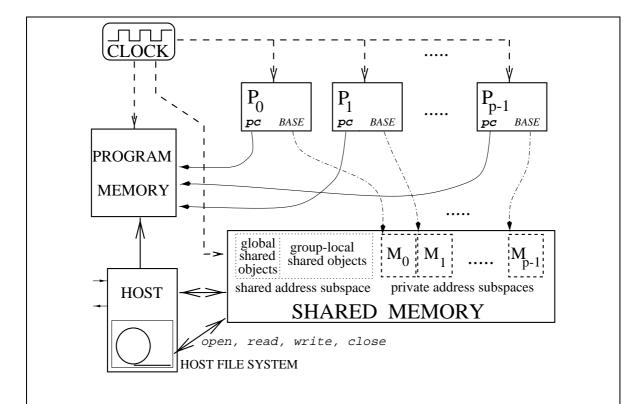

The PRAM<sup>2</sup> is a popular programming model in the theory of parallel algorithms. It denotes a massively parallel synchronous MIMD<sup>3</sup> computer with a sequentially consistent shared memory and uniform memory access time. Although widely regarded as being highly unrealistic, a massively parallel realization of a Combine CRCW PRAM, the strongest PRAM variant<sup>4</sup> known in theory, has been designed and built by the parallel computer architecture group of Prof. Dr. Wolfgang Paul at the University of Saarbrücken, Germany. The SB-PRAM, theoretically based on Ranade's "Fluent machine" emulation approach [Ran87, RBJ88], combines several important concepts from parallel computer architecture, like multithreading and pipelining for latency hiding and cost-efficient use of silicon, a scalable combining intercon-

$<sup>^{2}</sup>$ PRAM = parallel random access machine, a straightforward extension of the sequential random access machine (RAM, also known as the von-Neumann architecture) by connecting multiple processors to a shared memory with machine-wide synchronous execution at the instruction level. The PRAM assumes unit memory access time for all processors and hence abstracts completely from the cost of shared memory access and data locality issues.

<sup>&</sup>lt;sup>3</sup>MIMD = multiple instruction streams, multiple data streams. Program control is individual for each processor.

<sup>&</sup>lt;sup>4</sup>Indeed, the strongest parallel machine model currently used is the BSR, which is even stronger than the Combine CRCW PRAM. Usually the BSR is not considered a PRAM variant but instead constitutes a different machine model.

nection network for resolving concurrent memory access conflicts and computing prefix and reduction operations on-the-fly in the network, simple RISC processors with a constant cycle time, and a common clock signal, which allows the whole machine to run synchronously at the machine instruction level and makes the computations (in principle) deterministic. The architecture is cost-effective and scalable. Unfortunately, no off-the-shelf components could be used; the prototypes are built with technology from 1991 when the design was fixed. Prototypes with (from the programmer's view) 31, 124, 498 and 1984 processors have been built; the largest prototype is currently (March 2000) still in the testing phase. The SB-PRAM group also wrote some system software and a software simulator that can be used for development and testing purposes. In short, the SB-PRAM is the only massively parallel shared memory MIMD machine in the world that is completely synchronous at the instruction level.

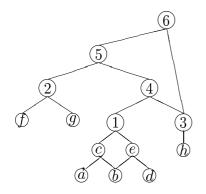

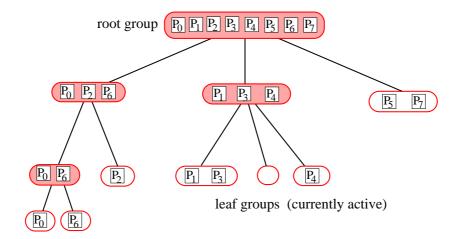

Together with the research on the architectural design of the SB-PRAM at the University of Saarbrücken, a programming language called FORK [HSS92] was proposed in 1989. The main goal of FORK was to exploit the synchronous execution feature of the SB-PRAM and make it transparent to the programmer at the operator level of the source language. A hierarchical processor group concept allows for the static and dynamic nesting of parallelism by splitting groups into subgroups, where the groups define the scope of sharing and of synchronous program execution. Group splitting can be arranged either explicitly by the programmer, or implicitly by the compiler where branches depending on nonshared values may compromise synchronous execution. In the latter case, the current group is split into one subgroup for each branch target, narrowing the scope of synchronous execution to the subgroups. With the group splitting feature, FORK enables the straightforward implementation of parallel divide-and-conquer algorithms.

But FORK was only a theoretical design and lacked nearly all features needed for practical work: pointers, data structures, dynamic arrays, function variables, floatingpoint numbers, input and output. There was no means (beyond group splitting) to escape from synchronous execution, and the language syntax was not compatible with any sequential programming language used in the real world. These restrictions in FORK seemed desirable to enable so-phisticated program analyses [Sei93] and formal correctness proofs [Sch91, Sch92, RS92]. For the practical use with the SB-PRAM however, FORK was completely unusable. A compiler for FORK was started [Lil93] in the compiler construction group at the Computer Science department of the University of Saarbrücken but was finally abandoned in early 1994. In the meanwhile the SB-PRAM group at Saarbrücken implemented on their own an asynchronous C dialect as a straightforward extension of the gcc compiler and ported the P4 library to the SB-PRAM. pgcc has been used by the SB-PRAM group to implement the operating system PRAMOS and several large-scale applications from the SPLASH benchmark suite.

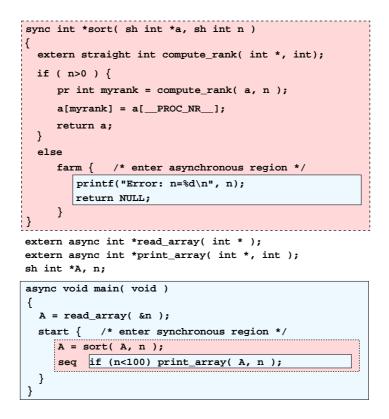

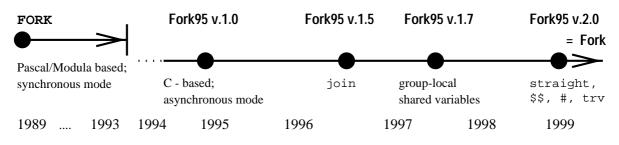

Immediately after finishing my PhD thesis in spring 1994 I was assigned the task to write a (new) compiler for FORK. Together with Prof. Dr. Helmut Seidl (now at FB IV Informatik, University of Trier, Germany) I completely redesigned [M6] the FORK language; the synchronous execution controlled by the processor groups was complemented by a second, asynchronous mode of program execution. We decided in favor of ANSI-C as the new sequential basis language <sup>5</sup>. In this way, the new language dialect, called Fork95 [I3,C8,J3], became a

<sup>&</sup>lt;sup>5</sup>This was because C was the de-facto standard in 1994. A generalization of Fork to C++ as basis language is more or less straightforward, as its parallelism features are orthogonal to the object features of C++. On the

#### 1.3. Design and Implementation of Parallel Programming Languages

proper superset of the asynchronous C variant pgcc [I6].

The implementation of the Fork95 compiler for the SB-PRAM [I3], which I did on my own, was partly based on an existing ANSI-C compiler [FH91a, FH91b, FH95]. However, the entire code generation phase, driver and the standard libraries had to be (re)written from scratch. A first runnable version of the compiler could be presented in 1995.

In the subsequent years, Fork95 was extended several times. An important new language construct is the join statement [I4,C14,B1] which provides a flexible way to collect asynchronously operating processors and make them synchronously execute a (PRAM) algorithm. A straightforward application of join is the parallel execution of—up to now, always sequentialized—critical sections, because the synchronous program execution guarantees the deterministic parallel access to shared program objects.

Currently, the Fork language has reached a stable state and is used not only by myself but also by several instructors at various European universities for teaching classes on PRAM algorithms and parallel programming. Fork is also used in research projects on parallel programming, e.g. for the design of skeleton programming [Col89] languages [Mar97] or for the implementation of the PAD library of PRAM algorithms and data structures by Dr. Jesper Träff [C10,C13,J5,B1]. I have written myself many Fork programs, e.g. a solver for linear inequality systems [C11] or the highly irregular force calculation phase in a *N*-body simulation [B1].

Unfortunately, the SB-PRAM project was technologically overtaken by the continuous performance improvement of modern microprocessors, such that performance figures—except for highly irregular or I/O-bounded applications—do no longer look impressive if compared with small-scale shared memory multiprocessor servers or even sequential PCs.

On the other hand, the efficient compilation of Fork [B1] relies on some unique hardware features of the SB-PRAM, like the instruction-level synchronous program execution or the nonsequentializing execution of atomic fetch&add instructions that are used in basic synchronization mechanisms in the Fork compiler. When compiling Fork for asynchronous parallel machines [B1], these features must be emulated in software by the compiler or the runtime system, which would lead to a dramatical loss of performance. Hence, we had, in the long range, to retarget our research on parallel programming language design and implementation to commercially available parallel machines, while using Fork only for teaching and experimenting with parallelism.

In 1996/97 I designed together with Prof. Dr. Helmut Seidl the control-synchronous parallel programming language ForkLight [M10,C16], which is based on the Asynchronous PRAM model [CZ89, Gib89]. ForkLight has many similarities to Fork, like a sequentially consistent shared memory, SPMD execution with support for nested parallelism by a hierarchical group concept, and the duality of a synchronous and an asynchronous execution mode. However, the synchronicity of program execution is relaxed to the boundaries of the basic blocks in the program. This so-called *control-synchronicity* allows for more efficient compilation on asynchronous shared memory machines like e.g. the Tera MTA. In a similar way as in Fork, ForkLight relates the degree of control synchronous program execution to the block

other hand, Java could not be chosen because the parallelism concept used in Fork is not compliant with the thread-based parallelism of Java. In [C18,J7] I have studied the combination of Fork-like SPMD parallelism with a thread-free subset of Java.

structure of the program and makes it thus transparent for the programmer. I have written an experimental compiler for ForkLight. ForkLight may also be regarded as a more flexible alternative to the recent shared memory programming standard Open-MP [Ope97].

While ForkLight, in the same way as Fork, offers sequential consistency of the shared memory, this is not efficiently supported on many parallel platforms (e.g. some virtual shared memory systems) and must be emulated by the run-time system or the compiler. In many cases, though, sequential memory consistency is not really necessary at every point of the program. Many virtual shared memory systems offer low-level constructs for controlling the consistency of shared program objects individually. Unfortunately, this results in a low-level programming style that is as tedious and error-prone as message passing.

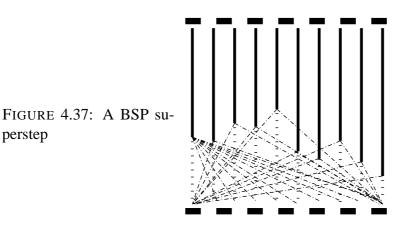

Valiant proposed the BSP<sup>6</sup> model [Val90] as a more realistic alternative to the PRAM model, by assuming a distributed-memory architecture and taking also the communication and synchronization costs into account when analyzing the complexity of a parallel program. The BSP model requires the programmer to structure a SPMD program as a sequence of so-called supersteps that are separated by global barriers. A superstep contains a phase of local computation followed by a global interprocessor communication phase specified by message passing primitives. This flat program organization is not well-suited for irregular applications. Some BSP library implementations [HMS<sup>+</sup>98, BJvR98] support one-sided communication, which offers more comfort than two-sided message passing by automatizing receiving of messages and storing their data at the target site of a communication. Nevertheless, explicit message passing means low-level, error-prone programming.

In order to introduce a shared memory programming interface and to allow for nested parallelism in the BSP model, I developed the BSP programming language NestStep [C18,I8,J7]. Again exhibiting some similarities to Fork and ForkLight, NestStep uses the group concept to specify the scope of supersteps and of shared memory consistency. I have written an experimental implementation of the NestStep run time system based on Java; experience has shown that Java is unsuitable for this purpose because it exhibits poor performance. Hence, an implementation in C with (e.g.) MPI calls for the communication of updates to shared variables appeared to be preferable. Such a reimplementation was planned as a master student project since end of 1998. Due to a lack of master students in our group at the University of Trier, I finally decided early in 2000 to write the C/MPI variant myself. Early results show an improvement in the execution time of a factor of 5 (for sequential arithmetics-dominated programs) up to a factor of more than 20 for communications-dominated programs with up to 5 processors (our local Linux PC cluster) with respect to the corresponding Java versions. In the course of this implementation work for the C-based NestStep version NestStep-C, I reworked and simplified the concept of distributed arrays and abolished the support of volatile shared variables in order to obtain a unified, BSP-compliant memory consistency schema. Section 4.5 presents the new NestStep standard and thus partially contains previously unpublished material.

Together with Prof. Dr. Jörg Keller and Dr. Jesper Träff I have written a textbook [B1] with the (somewhat provocative) title *Practical PRAM Programming*, which appears in late 2000 at Wiley (New York). This book deals with the theory, emulation, implementation, programming, and application of synchronous MIMD computers with shared memory. It introduces

<sup>&</sup>lt;sup>6</sup>BSP = bulk-synchronous parallel programming.

the PRAM model and basic PRAM theory, discusses PRAM emulation approaches, gives a complete reference to the SB-PRAM system architecture, and describes the Fork language design and implementation. It explains how to write structured parallel programs with Fork for many different parallel algorithmic paradigms and programming techniques, surveys the implementation of fundamental PRAM algorithms in the PAD library, and concludes with a parallel application written in Fork from the field of visualization and computational geometry. Part of the material that I contributed to *Practical PRAM Programming*, in particular the description of the language Fork, the concept of skeleton-style programming in Fork, and the implementation aspects of Fork, has been used and adapted in the Chapters 4 and 5 of this thesis.

## Chapter 2

# **Instruction Scheduling for RISC, Superscalar, and Vector Processors**

### 2.1 Introduction

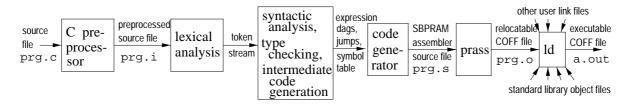

The front end of a compiler usually generates an intermediate representation (IR) of the source program that is more or less independent of the source language as well as of the target machine. This intermediate representation could be regarded as a program for a virtual machine. It is the job of the compiler's back end to generate efficient target code from the intermediate representation.

The most important optimization problems in the code generation phase of a compiler are instruction selection, register allocation, and instruction scheduling. Although these three problems have complex dependence relations among each other, and thus should be solved simultaneously, it is the current state of the art in code generators that instruction selection is performed first, while there is no general agreement on the best order and degree of integration between register allocation and instruction scheduling.

In this work we focus on approaches to the integration of register allocation and instruction scheduling for basic blocks.

#### 2.1.1 Processor Model

Our work is independent of any particular target processor. Rather, we characterize the runtime behaviour of the class of processors where our work may be immediately applied by a tuple

$\mathcal{P} = (k, N_U, N_I, U, \Delta)$

where k denotes the maximum number of instructions that may start execution in the same clock cycle,  $N_U$  specifies the number of (parallel) functional units,  $N_I$  is the number of different types of instructions,  $U : \{1, ..., N_I\} \rightarrow \{1, ..., N_U\}$  specifies for each type of instruction on which unit it is to be executed, and  $\Delta : \{1, ..., N_I\} \rightarrow \mathbb{N}_0$  gives the number of delay cycles for each type of instruction. The type of an instruction v in the intermediate representation of a program is given by  $type(v) \in \{1, ..., N_I\}$ .

A processor with k = 1 (e.g. the DLX architecture in [HP96]) is called a *single-issue processor*, a processor with k > 1 is called a *multi-issue processor*. A single-issue processor with  $\Delta(i) = 0$  for all  $i \in \{1, ..., N_I\}$  is called a *simple (RISC) processor*; a single-issue processor with  $\Delta(i) \ge 0$  for all  $i \in \{1, ..., N_I\}$  and  $\Delta(i) > 0$  for at least one instruction type i is called a *pipelined (RISC) processor*. Multi-issue processors can be VLIW (very long instruction word), EPIC (explicitly parallel instruction code), or superscalar processors. In a VLIW processor the compiler determines concretely which IR instructions will execute at runtime in the same clock cycle on different units, and composes these to a single, wide instruction word (code compaction). The assembler-language interface to a VLIW processor thus consists of specialized, wide instructions as atomic units, where different parts of a wide instruction word address different functional units (horizontal instruction set architecture, horizontal code). In contrast, for a superscalar processor the instructions remain uncompacted, and the decoding and assignment of the instructions to the functional units is done online by a runtime scheduler (the *instruction dispatcher*), which usually has a lookahead of a few instructions. Generally, a *k*-issue superscalar processor is able to dispatch up to *k* instructions in the same clock cycle. Obviously, this latter variant imposes less work on the compiler and the resulting machine code is more portable than with VLIW architectures. On the other hand, the dispatcher adds time overhead and complexity to the target processor. The more recent EPIC approach [SR00] is a compromise that should combine the advantages of both approaches, namely the exploitation and transfer of compile-time information within the code as in VLIW architectures and the flexibility of superscalar processors.

Note that our characterization of the runtime behaviour of processors contains the following simplifying assumptions:

- For the first, we assume for simplicity that  $k = N_U$ . This property holds usually for VLIW architectures. For a superscalar processor it means that the dispatcher is not the performance bottleneck. In most single-issue and superscalar processors, however, the maximum degree of instruction-level parallelism is limited by the dispatcher's capacity k. For instance, the Motorola 88110 has 10 parallel functional units but can only issue up to 2 instructions per clock cycle.

- There is only one instance of each type of functional unit. Some superscalar processors provide multiple instances of certain types of units, e.g. multiple units for integer calculcations. For instance, the Motorola 88110 has two integer units and two graphics units.

- Each instruction can be executed on exactly one of the functional units. In some superscalar processors there may be certain types of instructions that may execute on different types of units (possibly with different time behaviour); for instance, some floatingpoint unit may be able to perform also certain integer arithmetics.

- Only one functional unit is involved in the execution of an instruction. This is not necessarily the case on all architectures: For instance, on the IBM Power architecture, storing a floatingpoint number simultaneously needs the integer unit (for the address calculation) and the floatingpoint unit [Wan93].

#### 2.1. Introduction

- Execution of an instruction occupies the corresponding functional unit only for one clock cycle. Hence, even for delayed instructions, another instruction may be fed into the same unit in the following clock cycle.

- The functional units are independent of each other. In some architectures (e.g. Motorola 88100) it is possible that some stages of different functional units share components, which may lead to further delays and additional scheduling constraints [EK91].

Even for target processors where one of these constraints is not fulfilled, we are often able to work around easily by applying only a small modification to our framework. For instance, for a k-issue superscalar processor with  $k < N_U$ , we only need to add that constraint to the function that computes the run time of a given schedule. In the same way we can easily handle multiple instances of the same type of functional unit. However, we renounce the full generality in order to keep the presentation simple.

For a further introduction to the design of RISC, VLIW, and superscalar processors, we refer to [Ung95] and [HP96].

#### 2.1.2 Instruction Selection

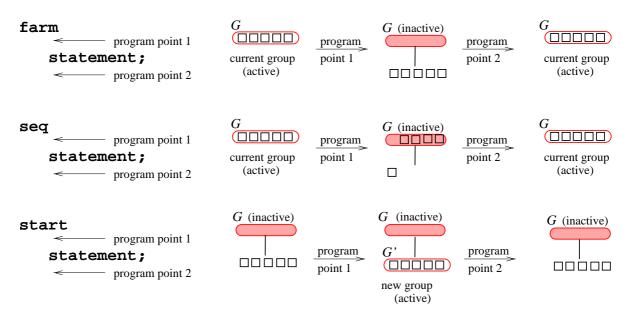

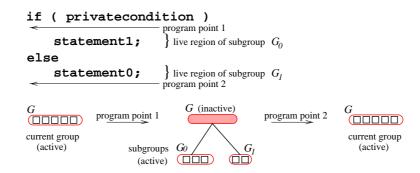

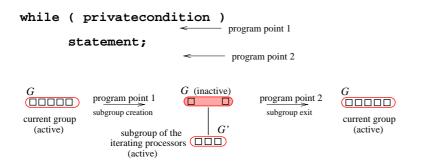

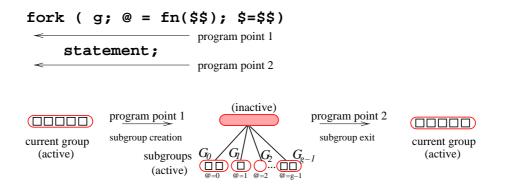

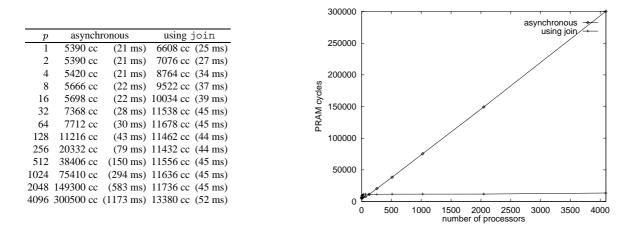

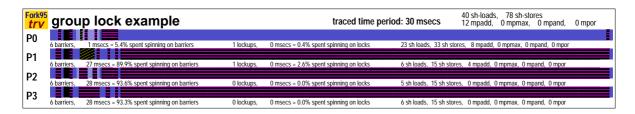

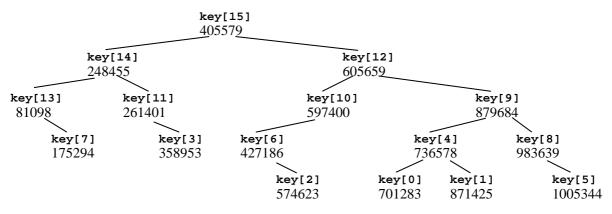

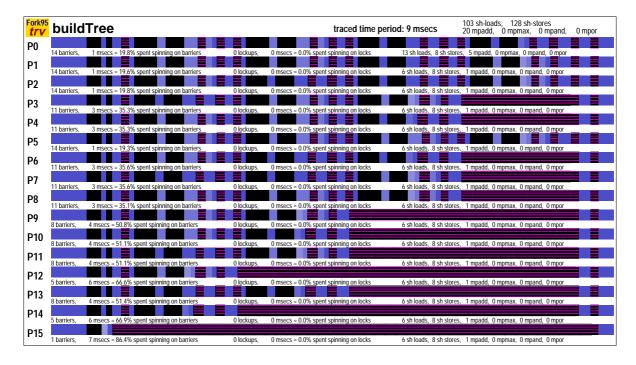

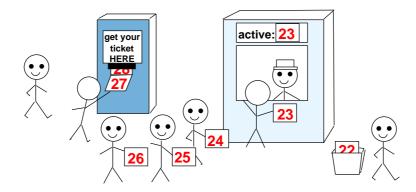

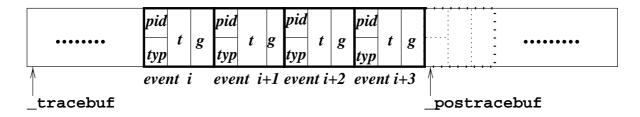

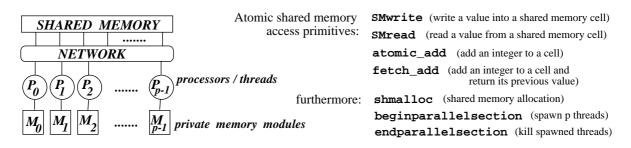

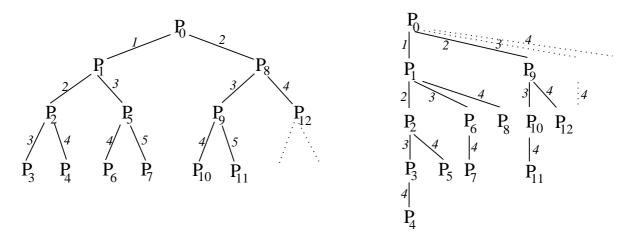

The instruction selection problem consists in covering all abstract operations of the intermediate representation of the program by sequences of concrete instructions of the target processor, such that the semantics is the same as that of the intermediate representation. If the target machine provides multiple addressing modes for an operation, or there are different sequences of operations resulting in the same behaviour, instruction selection should favour a covering with minimum total cost, in terms of execution time and register requirements. A good introduction to the instruction selection problem can be found e.g. in [FH95].