# Analyse und Optimierung von fehlertoleranten Eingebetteten Systemen mit gehärteten Prozessoren

Viacheslav Izosimov, Ilia Polian, Paul Pop, Petru Eles, Zebo Peng Universität Linköping (S), Universität Freiburg, TU Lungby (DK)

### Integration von Software- und Hardware-Fehlertoleranz

- Multiprozessorsysteme, Kommunikation über einen Bus

- Prozessoren in unterschiedlichen Härtungsgraden verfügbar

- Fehlerbehandlung in Software: Prozessneuausführungen

- Minimiere Kosten unter Echtzeit- und Zuverlässigkeitsvorgaben

## **Systemmodell**

- Anwendung: gerichteter, azyklischer Graph

- Ecken: Prozesse, Kanten: Abhängigkeiten

- Abgebildet auf ein Multiprozessorsystem

- Fehlerbehandlung durch Prozess-Neuausführung

- Beispiel: 4 Prozesse, 2 Prozessoren;

WCET, Fehlerrate, Kosten für 3 Härtungsgrade

| A                             |                                              |               |                                                        |                     |                                       |                   |                                         |

|-------------------------------|----------------------------------------------|---------------|--------------------------------------------------------|---------------------|---------------------------------------|-------------------|-----------------------------------------|

| Anwendung:<br>4 Prozesse      | N <sub>1</sub>                               | h = 1         |                                                        | h = 2               |                                       | h = 3             |                                         |

|                               | 7.41                                         | t             | р                                                      | t                   | р                                     | t                 | р                                       |

| m <sub>1</sub>                | P <sub>1</sub>                               | 60            | 1.2·10 <sup>-3</sup>                                   | 75                  | 1.2.10-5                              | 90                | 1.2-10-10                               |

| $(P_2)$ $(P_4)$               | $P_2$                                        | 75            | 1.3·10 <sup>-3</sup>                                   | 90                  | 1.3-10-5                              | 105               | 1.3·10 <sup>-10</sup>                   |

| D = 360 ms                    | P <sub>3</sub>                               | 60            | 1.4·10 <sup>-3</sup>                                   | 75                  | 1.4-10-5                              | 90                | 1.4·10 <sup>-10</sup>                   |

| D = 300 IIIS                  | $P_4$                                        | 75            | 1.6·10 <sup>-3</sup>                                   | 90                  | 1.6-10-5                              | 105               | 1.6-10 <sup>-10</sup>                   |

|                               | Kost                                         | Kosten 16     |                                                        | 32                  |                                       | 64                |                                         |

|                               | _                                            |               | 10                                                     |                     | UZ                                    | _                 | 0-7                                     |

| Architektur:<br>2 Prozessoren | F                                            |               | = 1                                                    | ŀ                   | 1 = 2                                 | h                 | ) = 3                                   |

| 2 Prozessoren                 | N <sub>2</sub>                               |               |                                                        | t                   |                                       | t                 |                                         |

|                               | F                                            |               | = 1                                                    | _                   | 1 = 2                                 | t<br>75           | i = 3                                   |

| 2 Prozessoren                 | N <sub>2</sub>                               | h<br>t        | = 1<br>p                                               | t<br>60             | n = 2<br>p                            | t                 | n = 3                                   |

| 2 Prozessoren                 | <i>N</i> <sub>2</sub>                        | <i>h t</i> 50 | = 1<br>p<br>1·10 <sup>-3</sup>                         | t<br>60             | p 1.10-5                              | <i>t</i> 75 90    | $p = 3$ $p$ $1.10^{-10}$                |

| 2 Prozessoren                 | N <sub>2</sub> P <sub>1</sub> P <sub>2</sub> | 65            | = 1<br>p<br>1.10 <sup>-3</sup><br>1.2·10 <sup>-3</sup> | t<br>60<br>75<br>60 | $p = 2$ $p$ $1.10^{-5}$ $1.2.10^{-5}$ | <i>t</i> 75 90 75 | $p = 3$ $p$ $1.10^{-10}$ $1.2.10^{-10}$ |

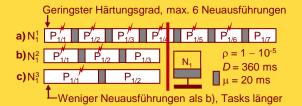

### Software- vs. Hardware-Fehlertoleranz

- Zuverlässigkeitsvorgabe ρ (Wahrscheinlichkeit eines unbehandelten Fehlers)

- Systemausfallwahrscheinlichkeits-Analyse: Berechnet notwendige Anzahl von Neu-Ausführungen, um ρ zu erreichen

# **Entwurfs- und Optimierungsstrategie**

- Ermittelt Architektur, Härtungsgrade der Knoten, Allokation von Prozessen, maximal erforderliche Anzahl von Neuausführungen pro Knoten, quasistatischen Ablaufplan

- Iteratives, heuristisches Vorgehen

- 55% Verbesserung (Anteil von zulässigen Anwendungen), synthetische Benchmarks

- 66% Kostenreduktion auf einem Vehicle Cruise Controller