# Linköping Studies in Science and Technology Thesis No. 1503

# Predictable Real-Time Applications on Multiprocessor Systems-on-Chip

by

#### Jakob Rosén

Submitted to Linköping Institute of Technology at Linköping University in partial fulfilment of the requirements for degree of Licentiate of Engineering

Department of Computer and Information Science Linköping University SE-581 83 Linköping, Sweden

Linköping 2011

This is a Swedish Licentiate's Thesis.

The Licentiate's degree comprises 120 ECTS credits of postgraduate studies.

ISBN 978-91-7393-090-1, ISSN 0280-7971 Printed by LiU-Tryck, Linköping, Sweden 2011 Copyright © 2011 Jakob Rosén Electronic version:

http://urn.kb.se/resolve?urn=urn:nbn:se:liu:diva-70138

#### Predictable Real-Time Applications on Multiprocessor Systems-on-Chip

by

Jakob Rosén

September 2011

ISBN 978-91-7393-090-1

Linköping Studies in Science and Technology

Thesis No. 1503

ISSN 0280-7971

LIU-TEK-LIC-2011:42

#### ABSTRACT

Being predictable with respect to time is, by definition, a fundamental requirement for any real-time system. Modern multiprocessor systems impose a challenge in this context, due to resource sharing conflicts causing memory transfers to become unpredictable. In this thesis, we present a framework for achieving predictability for real-time applications running on multiprocessor system-on-chip platforms. Using a TDMA bus, worst-case execution time analysis and scheduling are done simultaneously. Since the worst-case execution times are directly dependent on the bus schedule, bus access design is of special importance. Therefore, we provide an efficient algorithm for generating bus schedules, resulting in a minimized worst-case global delay.

We also present a new approach considering the average-case execution time in a predictable context. Optimization techniques for improving the average-case execution time of tasks, for which predictability with respect to time is not required, have been investigated for a long time in many different contexts. However, this has traditionally been done without paying attention to the worst-case execution time. For predictable real-time applications, on the other hand, the focus has been solely on worst-case execution time optimization, ignoring how this affects the execution time in the average case. In this thesis, we show that having a good average-case global delay can be important also for real-time applications, for which predictability is required. Furthermore, for real-time applications running on multiprocessor systems-on-chip, we present a technique for optimizing for the average case and the worst case simultaneously, allowing for a good average case execution time while still keeping the worst case as small as possible. The proposed solutions in this thesis have been validated by extensive experiments. The results demonstrate the efficiency and importance of the presented techniques.

This research work was funded in part by CUGS (the National Graduate School of Computer Science, Sweden).

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

#### Acknowledgments

So, here I am. The end of this winding road has been reached, and the thesis is finally ready. However, I would never have come to this point without the many people who gave me support, inspiration and courage during the past years. Let me first start by thanking my supervisors Zebo Peng and Petru Eles, for giving me the opportunity to become a graduate student and for always believing in me. I am very grateful for that. The working environment at IDA has been excellent, and I wish I could thank every one of my colleagues individually. If you work here and read this, consider yourself thanked!

Carl-Fredrik Neikter did a fantastic job contributing to the framework which this thesis is built upon, and I truly enjoyed our collaboration. Alexandru Andrei spent many late nights helping me with technical issues during the writing of our first paper, and for that I am thankful. I also want to thank Soheil Samii and Sergiu Rafiliu for our frequent and (usually) very enjoyable "board meetings", where we discussed all kinds of subjects related to our work.

Anton Blad and Fredrik Kuivinen have been my friends for a long time, and I really enjoyed the luxury of also having them as colleagues for a while. In particular, I want to thank them for the fun moments we spent developing the TRUT64 device (and testing it!), and of course also for just being such great guys. Furthermore, I want to express gratitude to Traian Pop for introducing me to the world of research in a friendly manner, and for throwing the best birthday parties. A big thank you must also go to everyone who participated in the official duck feeding sessions at the university pond, and to the geese and the ducks for kindly accepting the bread that I brought.

Finally, I thank my family for giving me love and support. Always.

Jakob Rosén Linköping, August 2011

## Contents

| 1 | INT                                   | RODUCTION                        | 1  |  |  |  |  |

|---|---------------------------------------|----------------------------------|----|--|--|--|--|

|   | 1.1                                   | Multiprocessor Real-Time Systems | 2  |  |  |  |  |

|   | 1.2                                   | Related Work                     | 3  |  |  |  |  |

|   | 1.3                                   | Contribution                     | 5  |  |  |  |  |

|   | 1.4                                   | Thesis Organization              | 5  |  |  |  |  |

| 2 | System Model 7                        |                                  |    |  |  |  |  |

|   | 2.1                                   | Hardware Architecture            | 7  |  |  |  |  |

|   | 2.2                                   | Application Model                | 8  |  |  |  |  |

|   | 2.3                                   | Bus Model                        | 9  |  |  |  |  |

| 3 | Pre                                   | EDICTABILITY APPROACH            | 13 |  |  |  |  |

|   | 3.1                                   | Motivational Example             | 13 |  |  |  |  |

|   | 3.2                                   | Overall Approach                 | 15 |  |  |  |  |

| 4 | Worst-Case Execution Time Analysis 19 |                                  |    |  |  |  |  |

|   | 4.1                                   | TDMA-Based WCET Analysis         | 19 |  |  |  |  |

|   | 4.2                                   | Compositional WCET Analysis Flow | 20 |  |  |  |  |

vi Contents

|   | 4.3 | 4.2.1<br>4.2.2<br>Nonco                      | Multiprocessor WCET Example              | 21<br>23<br>25 |  |  |

|---|-----|----------------------------------------------|------------------------------------------|----------------|--|--|

|   | 1.0 | Tionco                                       |                                          | 20             |  |  |

| 5 | Bus |                                              |                                          | 27             |  |  |

|   | 5.1 | WCGI                                         | D Optimization                           | 27             |  |  |

|   | 5.2 |                                              |                                          | 28             |  |  |

|   | 5.3 | Optim                                        | 11                                       | 30             |  |  |

|   |     | 5.3.1                                        |                                          | 30             |  |  |

|   |     | 5.3.2                                        |                                          | 31             |  |  |

|   |     | 5.3.3                                        | Generation of New Slot Size Candidates   | 34             |  |  |

|   |     | 5.3.4                                        | v O                                      | 35             |  |  |

|   | 5.4 | Simpli                                       | fied Algorithm                           | 38             |  |  |

|   | 5.5 |                                              | J                                        | 39             |  |  |

|   | 5.6 | Exper                                        |                                          | 40             |  |  |

|   |     | 5.6.1                                        | r r                                      | 41             |  |  |

|   |     | 5.6.2                                        | U                                        | 43             |  |  |

|   |     | 5.6.3                                        | Real-Life Example                        | 45             |  |  |

| 6 | Woi | rst/Av                                       | VERAGE-CASE OPTIMIZATION                 | 49             |  |  |

|   | 6.1 | Motiva                                       |                                          | 50             |  |  |

|   | 6.2 | Averas                                       |                                          | 52             |  |  |

|   | 6.3 |                                              |                                          | 57             |  |  |

|   | 6.4 | Bus Access Optimization for ACGD and WCGD 58 |                                          |                |  |  |

|   |     | 6.4.1                                        | <del>-</del>                             | 59             |  |  |

|   |     | 6.4.2                                        | 9                                        | 61             |  |  |

|   |     | 6.4.3                                        | · ·                                      | 63             |  |  |

|   |     | 6.4.4                                        |                                          | 64             |  |  |

|   | 6.5 | Exper                                        |                                          | 65             |  |  |

| 7 | Con | CLUSIO                                       | ons                                      | 69             |  |  |

| A | Bus | Bandy                                        | WIDTH CALCULATIONS                       | 77             |  |  |

|   | A.1 | Bus Bandwidth Calculations                   |                                          |                |  |  |

|   |     | A.1.1                                        | Calculation of the Desired Bus Bandwidth | 77             |  |  |

|   |     | A.1.2                                        |                                          | 80             |  |  |

## LIST OF FIGURES

| 2.1 | Hardware Model                    | 8  |

|-----|-----------------------------------|----|

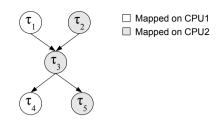

| 2.2 | Task graph                        | 9  |

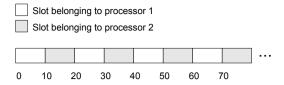

| 2.3 | Example of a bus schedule         | 10 |

| 2.4 | Bus schedule table representation | 11 |

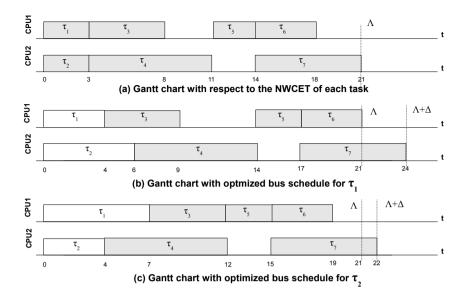

| 3.1 | Motivational example              | 14 |

| 3.2 | Overall approach example          | 16 |

| 3.3 | Overall approach                  | 18 |

| 4.1 | WCET tool program flow            | 21 |

| 4.2 | Example CFG                       | 22 |

| 4.3 | Example TDMA bus schedule         | 23 |

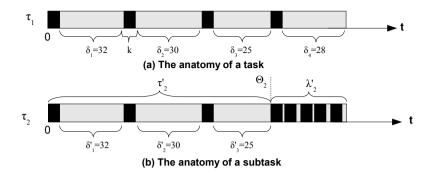

| 5.1 | Estimating the global delay       | 29 |

| 5.2 | The optimization approach         | 30 |

| 5.3 | Close-up of two tasks             | 32 |

| 5.4 | Calculation of new slot sizes     | 34 |

| 5.5 | Subtask evaluation algorithm      | 39 |

| 5.6  | The simplified optimization approach                    | 40 |

|------|---------------------------------------------------------|----|

| 5.7  | BSA1 bus schedule                                       | 41 |

| 5.8  | BSA2 bus schedule                                       | 42 |

| 5.9  | BSA3 bus schedule                                       | 42 |

| 5.10 | BSA4 bus schedule                                       | 43 |

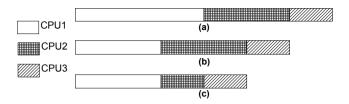

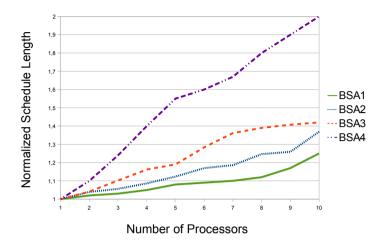

| 5.11 | Four bus access policies                                | 44 |

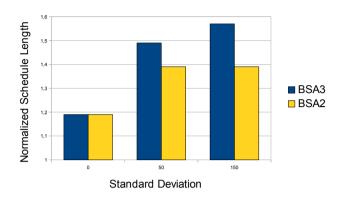

| 5.12 | Comparison between BSA2 and BSA3                        | 46 |

|      | BSA2 optimization steps                                 | 46 |

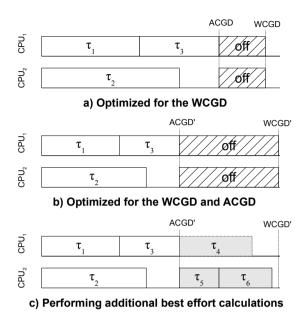

| 6.1  | Motivational example for a hard real-time system        | 51 |

| 6.2  | Motivational example for a buffer-based system          | 51 |

| 6.3  | Example histogram for 1000 executions                   | 53 |

| 6.4  | Example histogram for 12 executions                     | 53 |

| 6.5  | Example table for hypothetical path classification      | 54 |

| 6.6  | Example table for cache miss selection                  | 55 |

| 6.7  | Three hypothetical execution paths and the correspond-  |    |

|      | ing average-case execution time estimation              | 57 |

| 6.8  | Combined optimization approach                          | 58 |

| 6.9  | Example task graph                                      | 60 |

| 6.10 | Average-case chart                                      | 60 |

| 6.11 | Average-case chart with corresponding execution paths . | 61 |

| 6.12 | Average-case chart with density regions                 | 61 |

| 6.13 | The improve function                                    | 66 |

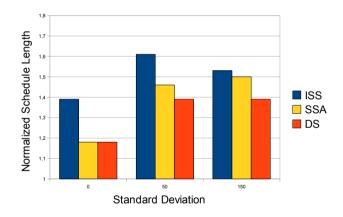

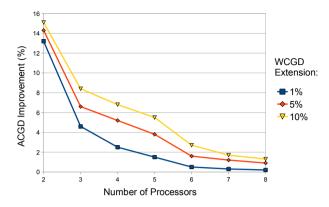

| 6.14 | Relative ACGD improvement                               | 67 |

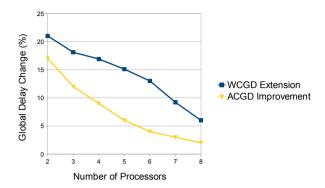

| 6.15 | Relative ACGD improvement and WCGD extension            | 68 |

#### **ABBREVIATIONS**

ACET Average-Case Execution Time

ACGD Average-Case Global Delay

BSA Bus Scheduling Approach

CFG Control Flow Graph

DS Density Region Based Sizes

ISS Initial Slot Sizes

NWCET Naive Worst-Case Execution Time

QoS Quality of Service SSA Slot Size Adjustments

TDMA Time Division Multiple Access

WCET Worst-Case Execution Time

WCGD Worst-Case Global Delay

x Abbreviations

## Introduction

Embedded real-time systems have become a key part of our society, helping us in almost every aspect of our daily living. Of significant importance is the class of safety-critical embedded real-time systems, to which we entrust our lives, for instance at hospitals, in aeroplanes and in cars. These systems must be reliable and, consequently, it is of crucial importance that they are *predictable* with respect to time. However, predictability is desirable not only for this kind of traditional hard real-time systems, but for any system exhibiting real-time properties.

This thesis describes techniques for designing predictable embedded real-time systems in a multiprocessor environment. Besides serving as an introduction to the topic, this chapter presents a summary of the state-of-the-art research within the field. After briefly describing the contributions of this thesis, the chapter ends with an outline of what follows next.

#### 1.1 Multiprocessor Real-Time Systems

For real-time systems, correctness of a program not only depends on the produced computational results, but also on its ability to deliver these on time, according to specified time constraints. Therefore, for a real-time application, predictability with respect to time is of uttermost importance. The obvious example is safety-critical hard real-time systems, such as medical and avionic applications, for which failure to meet a specified deadline not only renders the computations useless, but also can have catastrophic consequences. However, predictability is getting more and more desirable also for other classes of embedded applications, for instance within the domains of multimedia and telecommunication, for which QoS guarantees are desired [8].

As these kinds of applications become increasingly complex, they also require more computational power in terms of hardware resources. Generally, the trend in processor design is to increase the number of cores as means to improve the performance and power efficiency, and microprocessors with hundreds of cores are expected to arrive on the market in the not-so-distant future [4]. In order to satisfy the demands of complex and resource-demanding embedded systems, for which predictability is required, multicore systems implemented on a single chip are used to an increasing extent [16, 36].

To achieve predictability with respect to time, schedulability analysis techniques are applied, assuming that the worst-case execution time (WCET) of every task is known. A lot of research has been carried out within the area of worst-case execution time analysis [21]. However, according to the proposed techniques, each task is analyzed in isolation, as if it was running on a monoprocessor system. Consequently, it is assumed that memory accesses over the bus take a constant amount of time to process, since no bus conflicts can occur. For multiprocessor systems with a shared communication infrastructure, however, transfer times depend on the bus load and are therefore no longer constant, causing the traditional methods to produce incorrect results [32]. The main obstacle when performing timing analysis on multiprocessor systems is that the scheduling of tasks assumes that their worst-case execution times are known, but to calculate these worst-case execution times, knowledge about the task schedule is required. Clearly, the traditional method of separating WCET analysis and task scheduling no longer works, and new approaches are required.

Of great interest when measuring the execution time of a real-time

application is the global delay, defined as the time it takes to execute the application from its beginning to the very end. In this thesis, we propose an approach for designing predictable real-time embedded systems on multiprocessor system-on-chip architectures. We show how it is possible to design predictable systems using a TDMA bus architecture, and we also propose algorithms for generating intelligent bus schedules minimizing the worst-case global delay (WCGD) of the application.

Furthermore, we take a new approach to hard real-time system design by, in addition, also considering the effects on the average-case global delay (ACGD) while making sure that the WCGD is kept to a near-minimum. Optimization techniques for improving the average case execution time of an application, for which predictability with respect to time is not required, have been investigated in nearly every scientific discipline involving a computer. However, this has traditionally been done without paying attention to the worst-case execution time. For predictable applications, on the other hand, the focus has been solely on worst-case execution time optimization, which still is a hot research topic [6, 7]. To the best of our knowledge, this is the first time the combination of these two concepts has been investigated within the context of achieving predictability.

#### 1.2 Related Work

The fundament for achieving predictability is worst-case execution time (WCET) analysis, and a lot of research has been carried out within this area. Wilhelm et al. present an overview of the existing methods and tools [33]. None of them can, however, be applied directly to multiprocessor systems with a shared communication infrastructure, since these techniques assume a monoprocessor environment. Yan and Zhang present a new approach for worst-case execution time analysis on multicore processors with shared L2 caches [37]. They describe their work as a first, important step towards a complete framework rather than a full solution to the problem.

One approach is to use an additive bus model, assuming that conflicts on the bus do not affect the calculated worst-case execution times significantly compared to when running the same program on a monoprocessor platform. It has been shown that this is a good assumption if the bus load is kept below 60% [2], but even for such low bus loads, no worst-case execution time guarantees can be made. Furthermore,

increasing the number of processor cores will also increase the bus congestion [35] and, thus, the additive bus model is likely to not perform well for future architectures, even when strict time-predictability is not required.

Schoeber and Puschner present a technique for achieving predictability on TDMA bus-based chip multiprocessors [30]. Similar to the approach in this thesis, the output from the worst-case execution time analysis is used to improve the bus schedule. However, in order to avoid the problem of scheduling tasks, they assume that the number of cores are greater than the number of tasks.

In a recently published paper, Lv et al. use abstract modeling in Uppaal to calculate the worst-case execution time of tasks running on multiprocessor systems with a shared communication infrastructure [14]. The contribution of their approach is a very general framework with support for many kinds of buses. However, their solution does not handle computer architectures exhibiting timing anomalies.

Within the context of response time analysis [9], Schliecker et al. propose a technique using accumulated busy times instead of considering each memory access individually [29]. The result is a framework for multiprocessor analysis that computes worst-case response times with good precision, but without providing any hard timing guarantees. A more recent approach by the same authors provides conservative bounds, but without support for noncompositional architectures [28]. Schranzhofer et al. present a technique for response time analysis for TDMA bus-based multiprocessor systems with shared resources [31]. The analysis is safe, but does not support the presence of timing anomalies. Pellizzoni and Caccamo propose an approach for calculating the delay caused by bus interference for tasks running on systems with several connected peripherals [19]. They also provide a corresponding schedulability analysis framework.

Edwards and Lee argue in favor of hardware customized for achieving timing predictability, in contrast to today's platforms optimized solely for good average case performance [5]. Lickly et al. present an example of one such processor [12]. However, no such hardware exists on the market today. Paolieri et al. propose a predictable multiprocessor hardware architecture, using custom bus arbiters, designed for running hard and soft real-time tasks concurrently [17]. For hard real-time tasks, it provides a maximum bound on the memory access transfer time. The big advantage of this approach is that traditional worst-case execution

time analysis techniques can be used without modifications. However, applications with many hard real-time tasks will make this upper bound become large, potentially increasing the pessimism.

#### 1.3 Contribution

The main contributions of this thesis are:

- 1. We propose a novel technique to achieve predictability on multiprocessor systems by doing worst-case execution time analysis and scheduling simultaneously [1, 23, 24]. With respect to a given TDMA bus schedule, tasks are scheduled at the same time as their worst-case execution times are calculated, and the resulting worst-case global delay of the application is obtained.

- 2. To generate good bus schedules, we have constructed efficient optimization algorithms that minimize the worst-case global delay of the given application [23].

- 3. Combining optimization for the worst case and the average case, we have developed an approach to achieve a good average-case global delay while still keeping the worst-case delay as small as possible [25].

#### 1.4 Thesis Organization

The remaining part of the thesis is outlined as follows. In the next chapter, the system model is described in detail. The overall approach for achieving predictability is then presented in Chapter 3. In Chapter 4, we discuss the underlying worst-case analysis framework necessary for implementing our approach. Chapter 5 presents algorithms for optimization of the worst-case global delay using several bus scheduling approaches. Experimental results are presented at the end of the chapter. The algorithms for combining WCGD and ACGD optimization are presented in Chapter 6, together with a motivation for why the average case is important also for predictable real-time systems. The chapter ends with experimental results validating our approach. Finally, Chapter 7 presents our conclusions.

#### System Model

This chapter starts by describing the hardware platform that is assumed throughout the rest of the thesis. Next, the software application model is explained. Finally, we describe the model of the TDMA-based communication infrastructure.

#### 2.1 Hardware Architecture

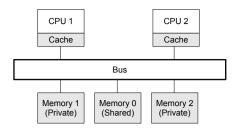

As hardware platform, we have considered a multiprocessor system-onchip architecture with a shared communication infrastructure, as shown in Figure 2.1, typical for the new generation of multiprocessor systemon-chip designs [11]. Each processor has its own cache for storing data and instructions, and is connected to a private memory via the bus. For interprocessor communication, a shared memory is used. All memory accesses to the private memories are cached, as opposed to accesses to the shared memory which, in order to avoid cache coherence problems, are not cached. All memory devices are accessed using the same, shared bus. However, in the case of private memory accesses, the bus is used only when an access results in a cache miss.

Figure 2.1 Hardware Model

Within the context of worst-case execution time analysis, hardware platforms can be divided into compositional architectures and noncompositional architectures [34], depending on whether or not the platform exhibits timing anomalies [13, 22]. Timing anomalies occur when a local worst-case scenario, such as a cache miss instead of a hit, does not result in the worst case globally. This complicates the worst-case execution time analysis significantly, since no local assumptions can be made. Compositional architectures, such as the ARM7, do not exhibit timing anomalies, and the analysis can therefore be divided into disjunct subproblems, simplifying the analysis procedure. Noncompositional architectures, on the other hand, require a far more complicated and time-consuming analysis. The PowerPC 775 is an example of a noncompositional architecture [34]. As will be described further on, our approach works for both compositional architectures and noncompositional architectures.

#### 2.2 Application Model

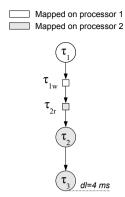

The functionality of a software application is captured by a directed acyclic task graph,  $G(\Pi, \Gamma)$ . Its nodes  $\Pi$  represent computational tasks, and the edges  $\Gamma$  represent data dependencies between them. A task cannot start executing before all of its input data is available. Communication between tasks mapped on the same processor is performed by using the corresponding private memory, and is handled in the same way as other memory requests during the execution of a task. Interprocessor communication, or so called *explicit communication*, is done via the shared memory and is modeled as two communication tasks — one for transmitting and one for receiving — in the task graph. The transmitting communication task is assigned to the same processor as

Figure 2.2 Task graph

the task that is sending data to the shared memory, and similarly the receiving communication task is assigned to the processor fetching the same data. An example is shown in Figure 2.2 where  $\tau_{1w}$  and  $\tau_{2r}$  represent the transmitting and receiving task, respectively.

A computational task cannot communicate with other tasks during its execution, which means that it will not access the shared memory. However, the task is accessing data, used in the computations, from its private memory and program instructions are continuously fetched. Consequently, the bus is accessed every time a cache miss occurs, resulting in what we define as *implicit communication*. As opposed to explicit communication, implicit communication has not been taken into account in previous approaches for real-time application system-level scheduling and optimization [20, 27].

The task graph has a deadline which represents the maximum allowed execution time of the entire application, known as the maximum global delay. Individual tasks can have deadlines as well. The example task graph in Figure 2.2 has a global delay of 4 milliseconds. The application is assumed to be running periodically, with a period greater than or equal to the application deadline.

#### 2.3 Bus Model

A precondition for achieving predictability is to use a predictable bus architecture. Therefore, we are using a TDMA-based bus arbitration policy, which is suitable for modern system-on-chip designs with QoS

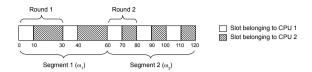

Figure 2.3 Example of a bus schedule

constraints [8, 18, 26].

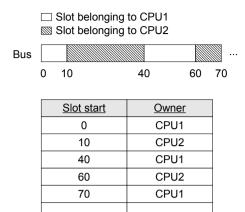

The behavior of the bus arbiter is defined by the bus schedule, consisting of sequences of slots representing intervals of time. Each slot is owned by exactly one processor, and has an associated start time and an end time. Between these two time instants, only the processor owning the slot is allowed to use the bus. A bus schedule is divided into segments, and each segment consists of a round, that is, a sequence of slots that is repeated periodically. See Figure 2.3 for an example.

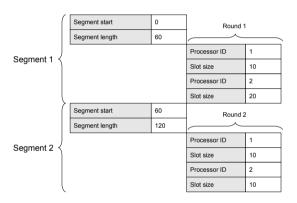

The bus arbiter stores the bus schedule in a dedicated external memory, and grants access to the processors accordingly. If processor  $CPU_i$  requests access to the bus in a time interval belonging to a slot owned by a different processor, the transfer will be delayed until the start of the next slot owned by  $CPU_i$ . A bus schedule is defined for one period of the application, and is then repeated periodically. A table representation of the bus schedule in Figure 2.3 can be found in Figure 2.4.

To limit the required amount of memory on the bus controller needed to store the bus schedule, a TDMA round can be subject to various complexity constraints. A common restriction is to let every processor own, at most, a specified number of slots per round. Also, one can let the sizes be the same for all slots of a certain round, or let the slot order be fixed.

Figure 2.4 Bus schedule table representation

## Predictability Approach

This chapter begins with a motivational example illustrating the problems encountered when designing predictable multiprocessor-based realtime systems. It then continues by describing our overall approach to achieve predictability for such systems.

#### 3.1 Motivational Example

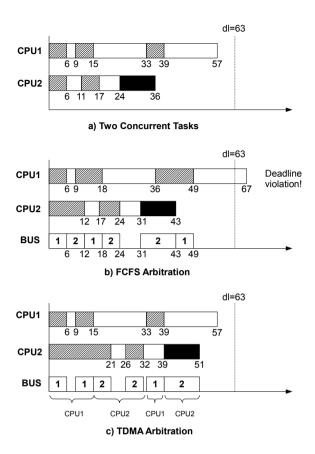

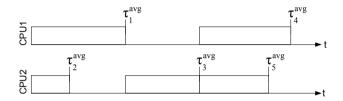

Consider two tasks running on a multiprocessor system with two processors and a shared communication infrastructure according to Chapter 2. Each task has been analyzed with a traditional WCET tool, assuming a monoprocessor system, and the resulting Gantt chart of the worst-case scenario is illustrated in Figure 3.1a. The dashed intervals represent cache misses, each of them taking six time units to serve, and the white solid areas represent segments of code not using the bus. The task running on processor 2 is also, at the end of its execution, transferring data to the shared memory, and this is represented by the black solid area.

However, since the tasks are actually running on a multiprocessor system with a shared communication infrastructure, they do not have

Figure 3.1 Motivational example

exclusive access to the bus handling the communication with the memories. Hence, some kind of arbitration policy must be applied to distribute the bus bandwidth among the tasks. The result is that when two tasks request the bus simultaneously, one of them has to wait until the other has finished transferring. This means that transfer times are no longer constant. Instead, they now depend on the bus conflicts resulting from the execution load on the different processors. Figure 3.1b shows the corresponding Gantt chart when the commonly used FCFS arbitration policy is applied.

The fundamental problem when performing worst-case execution time analysis on multiprocessor systems is that the load on the other processors is in general not known. For a task, the number of cache misses and their location in time depend on the program control flow path. This means that it is very hard to foresee where there will be bus access collisions, since this will differ from execution to execution. To complicate things further, the worst-case control flow path of the task will change depending on the bus load originating from the other concurrent tasks. In order to solve this and introduce predictability, we use a TDMA bus schedule which, a priori, determines exactly when a processor is granted the bus, regardless of what is executed on the other processors. Given a TDMA bus schedule, the WCET analysis tool calculates a corresponding worst-case execution time. Some bus schedules will result in relatively short worst-case execution times, whereas others will be very bad for the worst case. Therefore, it is important that a clever bus schedule, optimized to reduce the worst case, is used. Algorithms for this will be presented in Chapter 5. Note that regardless of what bus schedule is given as input to the WCET analysis algorithm, the corresponding worst-case execution time will always be safe. Figure 3.1c shows the same task configuration as previously, but now the memory accesses are arbitrated according to a TDMA bus schedule.

#### 3.2 Overall Approach

For a task running on a multiprocessor system, as described in Chapter 2, the problem for achieving predictability is that the duration of a bus transfer depends on the bus congestion. Since bus conflicts depend on the task schedule, WCET analysis cannot be performed before that is known. However, task scheduling traditionally assumes that the worst-case execution times of the tasks to be scheduled are already calculated.

To solve this circular dependency, we have developed an approach based on the following principles:

- 1. A TDMA-based bus access policy, according to Section 2.3, is used for arbitration. The bus schedule, created at design time, is enforced during the execution of the application.

- 2. The worst-case execution time analysis is performed with respect to the bus schedule, and is integrated with the task scheduling process, as described in Figure 3.3.

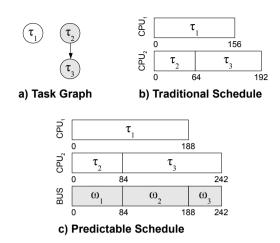

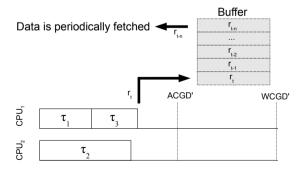

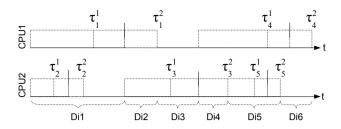

We illustrate our overall approach with a simple example. Consider the application in Figure 3.2a. It consists of three tasks  $-\tau_1$ ,  $\tau_2$  and  $\tau_3$  – mapped on two processors. The static cyclic scheduling process is

Figure 3.2 Overall approach example

based on a list scheduling technique, and is performed in the outer loop described in Figure 3.3 [10]. Let us, as is done traditionally, assume that worst-case execution times have been obtained using techniques where each task is considered in isolation, ignoring conflicts on the bus. These calculated worst-case execution times are 156, 64, and 128 time units for  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$ , respectively. The deadline is set to 192 time units, and would be considered as satisfied according to traditional list scheduling, using the already calculated worst-case execution times, as shown in Figure 3.2b. However, this assumes that no conflicts, extending the bus transfer durations (and implicitly the memory access times), will ever occur on the bus. This is, obviously, not the case in reality and thus results obtained with the previous assumption are wrong.

In our predictable approach, the list scheduler will start by scheduling the two tasks  $\tau_1$  and  $\tau_2$  in parallel, with start time 0, on their respective processor (line 2 in Figure 3.3). However, we do not yet know the end times of the tasks, and to gain this knowledge, worst-case execution time analysis has to be performed. In order to do this, a bus schedule which the worst-case execution times will be calculated with respect to (line 6 in Figure 3.3) must be selected. This bus schedule is, at the moment, constituted by one bus segment  $\omega$ , as described in Section 2.3. Given this bus schedule, worst-case execution times of tasks  $\tau_1$  and  $\tau_2$  will be computed (line 7 in Figure 3.3). Based on this output, new bus schedule candidates are generated and evaluated (lines 5-8 in Figure 3.3), with the goal of obtaining those worst-case execution times that

lead to the shortest possible worst-case global delay of the application. Assume that, after selecting the best bus schedule, the corresponding worst-case execution times of tasks  $\tau_1$  and  $\tau_2$  are 167 and 84 respectively. We can now say the following:

- Bus segment  $\omega_1$  is the first segment of the application bus schedule, and will be used for the time interval 0 to 84.

- Both tasks  $\tau_1$  and  $\tau_2$  start at time 0.

- In the worst case,  $\tau_2$  ends at time 84 (the end time of  $\tau_1$  is still unknown, but it will end later than 84).

Now, we go back to step 3 in Figure 3.3 and schedule a new task,  $\tau_3$ , on processor CPU<sub>2</sub>. According to the previous worst-case execution time analysis, task  $\tau_3$  will, in the worst case, be released at time 84, scheduled in parallel with the remaining part of task  $\tau_1$ . A new bus segment  $\omega$ , starting at time 84, will be selected and used for analyzing task  $\tau_3$ . For task  $\tau_1$ , the already fixed bus segment  $\omega_1$  is used for the time interval between 0 and 84, after which the new segment  $\omega$  is used. Once again, several bus schedule candidates are evaluated, and finally the best one, with respect to the worst-case global delay, is selected. Assume that the segment  $\omega_2$  is finally selected, and that the worst-case execution times for tasks  $\tau_1$  and  $\tau_3$  are 188 and 192 respectively, making task  $\tau_3$  end at 276. Now,  $\omega_2$  will become the second bus segment of the application bus schedule, ranging from time 84 to 188, and this part of the bus schedule will be fixed. Now, we repeat the same procedure with the remaining part of  $\tau_3$  (which now ends at time 242 instead of 276, since  $\omega_3$  assigns all bus bandwidth to CPU<sub>2</sub>). The final, predictable schedule is shown in Figure 3.2c, and leads to a WCGD of 242.

An outline of the algorithm can be found in Figure 3.3. We define  $\Psi$  as the set of tasks active at the current time t, and this is updated in the outer loop. In the beginning of the loop, a new bus segment  $\omega$ , starting at t, is generated and the resulting bus schedule candidate is evaluated with respect to each task in  $\Psi$ . Based on the outcome of the WCET analysis, the bus segment  $\omega$  is improved for each iteration. The bus segments previously generated before time t remain unaffected. After selecting the best segment  $\omega$ ,  $\theta$  is set to the end time of the task in  $\Psi$  that finished first. The time t is updated to  $\theta$  and we continue with the next iteration of the outer loop.

Communication tasks are treated as a special class of computational tasks, which are generating a continuous flow of cache misses with no

```

O1: \theta=0

02: while not all tasks scheduled

03:

schedule new task at t \geq \theta

04:

\Psi=set of all tasks that are active at time t

05:

repeat

06:

select bus segment \omega for the

time interval starting at t

07:

determine the WCET of all tasks in \boldsymbol{\Psi}

08:

until termination condition

09:

\theta=earliest time a task in \Psi finishes

10: end while

```

Figure 3.3 Overall approach

computational cycles in between. The number of cache misses is specified such that the total amount of data transferred on the bus, due to these misses, equals the maximum length of the explicit message. Therefore, from an analysis point of view, no special treatment is needed for explicit communication. In the following, when we talk about cache misses, it applies to both explicit and implicit communication.

## Worst-Case Execution Time Analysis

In order to calculate the WCET of a task, the analysis needs to be aware of the TDMA bus, taking into account that processors must be granted the bus only during their assigned time slots. This chapter describes the modifications required in order to adopt a traditional WCET algorithm to our predictable approach, without increasing the overall time-complexity.

#### 4.1 TDMA-Based WCET Analysis

Performing worst-case execution time analysis with respect to a TDMA bus schedule requires not only knowledge about the number of cache misses for a certain program path, but also their location with respect to time. Hence, traditional ILP-based methods for worst-case execution time analysis cannot be applied. Instead, each memory access needs to be considered with respect to the bus schedule, granting access to the bus only during the slots belonging to the requesting processor. However, to collect the necessary information used by our worst-case execution time analysis framework, the same techniques used in traditional

methods can be utilized.

Calculating the worst-case execution time has to be done with respect to the particular hardware architecture on which the task being analyzed is going to be executed. Factors such as the instruction set, pipelining complexity, caches and so on must be taken into account by the analysis. For an application running on a compositional architecture, the analysis can be divided into subproblems processed in a local fashion, for instance on basic block level. We can be sure that the local worst-case always contributes to the worst-case globally, allowing for fast analysis techniques without the need to analyze every single program path individually. This is, unfortunately, not the case when using noncompositional architectures. The presence of timing anomalies will force the analysis to consider all possible program paths explicitly, naturally causing the analysis time to explode as the size of the tasks increase.

For a predictable multiprocessor system with a shared communication structure, as described in Chapter 2, it is necessary to search through all feasible program paths and match each possible bus transfer to slots in the actual bus schedule, keeping track of exactly when a bus transfer is granted the bus in the worst case. This means that the execution time of a basic block will vary depending on when it is executed. Fortunately, for an application running on a compositional architecture, efficient search-tree pruning techniques dramatically reduce the search space, allowing for local analysis, just as for traditional WCET techniques.

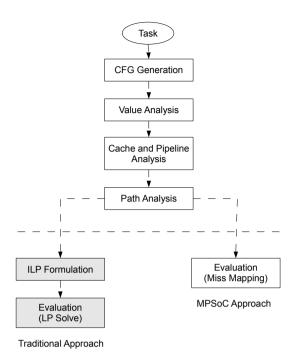

#### 4.2 Compositional WCET Analysis Flow

A typical program flow for a WCET tool operating on compositional architectures is shown in the left path of Figure 4.1 [33]. First, a control flow graph (CFG) is generated. A value analysis is then performed to find program characteristics such as data address ranges and loop bounds. To take into account performance-enhancing features of modern hardware, cache and pipeline analyses are carried out next. A path analysis identifies the feasible paths and an ILP formulation for calculating the worst-case program path is then produced. The information traditionally provided in this ILP formulation is, however, not sufficient for calculating the WCET on a multiprocessor system since not only the number of cache misses are needed for each basic block, but

Figure 4.1 WCET tool program flow

also their positions with respect to time. If necessary, an underlying WCET tool has to be modified to provide this information. A more in-depth description can be found in the work published by Neikter [3].

Our TDMA-based approach for compositional WCET analysis is illustrated in the right path of Figure 4.1. After the path analysis, the information from the previous steps is used to calculate the worst-case program path by mapping the cache misses to the corresponding bus slots in the TDMA schedule. We will now show the idea behind this with a simple example.

#### 4.2.1 Monoprocessor WCET Example

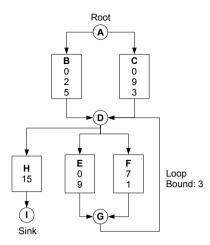

Consider a task  $\tau$  executing on a system with two processors (processor 1 and processor 2). The task is being mapped on processor 1, and has start time 0. First, an annotated control flow graph, as illustrated in Figure 4.2, is constructed. The rectangular elements **B**, **C**, **H**, **E**, **F** in

Figure 4.2 Example CFG

the graph represent basic blocks, and the circles  $\mathbf{A}$ ,  $\mathbf{D}$ ,  $\mathbf{G}$ ,  $\mathbf{I}$  represent control nodes gluing them together. The loop starting at control node  $\mathbf{G}$  will run at most three times, so the loop bound is consequently set to 3. The annotated numbers in the basic blocks represent consecutive cycles of execution, in the worst case, not accessing the bus. For instance, basic block  $\mathbf{B}$  will, when executed, immediately – after 0 clock cycles – issue a cache miss. After this, 2 cycles will be spent without bus accesses before the next (and last) cache miss occurs. Finally, 5 bus access-free cycles will be executed before the basic block ends. Hence, the execution time of basic block  $\mathbf{B}$  will be  $(0 + k_1 + 2 + k_2 + 5)$  where  $k_1$  and  $k_2$  represent the transfer times of the first and second cache miss respectively. Note that usually, loop unrolling is performed in order to decrease the pessimism of the analysis. This example is, however, purposely kept as simple as possible, and therefore the loop has not been unrolled.

For a typical monoprocessor system, all cache misses take the same constant amount of time to process, and the execution time of basic block  ${\bf B}$  would be known immediately. However, for multiprocessor architectures such as the one described in Chapter 2, we must calculate the individual transfer times with respect to a given TDMA schedule.

Figure 4.3 Example TDMA bus schedule

#### 4.2.2 Multiprocessor WCET Example

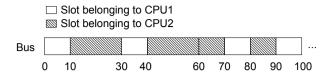

Instead of a monoprocessor system, assume a multiprocessor system, as described in Chapter 2, using the bus schedule in Figure 4.3. Processor 1, on which the task is running, gets a bus slot of size 10 processor cycles periodically assigned to it every 20th cycle. In this particular example, a cache miss takes 10 cycles for the bus to transfer, resulting in the bus being granted to processor 1 *only* at times t satisfying  $t \equiv 0 \pmod{20}$ , where t is the congruence operator.

To calculate the worst-case program path, we must evaluate all feasible program paths in the control flow graph. In the very simple example in Figure 4.2, there are 30 program paths<sup>1</sup> to explore, growing exponentially with the number of branches and loop bounds. Fortunately, due to the nature of the compositional architecture and the TDMA bus, not all of them have to be investigated explicitly. In fact, in a task graph with all loops unrolled, each basic block would need to be investigated exactly once, as will be explained in the following.

Let us denote the worst-case start time of a basic block  $\mathbf{Z}$  by  $s(\mathbf{Z})$ , and the end time in the worst case by  $e(\mathbf{Z})$ . The execution time of a basic block  $\mathbf{Z}$ , in the worst case, is then defined as  $w(\mathbf{Z}) = e(\mathbf{Z}) - s(\mathbf{Z})$ . Without considering bus conflicts, as in traditional methods, the worst-case execution time of the basic blocks would be  $w_{\text{trad}}(\mathbf{B}) = 27, w_{\text{trad}}(\mathbf{C}) = 32, w_{\text{trad}}(\mathbf{E}) = 19, w_{\text{trad}}(\mathbf{F}) = 18$  and  $w_{\text{trad}}(\mathbf{H}) = 15$ . The corresponding worst-case program path becomes  $\mathbf{C}, \mathbf{E}, \mathbf{E}, \mathbf{H}$  resulting in a worst-case execution time of  $27+19\cdot3+15=104$  clock cycles. However, this assumes that all cache misses take the same amount of time to transfer, and this is false in a multiprocessor system with a shared communication structure. In our TDMA-based approach, the execution time of a basic block depends on its start time in relation to the bus schedule. We start from the root node and successively calculate the execution time of each basic block with respect to the worst-case

$<sup>12 + 2^2 + 2^3 + 2^4 = 30</sup>$

24

start time. At the same time, the worst-case path is calculated.

With respect to the TDMA schedule in figure 4.3, the worst-case start times of the basic blocks connected directly to the root node is 0, since they will never execute at any other time instant. The execution time of block  $\mathbf{B}$ , in the worst case, is  $w(\mathbf{B}) = 0 + 10 + 2 + 18 + 5 = 35$  whereas the corresponding execution time of block  $\mathbf{C}$  is  $w(\mathbf{C}) = 0 + 10 + 9 + 11 + 3 = 33$ . Note that  $w(\mathbf{B}) > w(\mathbf{C})$ , even though the relation is the opposite in the traditional case above where  $w_{\text{trad}}(\mathbf{B}) < w_{\text{trad}}(\mathbf{C})$ . In order to decide which one of these two basic blocks is on the critical path, two very important observations must be made based on the predictable nature of the TDMA bus (and the compositionality considered in this section).

- 1. The absolute end time of a basic block can never increase by letting it start earlier. That is, a basic block  $\mathbf{Z}$  with  $s(\mathbf{Z}) = x$  and  $e(\mathbf{Z}) = y$ , any start time x' < x will result in an end time  $y' \leq y$ . The execution time of the particular basic block can increase, but the increment can never exceed the difference x x' in start time. This means that for a basic block  $\mathbf{Z}$ , the basic block will never end later than  $e(\mathbf{Z})$  as long as it start before (or at)  $s(\mathbf{Z})$ . This guarantees that the worst-case calculations will never be violated, no matter what program path is taken. Note that  $w(\mathbf{Z})$  is the execution time in the worst case, with respect to  $e(\mathbf{Z})$ , and that the time spent by executing  $\mathbf{Z}$  can be greater than  $w(\mathbf{Z})$  for an earlier start time than  $s(\mathbf{Z})$ .

- 2. Consider a basic block **Z** with worst-case start time  $s(\mathbf{Z}) = x$  and worst-case end time  $e(\mathbf{Z}) = y$ . If we, instead, assume a worst-case start time of  $s(\mathbf{Z}) = x''$  where x'' > x, the corresponding resulting absolute end time  $e(\mathbf{Z}) = y''$  will always satisfy the relation  $y'' \ge y$ . This means that the greatest assumed worst-case start time  $s(\mathbf{Z})$  will also result in the greatest absolute end time  $e(\mathbf{Z})$ .

Based on the second observation, we can be sure that the maximum absolute end time for the basic block (**E**, **F** or **H**) succeeding **B** and **C** will be found when the worst-case start time is set to 35 rather than 33. Therefore, we conclude that **B** is on the worst-case program path and, since they are not part of a loop, **B** and **C** do not have to be investigated again.

Next follow three choices. We can enter the loop by executing either **E** or **F**, or we can go directly to **H** and end the task immediately. Due

to observation 2 above, we can conclude that the worst-case absolute end time of H, and thus the entire task, will be achieved when the loop iterates the maximum possible number of times, which is 3 iterations, since that will maximize  $s(\mathbf{H})$ . Therefore, the next step is to calculate the worst-case execution time for basic blocks E and F respectively for each of the three iterations, before finally calculating the worstcase execution time of H. In the first iteration, the worst-case start time is  $s(\mathbf{E_1}) = s(\mathbf{F_1}) = 35$  and the execution times become  $w(\mathbf{E_1}) =$ 0+15+9=24 and  $w(\mathbf{F_1})=7+28+1=36$  for **E** and **F** respectively. We conclude that the worst-case program path so far is B, F and the new start time is set to  $s(\mathbf{E_2}) = s(\mathbf{F_2}) = 35 + 36 = 71$ . In the second loop iteration, we get  $w(\mathbf{E_2}) = 0 + 19 + 9 = 28$  and  $w(\mathbf{F_2}) = 7 + 12 + 1 = 20$ . Hence, in this iteration, E contributes to the worst-case program path and the new worst-case start time becomes  $s(\mathbf{E_3}) = s(\mathbf{F_3}) = 99$ . In the final iteration, the execution times are  $w(\mathbf{E_3}) = 0 + 11 + 9 = 20$  and  $w(\mathbf{F_3}) = 7 + 24 + 1 = 32$  respectively, resulting in the new worst-case start time  $s(\mathbf{H}) = 131$ . We now know that the worst-case program path is B, F, E, F, H, and since H contains no cache misses, and therefore always takes 15 cycles to execute, the WCET of the entire task is  $e(\mathbf{H}) =$ 146.

As shown in this example, in a loop-free control flow graph, each basic block has to be visited once. For control flow graphs containing loops, the number of investigations will be the same as for the case where all loops are unrolled according to their respective loop bounds. The result, when the graph is traversed, is a time-complexity not higher than for traditional monoprocessor worst-case execution time analysis techniques.

## 4.3 Noncompositional Analysis

In the presence of timing anomalies, it is no longer possible to do local assumptions about the global worst case execution time. Therefore, for such architectures, every program path has to be analyzed explicitly. This is the case, not only for multiprocessor systems, but for any worst-case execution time framework operating on a noncompositional platform. Also, all steps in Figure 4.1, from the cache and pipeline analyses and forward, must be integrated since it, for noncompositional architectures, is impossible to assume safe initial cache and pipeline states for a basic block, regardless of the allowed pessimism. Since also tradi-

tional WCET analysis operating on noncompositional hardware has to perform a global search through all program paths, the modifications in order to make it aware of the TDMA bus is, in theory, straight-forward. To adapt a traditional noncompositional WCET analysis technique to the class of multiprocessor systems described in Chapter 2, for each considered cache miss, the bus schedule has to be searched in order to find the start and end times of the corresponding bus transfer. This operation is of linear complexity and will therefore not increase the total, already exponential, complexity of the traditional worst-case execution time analysis.

## BUS SCHEDULE OPTIMIZATION

Given any TDMA bus schedule, the WCET analysis framework described in Chapter 4 calculates a safe worst-case execution time. This means that the WCET of a task is directly dependent on the bus schedule. This chapter describes how to generate a bus schedule, while satisfying various efficiency requirements. At the end of the chapter, we present experimental results showing the efficiency of our approach.

## 5.1 WCGD Optimization

Since the bus schedule is directly affecting the worst-case execution time of the tasks, and consequently also the worst-case global delay of the application, it is important that it is chosen carefully. Ideally, when constructing the bus schedule, we would like to allocate a time slot for each individual cache miss on the worst-case control flow path, granting access to the bus immediately when it is requested. There are, however, two significant problems preventing us from doing this. The first one is that several processors can issue a cache miss at the same time instant, creating conflicts on the bus. The second problem is that allocating bus

slots for each individual memory transfer would create a very irregular bus schedule, requiring an unfeasible amount of memory space on the bus controller.

In order to solve the problem of irregular, memory consuming bus schedules, some restrictions on the TDMA round complexity need to be imposed. For instance, an efficient strategy is to allow each processor to own a maximum number of slots per round. Other limitations can be to let each round have the same slot order, or to force the slots in a specific round to have the same size. In this chapter, we assume that every processor can own at most one bus slot per round. The slots in a round can have different sizes, and the order can be set without restrictions. However, it is straight-forward to adapt this algorithm to more (or less) flexible bus schedule design rules. In addition to the main algorithm, we present a simplified algorithm for the special case where all slots in a round must be of the same size.

The problem of handling cache miss conflicts is solved by distributing the bus bandwidth such that the transfer times of cache misses, contributing directly to the worst-case global delay, are minimized. This is done in the inner loop of the overall approach outlined in Figure 3.3. For the optimization process, we start by defining a cost function that estimates the worst-case global delay as a function of the bandwidth distribution. A detailed description will follow in the next section.

#### 5.2 Cost Function

Given a set of active tasks  $\tau_i \in \Psi$  (see Figure 3.3), the goal is now to generate a close to optimal bus segment schedule with respect to  $\Psi$ . An optimal bus schedule, however, is a bus schedule taking into account the global context, minimizing the global delay of the application. This global delay includes tasks not yet considered and for which no bus schedule has been defined. This requires knowledge about future tasks, not yet analyzed, and, therefore, we must find ways to approximate their influence on the global delay.

In order to estimate the global delay, we first build a schedule  $S^{\lambda}$  of the tasks not yet analyzed, using a list scheduling technique. When building  $S^{\lambda}$  we approximate the WCET of each task by its respective worst-case execution time in the naive case, where no conflicts occur on the bus and any task can access the bus at any time. From now on we refer to this conflict-free WCET as NWCET (Naive Worst-Case

Figure 5.1 Estimating the global delay

Execution Time).

When optimizing the bus schedule for the tasks  $\tau \in \Psi$ , we need an approximation of how the WCET of one task  $\tau_i \in \Psi$  affects the global delay. Let  $D_i$  be the union of the set of all tasks depending directly on  $\tau_i$  in the process graph, and the singleton set containing the first task in  $S^{\lambda}$  that is scheduled on the same processor as  $\tau_i$ . We now define the tail  $\lambda_i$  of a task  $\tau_i$  recursively as:

- $\lambda_i = 0$ , if  $D_i = \emptyset$

- $\lambda_i = \max_{\tau_j \in D_i} (x_j + \lambda_j)$ , otherwise.

where  $x_j = \text{NWCET}_j$  if  $\tau_j$  is a computation task. For communication tasks,  $x_j$  is an estimation of the communication time, depending on the length of the message. Intuitively,  $\lambda_i$  can be seen as the length of the longest (with respect to the NWCET) chain of tasks that are affected by the execution time of  $\tau_i$ . Without any loss of generality, in order to simplify the presentation, only computation tasks are considered in the examples of this section. Consider Figure 5.1a, illustrating a Gantt chart of tasks scheduled according to their NWCETs. Direct data dependencies exist between tasks  $\tau_4$  &  $\tau_5$ ,  $\tau_5$  &  $\tau_6$ , and  $\tau_5$  &  $\tau_7$ ; hence,

for instance,  $D_3 = \{\tau_5\}$  and  $D_4 = \{\tau_5, \tau_7\}$ . The tails of the tasks are:  $\lambda_7 = \lambda_6 = 0$  (since  $D_7 = D_6 = \emptyset$ ),  $\lambda_5 = 7$ ,  $\lambda_4 = \lambda_3 = 10$ ,  $\lambda_2 = 18$  and  $\lambda_1 = 15$ .

Since our concern when optimizing the bus schedule for the tasks in  $\Psi$  is to minimize the global delay, a cost function taking  $\lambda_i$  into account can be formulated as follows:

$$C_{\Psi,\theta} = \max_{\tau_i \in \Psi} (\theta + \text{WCET}_i^{\theta} + \lambda_i)$$

(5.1)

where WCET<sub>i</sub><sup> $\theta$ </sup> is defined as the length of that portion of the worst case execution path of task  $\tau_i$  which is executed after time  $\theta$ .

## 5.3 Optimization Approach

The optimization algorithm is outlined in Figure 5.2.

- 1. Calculate initial slot sizes.

- 2. Calculate an initial slot order.

- 3. Analyze the WCET of each task  $\tau \in \Psi$  and evaluate the result according to the cost function.

- Generate a new slot order candidate and repeat from 3 until all candidates are evaluated.

- Generate a new slot size candidate and repeat from 2 until the exit condition is met.

- The best configuration according to the cost function is then used.

Figure 5.2 The optimization approach

These steps will now be explained in detail, starting with the inner loop that decides the order of the slots. Given a specific slot size, we search the order of slots that yields the best cost.

#### 5.3.1 Slot Order Selection

At step 2 of the algorithm in Figure 5.2, a default initial order is set. When step 4 is reached for the first time, after calculating a cost for the current slot configuration, the task  $\tau_i \in \Psi$  that is maximizing the cost function in Equation 5.1 is identified. We then construct n-1

new bus schedule candidates, n being the number of tasks in the set  $\Psi$ , by moving the slot corresponding to this task  $\tau_i$ , one position at a time, within the TDMA round. The best configuration with respect to the cost function is then selected. Next, we check if any new task  $\tau_j$ , different from  $\tau_i$ , now has taken over the role of maximizing the cost function. If so, the procedure is repeated, otherwise it is terminated.

#### 5.3.2 Determination of Initial Slot Sizes

At step 1 of the algorithm in Figure 5.2, the initial slot sizes are dimensioned based on an estimation of how the slot size of an individual task  $\tau_i \in \Psi$  affects the global delay.

Consider  $\lambda_i$ , as defined in Section 5.2. Since it is a sum of the NWCETs of the tasks forming the tail of  $\tau_i$ , it will never exceed the accumulative WCET of the same sequence of tasks. Consequently, if we for all  $\tau_i \in \Psi$  define

$$\Lambda = \max_{\tau_i \in \Psi} (\text{NWCET}_i^{\theta} + \lambda_i)$$

(5.2)

where NWCET $_i^{\theta}$  is the NWCET of task  $\tau_i \in \Psi$  counting from time  $\theta$ , a lower limit of the global delay can be calculated by  $\theta + \Lambda$ . This is illustrated in Figure 5.1a, for  $\theta = 0$ . Furthermore, let us define  $\Delta$  as the amount by which the estimated global delay increases due to the time each task  $\tau_i \in \Psi$  has to wait for the bus.

See Figure 5.1b for an example. Contrary to Figure 5.1a,  $\tau_1$  and  $\tau_2$  are now considered using their real WCETs, calculated according to a particular bus schedule ( $\Psi = \{\tau_1, \tau_2\}$ ). The corresponding expansion  $\Delta$  is 3 time units. Now, in order to minimize  $\Delta$ , we want to express a relation between the global delay and the actual bus schedule. For task  $\tau_i \in \Psi$ , we define  $m_i$  as the number of remaining cache misses on the worst case path, counting from time  $\theta$ . Similarly, also counting from  $\theta$ ,  $l_i$  is defined as the sum of each code segment and can thus be seen as the length of the task minus the time it spends using the bus or waiting for it (both  $m_i$  and  $l_i$  are determined by the WCET analysis). Hence, if we define the constant k as the time it takes to process a cache miss when ignoring bus conflicts, we get

$$NWCET_i^{\theta} = l_i + m_i k \tag{5.3}$$

As an example, consider Figure 5.3a showing a task execution trace, in the case where no other tasks are competing for the bus. A black box

Figure 5.3 Close-up of two tasks

represents the idle time, waiting for the transfer, due to a cache miss, to complete. In this example  $m_1 = 4$  and  $l_1 = \delta_1 + \delta_2 + \delta_3 + \delta_4 = 115$ .

Let us now, with respect to the particular bus schedule, denote the average waiting time of task  $\tau_i$  by  $d_i$ . That is,  $d_i$  is the average time task  $\tau_i$  spends waiting, due to other processors owning the bus and the actual time of the transfer itself, every time a cache miss has to be transferred on the bus. Then, analogous to Equation 5.3, the WCET of task  $\tau_i$ , counting from time  $\theta$ , can be calculated as

$$WCET_i^{\theta} = l_i + m_i d_i \tag{5.4}$$

The dependency between a set of average waiting times  $d_i$  and a bus schedule can be modeled as follows. Consider the distribution P, defined as the set  $p_1, \ldots, p_n$ , where  $\sum p_i = 1$ . The value of  $p_i$  represents the fraction of bus bandwidth that, according to a particular bus schedule, belongs to the processor running task  $\tau_i \in \Psi$ . Given this model, the average waiting times can be rewritten as

$$d_i = \frac{1}{p_i}k\tag{5.5}$$

Putting Equations 5.2, 5.4, and 5.5 together and noting that  $\Lambda$  has been calculated as a maximum over all  $\tau_i \in \Psi$ , we can formulate the following

system of inequalities:

$$\theta + l_1 + m_1 \frac{1}{p_1} k + \lambda_1 \le \theta + \Lambda + \Delta$$

$$\vdots$$

$$\theta + l_n + m_n \frac{1}{p_n} k + \lambda_n \le \theta + \Lambda + \Delta$$

$$p_1 + \dots + p_n = 1$$

What we want is to find the bus bandwidth distribution P that results in the minimum  $\Delta$  satisfying the above system. Unfortunately, solving this system is difficult due to its enormous solution space. However, an important observation that simplifies the process can be made, based on the fact that the slot distribution is represented by continuous variables p. Consider a configuration of  $p_1, \ldots, p_n, \Delta$  satisfying the above system, and where at least one of the inequalities are not satisfied by equality. We say that the corresponding task  $\tau_i$  is not on the critical path with respect to the schedule, meaning that its corresponding  $p_i$ can be decreased, causing  $\tau_i$  to expand over time without affecting the global delay. Since the values of p must sum to 1, decreasing  $p_i$ , allows for increasing the percentage of the bus given to the tasks  $\tau$  that are on the critical path. Even though the decrease might be infinitesimal, this makes the critical path shorter, and thus  $\Delta$  is reduced. Consequently the smallest  $\Delta$  that satisfies the system of inequalities is achieved when every inequality is satisfied by equality. As an example, consider Figure 5.1b and note that  $\tau_5$  is an element in both sets  $D_3$  and  $D_4$  according to the definition in Section 5.2. This means that  $\tau_5$  is allowed to start first when both  $\tau_3$  and  $\tau_4$  have finished executing. Secondly, observe that  $\tau_5$  is on the critical path, thus being a direct contributor to the global delay. Therefore, to minimize the global delay, we must make  $\tau_5$ start as early as possible. In Figure 5.1b, the start time of  $\tau_5$  is defined by the finishing time of  $\tau_4$ , which also is on the critical path. However, since there is a block of slack space between  $\tau_3$  and  $\tau_5$ , we can reduce the execution time of  $\tau_2$  and thus make  $\tau_4$  finish earlier, by distributing more bus bandwidth to the corresponding processor. This will make the execution time of  $\tau_1$  longer (since it receives less bus bandwidth), but as long as  $\tau_3$  ends before  $\tau_4$ , the global delay will decrease. However, if  $\tau_3$  expands beyond the finishing point of  $\tau_4$ , the former will now be on the critical path instead. Consequently, making task  $\tau_3$  and  $\tau_4$  end at the same time, by distributing the bus bandwidth such that the sizes of

Figure 5.4 Calculation of new slot sizes

$\tau_1$  and  $\tau_2$  are adjusted properly, will result in the earliest possible start time of  $\tau_5$ , minimizing  $\Delta$ . In this case the inequalities corresponding to both  $\tau_1$  and  $\tau_2$  are satisfied by equality. Such a distribution is illustrated in Figure 5.1c.

The resulting system consists of n+1 equations and n+1 variables  $(p_1, \ldots, p_n \text{ and } \Delta)$ , meaning that it has exactly one solution, and even though it is nonlinear, it is simple to solve. Using the resulting distribution, a corresponding initial TDMA bus schedule is calculated by setting the slot sizes to values proportional to P.

#### 5.3.3 Generation of New Slot Size Candidates

One of the possible problems with the slot sizes defined as in Section 5.3.2 is the following: if one processor gets a very small share of the bus bandwidth, the slot sizes assigned to the other processors can become very large, possibly resulting in long wait times. By reducing the sizes of the larger slots while trying to keep their mutual proportions, this problem can be avoided.

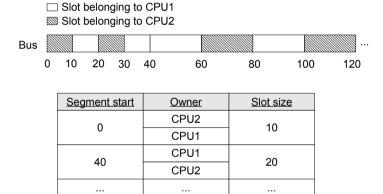

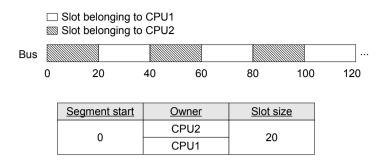

We illustrate the idea with an example. Consider a round consisting of three slots ordered as in Figure 5.4a. The slot sizes have been dimensioned according to a bus distribution  $P = \{0.49, 0.33, 0.18\}$ , calculated using the method in Section 5.3.2. The smallest slot, belonging to CPU 3, has been set to the minimum slot size k, and the remaining slot sizes are dimensioned proportionally  $^1$  as multiples of k. Consequently, the initial slot sizes become 3k, 2k and k. In order to generate the next set of candidate slot sizes, we define P' as the actual bus distribution of the generated round. Considering the actual slot sizes, the bus distribution becomes  $P' = \{0.50, 0.33, 0.17\}$ . Since very large slots assigned to a certain processor can introduce long wait times for tasks running

<sup>&</sup>lt;sup>1</sup>While slot sizes, in theory, do not have to be multiples of the minimum slot size k, in practice this is preferred as it avoids introducing unnecessary slack on the bus.

on other processors, we want to decrease the size of slots, but still keep close to the proportions defined by the bus distribution P. Consider once again Figure 5.4a. Since,  $p'_1 - p_1 > p'_2 - p_2 > p'_3 - p_3$ , we conclude that slot 1 has the maximum deviation from its supposed value. Hence, as illustrated in Figure 5.4b, the size of slot 1 is decreased one unit. This slot size configuration corresponds to a new actual distribution  $P' = \{0.40, 0.40, 0.20\}.$  Now  $p'_2 - p_2 > p'_3 - p_3 > p'_1 - p_1$ , hence the size of slot 2 is decreased one unit and the result is shown in Figure 5.4c. Note that in the next iteration,  $p'_3 - p_3 > p'_1 - p_1 > p'_2 - p_2$ , but since slot 3 cannot be further decreased, we recalculate both P and P', now excluding this slot. The resulting sets are  $P = \{0.60, 0.40\}$  and  $P' = \{0.67, 0.33\}$ , and hence slot 1 is decreased one unit. From now on, only slot 1 and 2 are considered, and the remaining procedure is carried out in exactly the same way as before. When this procedure is continued as above, all slot sizes will converge towards k which, of course, is not the desired result. Hence, after each iteration, the cost function (Equation 5.1) is evaluated and the process is continued only until no improvement is registered for a specified number  $\pi$  of iterations. The best ever slot sizes (with respect to the cost function) are, finally, selected. Accepting a number of steps without improvement makes it possible to escape certain local minima (in our experiments we use  $8 < \pi < 40$ , depending on the number of processors).

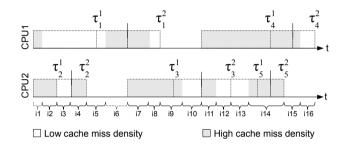

#### 5.3.4 Density Regions

A problem with the technique presented above is that it assumes that the cache misses are evenly distributed throughout the task. For most tasks, this is not the case in reality. A solution to this problem is to analyze the internal cache miss structure of the actual task and, accordingly, divide the worst case path into disjunct intervals, so called density regions. A density region is defined as an interval of the path where the distance between consecutive cache misses ( $\delta$  in Figure 5.3) does not differ more than a specified number. In this context, if we denote by  $\alpha$  the average time between two consecutive cache misses (inside a region), the density of a region is defined as  $\frac{1}{\alpha+1}$ . A region with high density, close to 1, has very frequent cache misses, while the opposite holds for a low-density region.

Consequently, in the beginning of the optimization loop, we identify the next density region for each task  $\tau_i \in \Psi$ . Now, instead of constructing a bus schedule with respect to each entire task  $\tau_i \in \Psi$ , only the interval  $[\theta..\Theta_i)$  is considered, with  $\Theta_i$  representing the end of the density region. We call this interval of the task a subtask since it will be treated as a task of its own. Figure 5.3b shows a task  $\tau_2$  with two density regions, the first one corresponding to the subtask  $\tau_2'$ . The tail of  $\tau_2'$  is calculated as  $\lambda_2' = \lambda_2'' + \lambda_2$ , with  $\lambda_2''$  being defined as the NWCET of  $\tau_2$  counting from  $\Theta_2$ . Furthermore, in this particular example  $m_2' = 3$  and  $l_2' = \delta_1' + \delta_2' + \delta_3' = 87$ .

Consider Figure 3.3 illustrating the overall approach. Analogous to the case where entire tasks are analyzed, when a bus schedule for the current bus segment has been decided,  $\theta'$  will be set to the finish time of the first subtask. Just as before, the entire procedure is then repeated for  $\theta = \theta'$ .

However, modifying the bus schedule can cause the worst-case control flow path to change. Therefore, the entire cache miss structure can be transformed during the optimization procedure (lines 4 and 5 in Figure 5.2), resulting in possible changes with respect to both subtask density and size. We solve this problem by using an iterative approach, adapting the bus schedule to possible changes of the subtask structure while making sure that the total cost is decreasing. This procedure will be described in the following paragraphs.

#### **Subtask Evaluation**

First, let us in this context define two different cost functions, both based on Equation 5.1. Let  $\tau_i^{'\rm end}$  be the end time of subtask  $\tau_i'$ , and define  $\tau^{'\rm end}$  as:

$$\tau'^{\text{end}} = \min_{\tau_i \in \Psi} (\tau_i'^{\text{end}}) \tag{5.6}$$

Furthermore, let NWCET $_i^{\tau'^{\rm end}}$  be the NWCET of the task  $\tau_i$ , counting from  $\tau'^{\rm end}$  to the end of the task. The *subtask cost*  $C'_{\Psi,\theta}$  can now be defined as:

$$C'_{\Psi,\theta} = \max_{\tau_i \in \Psi} (\tau'^{\text{end}} + \text{NWCET}_i^{\tau'^{\text{end}}} + \lambda_i)$$

(5.7)

Hence, the subtask cost is a straight-forward adaption of the cost function in Equation 5.1 to the concept of subtasks. Instead of using the worst-case execution time of the entire task, only the part corresponding to the first density region after time  $\theta$  is considered. The rest of

the task, from the end of the first density region to the end of the entire task, is accounted for in the tail, with respect to its corresponding NWCET.

In order to more accurately approximate how the subtask affects the worst-case global delay, we also introduce its complementary task cost  $C''_{\Psi,\theta}$  in addition to the subtask cost. Let WCET $_i^{\tau'^{\rm end}}$  be the worst-case execution time of task  $\tau_i$  starting from time  $\tau'^{\rm end}$ . We here assume that WCET $_i^{\tau'^{\rm end}}$  has been calculated with respect to a tailored bus segment, starting after  $\tau'^{\rm end}$ . The bus schedule representing this bus segment is calculated considering the cache miss structure of the corresponding part of the task, for instance by using the algorithm described in Section 5.3.2 for calculating initial slot sizes. This way we can approximate the transfer delays of the cache misses between  $\tau'^{\rm end}$  and the end of the task, instead of using the corresponding NWCET (as is done when calculating the subtask cost). The complementary task cost can be defined as:

$$C_{\Psi,\theta}^{"} = \max_{\tau_i \in \Psi} (\tau^{'\text{end}} + \text{WCET}_i^{\tau^{'\text{end}}} + \lambda_i)$$

(5.8)

Note that the only difference between this cost function and the previous one in Equation 5.7 is that we now use a calculated WCET for the remaining part of the task, instead of the NWCET. Consequently, the complementary task cost is always greater than or equal to the subtask cost. The problem with using the NWCET, as done when calculating the subtask cost, is that small subtasks tend to be favored. The complimentary cost is more precise, but also more time-consuming to calculate. Therefore the idea is to use it only when necessary.

With the two cost functions defined, we can formulate an algorithm for subtask evaluation, presented in Figure 5.5. In step 2, the tasks  $\tau_i \in \Psi$  are analyzed, in their entirety, in order to achieve an initial cache miss structure. This structure is then used to identify the first subtask  $\tau_i'$  of each task (step 3), and to calculate an initial bus schedule (step 4). In order to evaluate the bus schedule, the complementary cost is evaluated in step 5. In step 8, the bus schedule is modified with respect to the subtasks  $\tau_i$ . The algorithms, changing the slot sizes and order of the current TDMA round, used for these modifications can be found in Section 5.3.3 and Section 5.3.1. In step 9, the first corresponding subtask  $\tau_i'$  of each task  $\tau_i \in \Psi$  is reidentified with respect to the new cache miss structure, and an updated cost is calculated (by using the

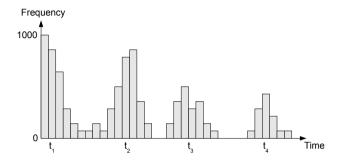

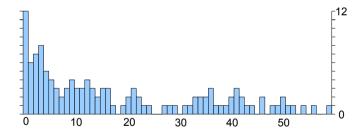

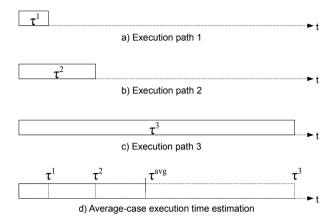

less expensive subtask cost function). If this cost is an improvement of the previous  $\text{cost}^2$ , we also evaluate the complementary  $\text{cost } C_{\Psi,\theta}''$ . If the new complementary cost is lower than the best  $\text{cost } C_{\text{inner}}^{\text{best}}$  found so far in the inner loop, we update  $C_{\text{inner}}^{\text{best}}$  to this new lowest cost.